文章目录

- 若干常用的时序逻辑电路

- 寄存器

- 移位寄存器

- 计数器

- 同步计数器

- 同步二进制计数器

- 同步二进制加法计数器

- 经典设计 74161

- 同步二进制减法计数器

- 同步二进制加减计数器

- 同步十进制计数器

- 异步计数器

- 二进制计数器

- 二进制加法计数器

- 二进制减法计数器

- 任意进制计数器的构成方法

- 当N>M

- 置零法

- 预置数法

- 当N<M

- 计数器应用实例

- 计数器+译码器----->顺序节拍脉冲发生器

- 计数器+数据选择器----->序列脉冲发生器

若干常用的时序逻辑电路

- 主要有两类:寄存器和计数器,没有组合电路那么丰富

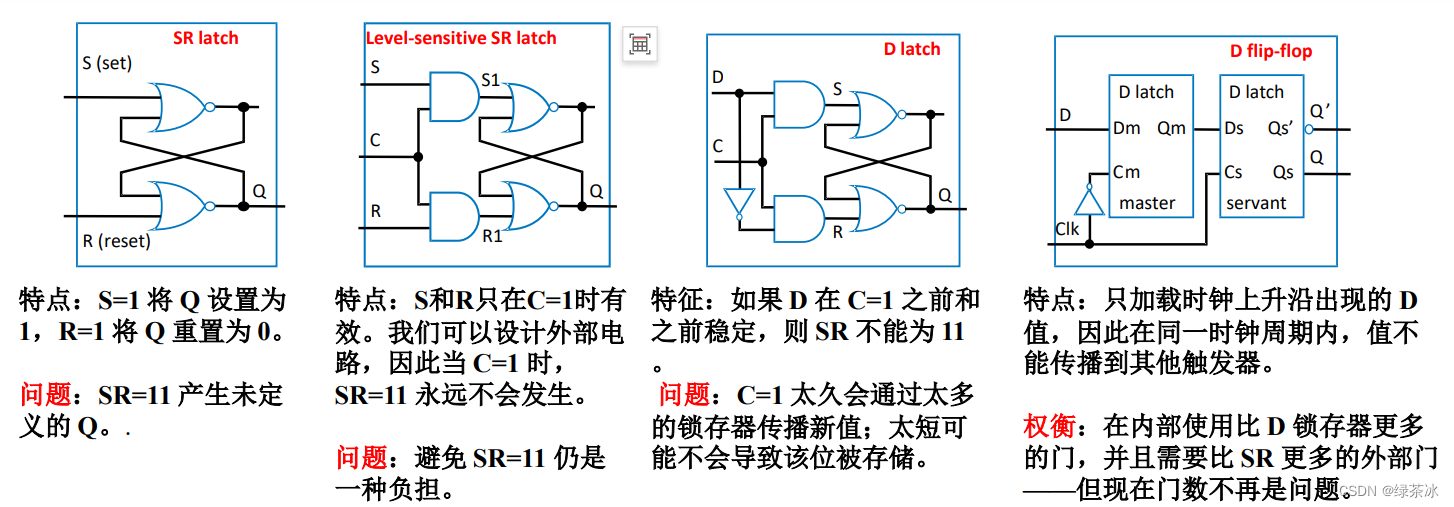

寄存器

- 用于寄存一组二进制代码,N位寄存器由N个触发器组成,可存放一组N位二进制代码

- 只要求其中每个触发器可置一置零

例:74HC175

(1)边沿触发

(2)提供了一个R端可以异步置零

移位寄存器

-

具有储存+移位功能

-

在二进制中,有时候移位就相当于运算,所以移位寄存器在数字电路中有相当重要的地位

-

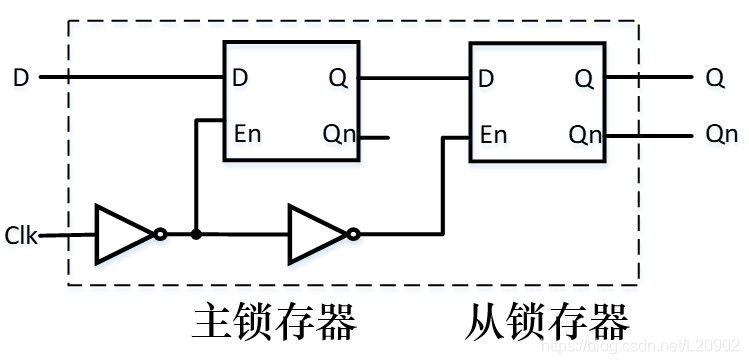

这个电路连接很简单,采用的都是边沿D触发器

-

数据从D1进来,一个节拍写道Q0,下一个节拍到Q1,以此类推

-

!因为触发器有Tpd和Tcd的存在,才使得这种写法能够稳定。Tpd的作用是数到达之后要经过多长时间才能写到下一级。想把数据稳定地写道第一个触发器FF0的话,数据和CLK应该有一个配合,早来建立时间,晚走保持时间。而相对于FF1来说,上一级来的数据也应该早来晚走。早来没有问题,只要触发边沿不到,Q0的值就是稳定值。晚走就要靠上一级的Tcd了。

-

!也就是说从左向右,第一级的Tcd要大于第二级的Thold,依此类推。

-

工作波形图如下:

-

!!!用在哪?优化上一篇文章的这个模型

-

接到出来的Si上,移位寄存器的长度决定了加法器可以做多少位

-

!问题1:上面的依位寄存器用的是D触发器,我可以换成其他触发器么?

-

结论:无论换成JK或RS都可以(功能上)

-

!问题2:功能换完了,可以换触发方式么?

-

电平触发不可以,如果换了,当触发信号到达时,一串都成直通得了,电平触发不存在节拍的概念,所以不能用作移位;主从结构的脉冲触发也可以

-

应用:

(1)代码转换,串—>并

(2)数据运算 -

!问题3:如果我想并变串怎么办?

-

目前的电路显然不符合要求,因为每一位的数据不能独立到达

-

要求:左/右移,并行输入,保持,异步置零等(还是四位)

-

设计原理:

(1)异步置零肯定要有异步信号接入端

(2)左移右移或并行输入或保持,都意味着每一位触发器的数据来源有多个方向。数据来源有多个,任何时候只搭在一个上-----数据选择器。每一位触发器的数据来源都需要加一个四选一的数据选择器,而这个数据选择器的地址端有两位,相当于多功能依位寄存器的功能控制端。要明确一点:这四个数据选择器要处在相同的功能下,所以可以直接把这两位接出来,当作整个模块的功能选择端。 -

通过设计原理再看这个电路就不是那么复杂了。

- 所有的触发器都选择了带有异步置零端的触发器(因为有这个需求),把异步置零端甩出来就是异步置零了

- 工作模式选择就对应着左移,右移,并行,保持这四个功能

- 四选一数据选择器

- 对FF1模块的构成进行分析:

(1)G2是个反相器,所以FF1看着是个SR,其实就是个D边沿触发器

(2)数据选择器四个数据来源:左1的最左边(从左来),左二的最右边(并行输入),右二的最右边(从右边来),右1的最右边(自保持)

(3)通过S1,S0就可以控制左移右移还是保持还是并行输入

(4)直接封装成模块,不再打开

- 看到这个模块

(1)CLK的三角:边沿触发

(2)S1,S0选择功能,左移,右移,并行输入,自保持

(3)Dir,Dil:左移右移的最原始数据来源 - 功能表

- 扩展应用(4位–>8位)

- 唯一一点就是确保左移右移数据不断,就是把Dil接到右边的Q0,把Q3接到右边的Dir

计数器

- 用于计数,分频,定时,产生节拍脉冲等

- 分类

(1)按时钟分:同步,异步

(2)按计数过程中数字增减分:加,减,可逆

(3)按计数器的数字编码分,二进制,二-十进制和循环码…

(4)按计数容量分:十进制,六十进制…

同步计数器

同步二进制计数器

分为加法和减法

同步二进制加法计数器

- 原理:多位二进制末位加一,若第i位以下皆为1时,则第i位应翻转

- 由此得出规律,若用T触发器构成计数器,则第i位触发器输入端Ti的逻辑式应为

- 也就是T0是恒等于1的,第i位的T取决于前面的Q相与,只要前面没记满,第i位就不会翻转

- 得到电路图

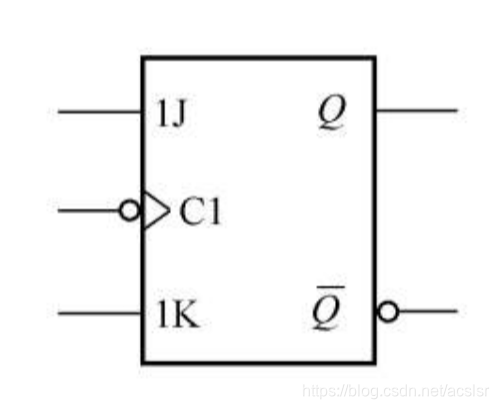

- !!T触发器没有一个现成的触发器,它是用我们学过的接出来的,最简单的是把J和K捏在一起构成了T触发器

- C是计位信号,有了这个信号就可以进行下一步的扩展,也可以不丢信息

经典设计 74161

- 这是一个常用的四位二进制计数器

- 通过读功能表,知道芯片怎么接

(1)CLK给上升沿

(2)Rd‘一定要接高电平,LD’一定要接高电平

(3)EP,ET一定要接高电平才可以计数

(4)由表格第一行,Rd‘是异步置零

(5)由表格第二行,当Rd’=1,LD’=0,CLK上升沿到达时,会把R0-R3写入Q0-Q3(预置数)

(6)由表格三四行,当EP和ET有一个是零的时候,保持。注意,在触发器中,说保持一定是保持的Q

- 内部电路

- 选的是带异步清零的JK触发器,这是异步清零端的来源,但是它并没有置一端,所以它的置数实际上不是通过异步来的,是通过JK触发器写进来的数。前面说过,JK触发器想要构成一个四位二进制计数的时候,可以把它构成一个T触发器来做。对着FF3来看,组成T触发器可以通过G19,也可以通过G14和G15,当用后者时,J和K就可以输入两个不一样的数,实现预置数

同步二进制减法计数器

- 原理:在多位二进制末位减一,若第i位一下皆为0,则第i位应该翻转

- 由此得出规律,若用T触发器构成计数器,则第i位触发器输入端Ti的逻辑式应为

- 也就是T0是恒等于1的,第i位的T取决于前面的Q’相与

- 构成等和加法类似

同步二进制加减计数器

- 两种方案

(1)来的脉冲是同一个脉冲源,和它配合的有另一个信号来表达这个脉冲是加还是减(码盘计数)

(2)加减计数是两个脉冲源(进出图书馆) - 最根本的是解决编码区分的问题

- 同一个计数器—容易出问题,除非物理背景让加两个信号不同时来。而两个脉冲源不会出现这个问题。

- 单时钟的方式

加/减脉冲用同一输入端,由控制线的高低电平决定加减,实例:74LS191

- U’/D是一个信号,等于0是加技术,等于0是减计数

- 功能表

(1)使能端S‘一定为0

(2)LD’是预置数,但是这里是异步的,也就是对CLK没有配合,一旦LD’等于0,直接写入预置数(所以这个里一定用的触发器原有的异步置零置一端)

- 双时钟的方式

实例:74LS193(采用T’触发器,即T=1)

- 加计数和减计数采用不同的时钟源

- 是一个假同步,因为所有的CLK并不是接在一起构成一个统一的时钟

- 实际上每一步的时钟受控于外面的CLK,但是加了个运算

- 最根本的使用,要有一个物理机制保证CLK(D)和CLK(U)不是同时来(这俩信号看芯片内部图),如果同时来,一定就会有竞争-冒险。

同步十进制计数器

-

问题:同步二进制计数如果是0-9没问题,如果再多了,可读性不是特别好,所以有同步十进制计数器

-

希望用二进制的结构实现十进制

-

问题:计数器的容量是多少?

-

容量就是10,所以如果要用二进制结构实现的话,4位二进制就是一个底,用它打基础,在它的基础上,我只用到它的十个(会造成浪费,但是可读性好)

-

有两件事需要做

(1)对电路进行改动,让1001的下个状态指向0000,让这之间的状态组成主循环圈

- 用0000对比之前1001的下个状态,1010。发现只有T1和T3的变化规则需要改

- 原来T3 = Q2Q1Q0,过去规则保存(因为在主循环圈的前面还要用到),而且要在Q3Q0时发生跳变。所以T3 = Q2Q1Q0 + Q3Q0

- 同理T1 = Q0Q3’

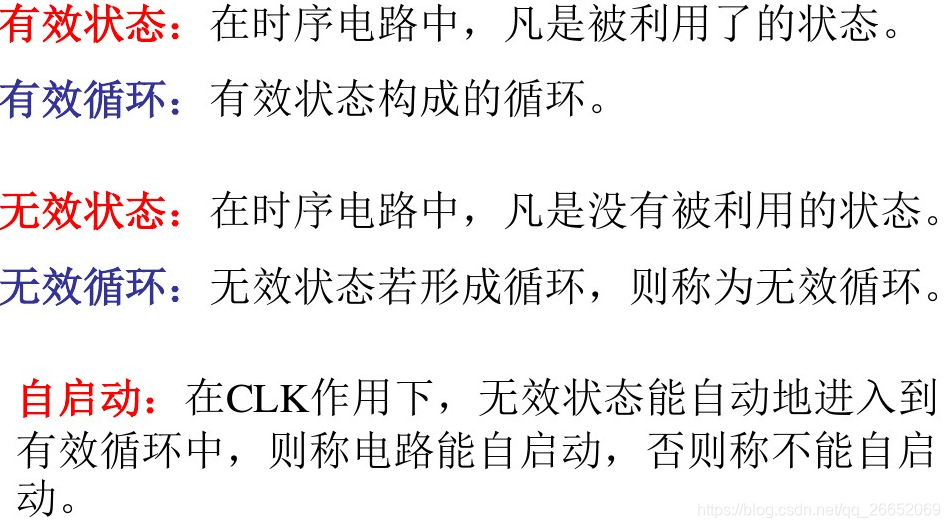

(2)剩余的项就成了无效态,要处理好无效态

- 问题:如果改成六进制,十二进制能改么?

- 可以

异步计数器

二进制计数器

二进制加法计数器

- 在末位+1时,从低位到高位逐位进位

- 原则:每一位从“1”变到“0”,向高位发出进位,使高位翻转

- 所有的J,K都接成1,那就意味着是T触发器,而且T恒等于1,所以见时钟就翻转

- Q0和CLK0就存在一个二分频的关系,Q1和Q0又是一个二分频,而且是Q0从1变0的时候翻转,也就是Q1计满了,天然的把自己作为一个进位给了下一位

- 时序图如下

- 在波形图当中,Q0的变化是以CLK0作为基准点,也就是CLK0的下降沿到达之后,Q0发生翻转。Q1的基准点是Q0,Q2的基准点是Q1

- 所以Q0的Tpd一定小于Q1的Tpd,Q1的Tpd一定小于Q2的Tpd,而且随着位数增加,Tpd会越来越大

- 也就是在Q3的Tpd之内,会出现一个我不希望的组合,这个给到下面的组合电路就会出现竞争-冒险,这也是异步电路我们不喜欢的地方

二进制减法计数器

把加法C前面的圈抹去

任意进制计数器的构成方法

用已有的N进制芯片,组成M进制的计数器,是常用的方法

- 两种可能

(1)N>M

(2)N<M

当N>M

- 异步置零法,同步置零法(每次计数的初态都以000开始)

- 异步预置数法,同步预置数法(只要状态数够,满足我进制需要就可以i,不必000开始)

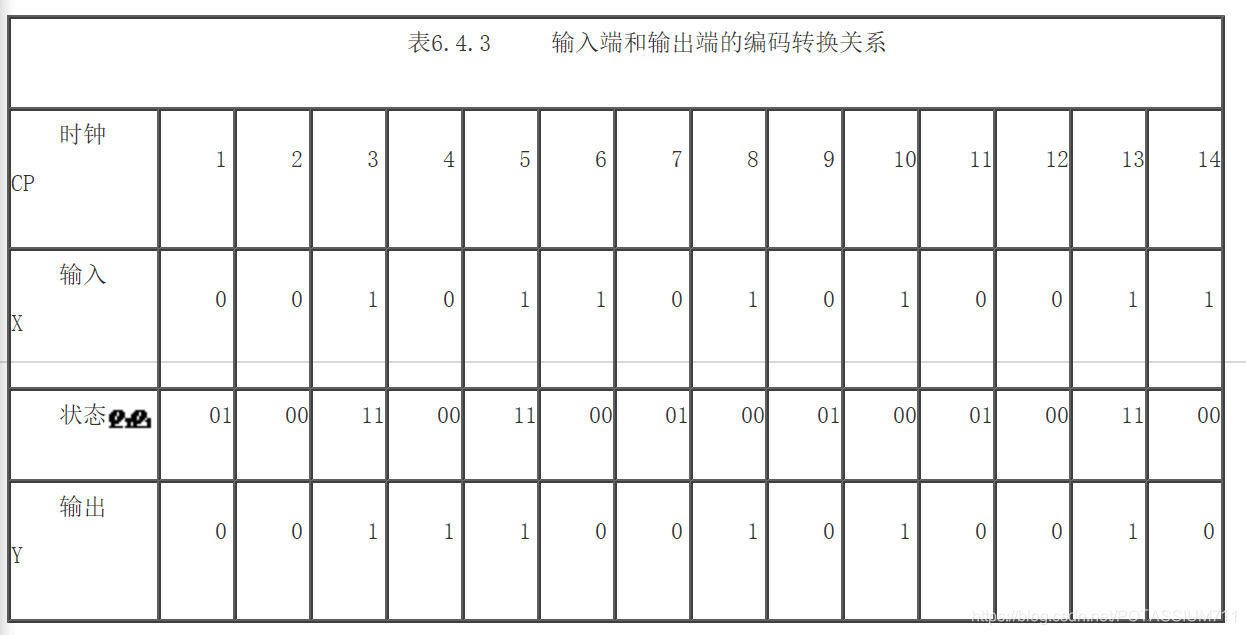

例:用十进制的74160接成六进制计数器

- 可以置零也可以预置数。

- 异步和同步的区别:异步如果置零信号来了,马上就置零,同步要等上升沿

置零法

-

!!如果用置零法:应该在计数到5的时候跳回0。如果用异步置零会有一个问题,第六个状态只会持续74160整个芯片的Tpd,但是前五个状态会持续一个CLK,也就是说,如果用异步置零,需要用0110,这个0110就成了一个暂态,它的出现就是为了回到0000

-

实际的状态转换图如下(注意两个虚线)

注意:只有1001,1000,0111是你十进制改六进制造成的无效态,其他的无效态是这个芯片16进制改10进制造成的 -

芯片引脚图

-

!!引出了进位信号,表达了你这个计数器是可以扩展的

-

建议不要单独画进位信号,就用跳转的信号当作进位信号是最理想的,因为跳转了就证明计满了

-

问题1:如果像上图那样引出进位信号在0100就出了进位信号,这个进位信号会持续0100和0101两个CLK长,是一个很长的高电平(能这么引的原因是,如果后面电路认下降沿就可以用,如果认上升沿就取反还可以用,原理是只要一个周期里只有一个进位信号就能用,但是不建议这么引)

-

问题2:在这个电路中,这么引会有问题,Rd’平时一直是1,只有Rd’=0才让他清零,清完零又回去了,这个信号会出现一个电平,但是大概就是传输延迟时间级别的,太短,如果用Rd’作为进位信号可能会被认为是竞争-冒险带来的毛刺,用个滤波电容就滤掉了

-

改进上面的电路

-

接了一个基本的RS锁存器,G2是Sd’,G3是Rd‘,Sd’=0的时候进位输出置一,如果想清零的话,必须让Rd’=0,而Rd‘接在了CLK上。

-

芯片是上升沿工作的,也就是写进位的时候Rd’=1,所以写入的信号会一直保持,直到CLK变到0

预置数法

- 这时候,我们译的是0101,因为LD是同步信号,所以得等到下一个CLK到达的时候,才能把数置进去,所以这时候0101这个状态就能呆一个时钟了

- 所以如果用置零法的话建议用同步的方法,置入0000

- 方案不唯一,可以用各种方法,甚至可以用1111,只要在0110的时候置数跳回1111就可以

- 书上给的例子是在74160有效循环圈里面最大的一个

- 同理,置1001,保证自己的有效循环圈即可

- 所以,有效循环的个数就是进制,两个点的连接,一个作为译码,还有一个作为置数

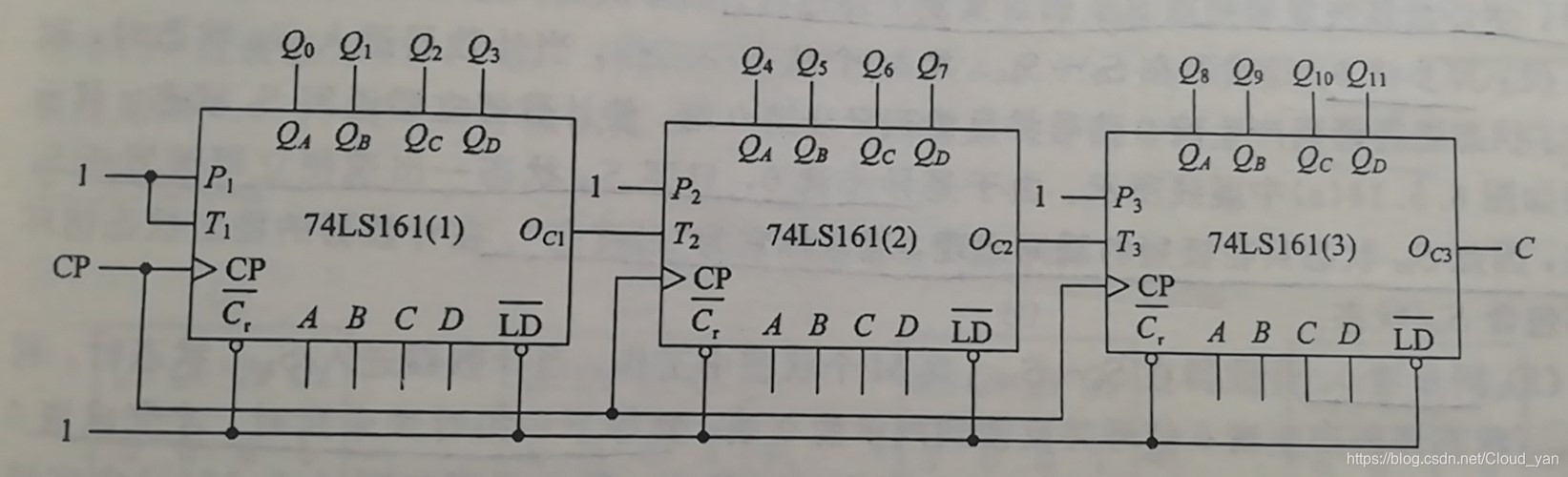

当N<M

- 方法一:分解

- M = N1 * N2

- 先用前面的方法分别接成N1和N2两个计数器

- N1和N2有两种连接方式

(1)并行进位:用同一个CLK。低位片的进位输出作为高位片的计数控制信号

(2)串行进位:低位片的进位输出作为高位片的CLK,两片始终处于计数状态

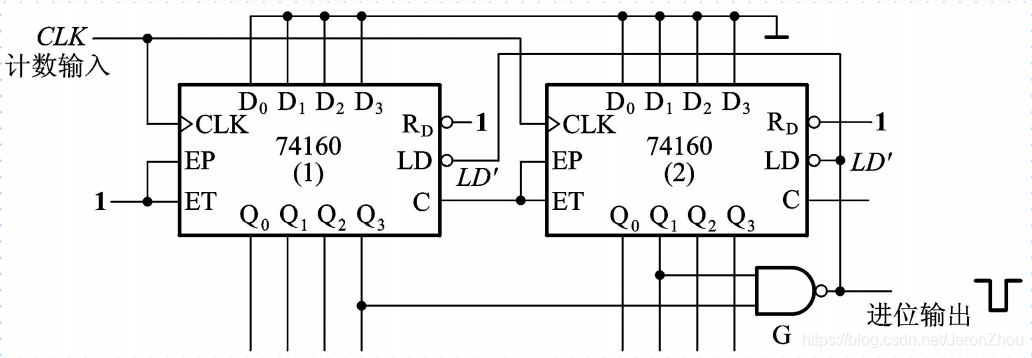

例:用74160接成100进制

只有EP,ET同为1时才允许进位,所以直接把前面的进位信号接到EP,ET上就可以了

- 问题:串行进位为什么接反相器?

- 前面那个的C是记到1001的时候会有一个高电平,如果不加反相器,那前面是9的时候,后面就加一了,也就是显示的话是1,2,3,4,5,6,7,8,19,10,11…

- 方法二:M不可分解

- 采用整体置零和整体置数法

- 先用两片接成M’ > M的计数器,然后采用置零或置数的方法

例:用74160接成29进制

- 整体异步置零:找出29,图上不是全译码,找了2和9的第一次出现方式,实验中可以这么做,但是实际中尽量使用全译码

- 整体同步置数:一出现28就回去

计数器应用实例

计数器+译码器----->顺序节拍脉冲发生器

- 把一个计数器和38译码器放在一起

- 前端是74161,而且Rd‘和LD都接了高电平,EP,ET接1,CLK给了一个始终,所以74161一直在16位计数循环,16个状态一直在跑

- 138取了它的低位,那么138的输出,每个CLK这些都会出现一个低电平,而且在循环跑,CLK是高电平的时候不工作,低电平的时候才工作,所以是CLK的后半段工作,前半段没工作

- 电路工作起来会相当稳定,因为前面发生变化的时候后面不变,把时间错开了

- 这个电路如果和前面三态总线的电路接在一起,总线就构成了循检的方式

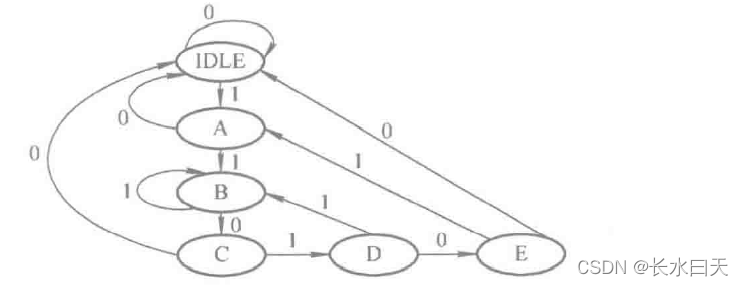

计数器+数据选择器----->序列脉冲发生器

- 152是八选一的数据选择器

- 当CLK不断进来,161循环计数,Y’就得到不断循环的脉冲序列00010111