第六章 时序逻辑电路

文章目录

- 第六章 时序逻辑电路

- 6.1 概述

- 6.1.1 时序逻辑电路的特点

- 6.1.2 时序电路的一般结构形式与功能描述方法

- 6.1.3 时序电路的分类

- 6.2 时序电路的分析方法

- 6.2.1 同步时序电路的分析方法

- 6.2.2 时序电路的状态转换表、状态转换图和时序图

- 6.3 若干常用的时序逻辑电路

- 6.3.1 寄存器和移位寄存器

- 6.3.2 计数器

6.1 概述

6.1.1 时序逻辑电路的特点

功能上:任一时刻的输出不仅取决于该时刻的输入,还与电路原来的状态有关。(这里是考虑到延迟了的)

电路结构上

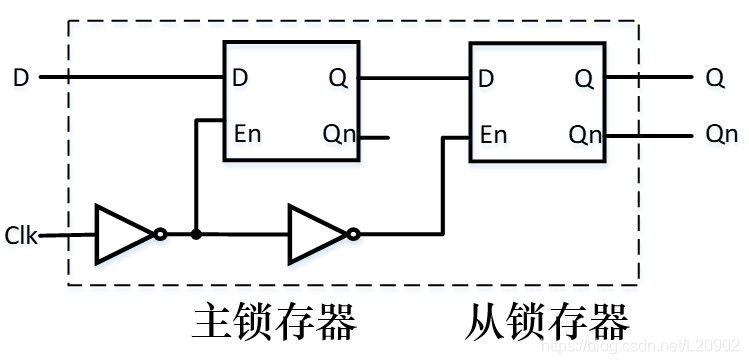

①包含存储电路和组合电路,存储电路必不可少

②存储电路输出状态必须反馈到组合电路输入端,和输入变量共同决定输出

在该图中,加法器逐位输入,结果也逐位输出。进位状态反馈到输入端,与输入变量共同决定输出。

6.1.2 时序电路的一般结构形式与功能描述方法

可用三个方程组来描述:

1、输出方程(输出和输入的关系)

2、驱动(激励)方程(存储电路的输入)

3、状态方程(存储电路输出和输入、现态的关系)

q:现态; q*:次态

6.1.3 时序电路的分类

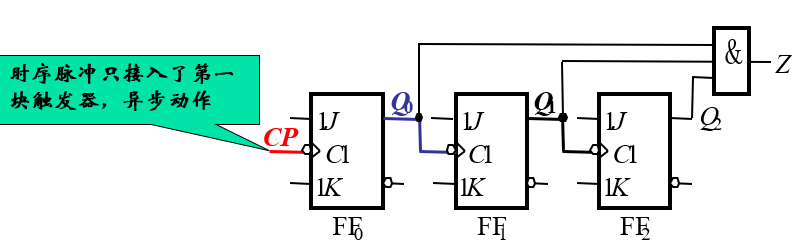

- 同步时序电路与异步时序电路

同步:存储电路中所有触发器的时钟使用统一的clk,状态变化发生在同一时刻

异步:没有统一的clk, 触发器状态的变化有先有后

- 米利(Mealy)型和穆尔(Moore)型

X是输入,Q是存储电路的输出

X是输入,Q是存储电路的输出

6.2 时序电路的分析方法

6.2.1 同步时序电路的分析方法

分析:找出给定时序电路的逻辑功能,即找出在输入和CLK作用下,电路的次态和输出。

一般步骤:

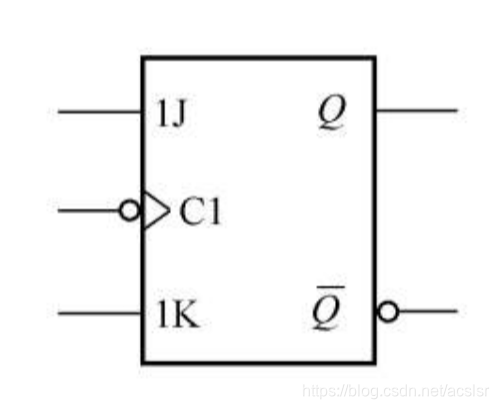

①从给定电路写出存储电路中每个触发器的驱动方程(输入的逻辑式),得到整个电路的驱动方程。

②将驱动方程代入触发器的特性方程,得到状态方程。

③从给定电路写出输出方程。

例:

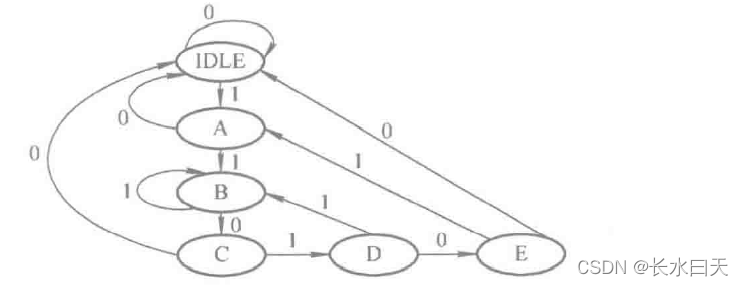

6.2.2 时序电路的状态转换表、状态转换图和时序图

一、状态转换表

已知初始状态,就可以通过初始状态的次态明白CLK=1时的状态和Y的状态。故以此递推,直到再回到初始状态为止。

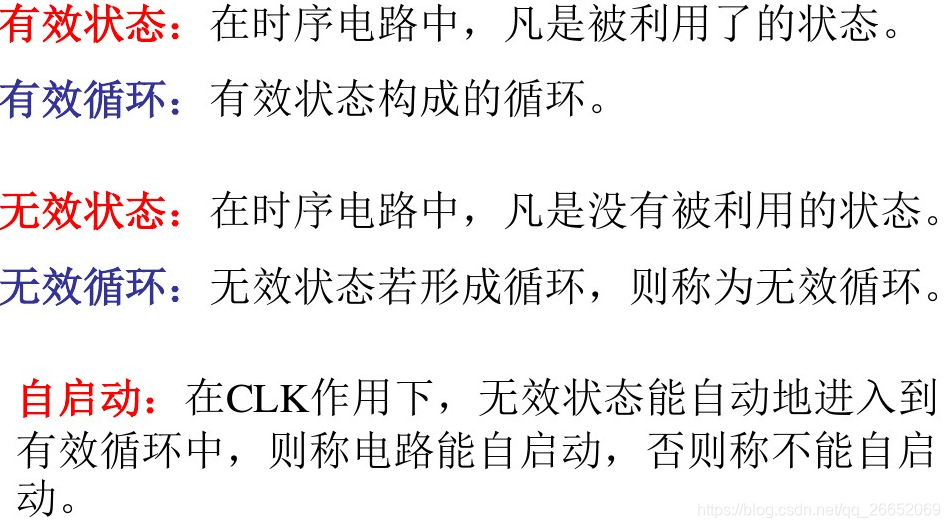

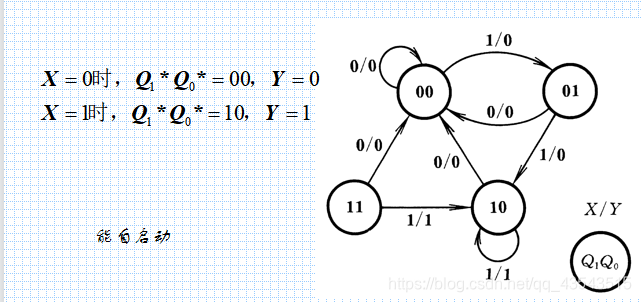

二、状态转换图

根据观察,此为七进制计数器。Y是进位脉冲。

自启动判断:任意给定一个初始状态,都能进入到主循环中去。即每个状态都必须与主循环的某个状态相联系

三、时序图

例6.2.3

1.驱动方程:

2.状态方程:

特性方程: Q*=D

3.输出方程:

4.状态转换表、状态转换图

因此可知,此为可控四进制计数器:当A=0时为加法计数器,A=1时为减法计数器

5.时序图

6.3 若干常用的时序逻辑电路

6.3.1 寄存器和移位寄存器

一、寄存器

①用于寄存一组二值代码,N位寄存器由N个触发器组成,可存放一组N位二值代码。

②只要求其中每个触发器可置1,置0。触发方式无要求。

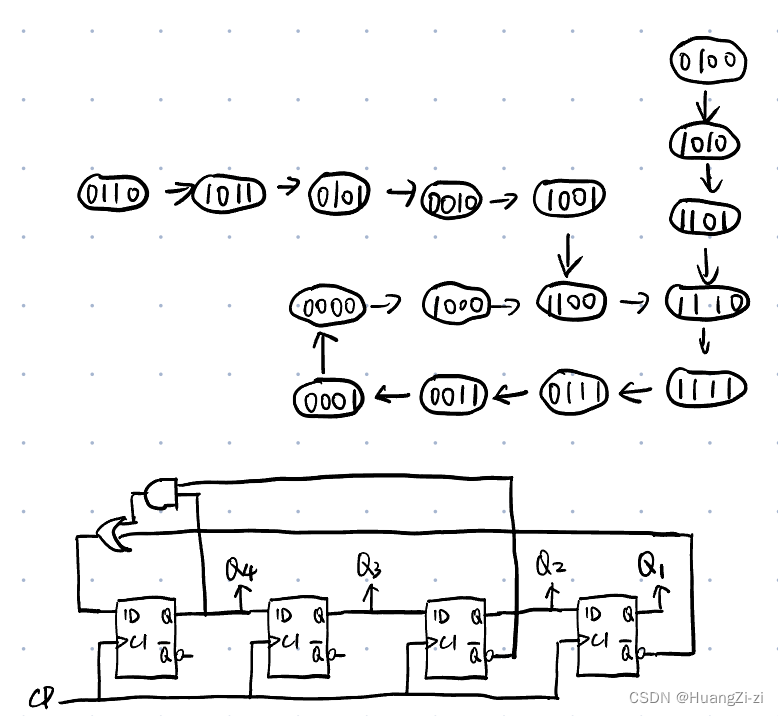

二、移位寄存器

具有存储 + 移位功能

存储的代码可在移位脉动作用下左移或右移

比如:需要移位时,就打开开关,需要右移几位就打开多久的开关。

左移时,是从右向左传递数据;右移时,是从左向右传递数据。

6.3.2 计数器

用于计数、分频、定时、产生节拍脉冲等

分类:

- 按时钟分,同步、异步

- 按计数过程中数字增减分,加、减和可逆

- 按计数器中的数字编码分,二进制、二-十进制和循环码…

- 按计数容量分,十进制,六十进制…

一、同步计数器

1.同步二进制计数器

①同步二进制加法计数器

原理:根据二进制加法运算规则可知:在多位二进制数末位加1,若第i位以下皆为1时,则第i位应翻转。

末尾是必须反转的

C在这里是一个进位输出。

可见,从 Q 0 Q_0 Q0到 Q 3 Q_3 Q3的周期都加倍了,~~我愿称之为超级加倍!~~频率以此减半,因此有分频功能,这种计数器也可称为分频器。

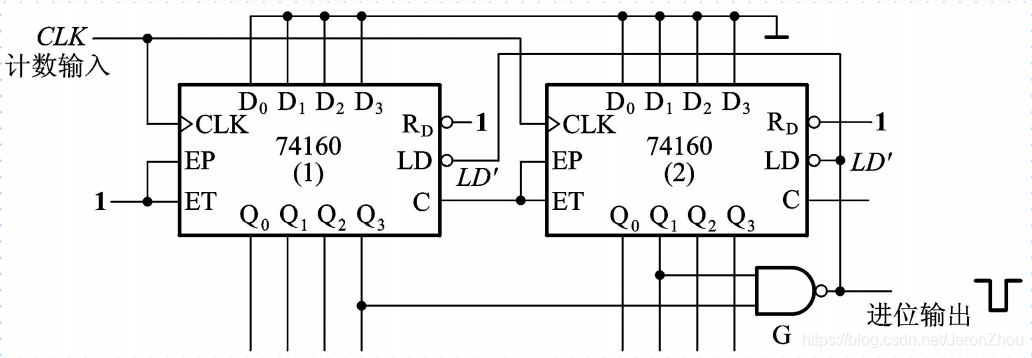

74161为集成了该功能的同步十六进制计数器

②同步二进制减法计数器

原理:根据二进制减法运算规则可知:在多位二进制数末位减1,若第i位以下皆为0时,则第i位应翻转。

可以与加法计数器进行类比

③同步加减计数器

a.单时钟方式

b.双时钟方式

加法、减法计数脉冲来自两个不同的脉冲源,时间上应错开

- 同步十进制计数器

①加法计数器

基本原理:在四位二进制计数器基础上修改,当计到1001(9)时,则下一个CLK电路状态回到0000(0) (而不是1010)

设计思路即根据真值表,求出表达式即可。

器件实例:74160

②减法计数器

基本原理: 对二进制减法计数器进行修改,在0000时减“1”后跳变为1001,然后按二进制减法计数就行了。

~~就是同理可得嘛~