🎨🎨欢迎大家来学习数字电路——时序逻辑电路。

🎨🎨在这里我们会讲解数码寄存器、移位寄存器、单向移位寄存器和集成双向移位寄存器74LS194,希望通过我们的学习会让你更明白数字电路中的奥秘。

目录

🎨一、寄存器

🏆1.数码寄存器

(1)电路组成

(2)工作过程

(3)对于数码寄存器的分析

🏆2.移位寄存器

(1)单向移位寄存器

①电路组成

②工作过程

(2)集成双向移位寄存器

①74LS194芯片的实物和引脚排列

②74LS194芯片的逻辑功能

一、寄存器

在数字电路中,常需要将数据或运算结果暂时存放起来。能够暂时存放二进制数据的电路称为寄存器。它由具有记忆功能的触发器和门电路构成。一个触发器只有0和1两个状态,只能存储1位二级制代码,n个触发器可以构成能存储n位二进制的寄存器。在时钟脉冲CP控制下,寄存器接收输入的二进制数码并存储起来。按照功能的不同,寄存器可分为数码寄存器和移位寄存器。

1.数码寄存器

数码寄存器具有接收、存储和清除原有数据的功能。

(1)电路组成

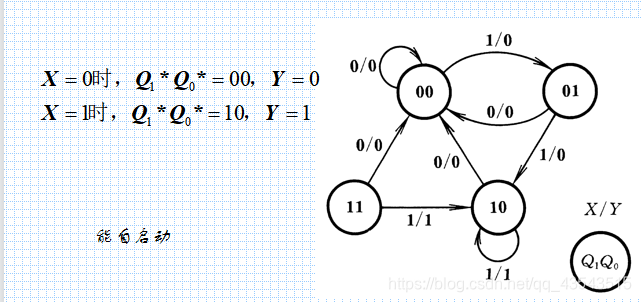

如图所示是一个由基本RS触发器和门电路组成的4位数码寄存器的逻辑电路图。4个RS触发器的复位端连接在一起,作为寄存器的清零端,

为寄存器的数据输入端,

是数据的输出端。

(2)工作过程

寄存器的工作分两步进行:

①寄存器前先清零

在接收数据前先在复位端加一个负脉冲(清零脉冲),把所有触发器置0,清零脉冲恢复高电平后,为接收数据做好准备。

②接收脉冲控制数据寄存

接收脉冲CP(正脉冲)到来,将与非门G0~G3打开,接收输入数码。例如,若

=1101,则G3、G2、G1、G0输出为0010,各触发器被置成1101,即

=1101,完成接收和寄存工作。

可以看出,上述寄存器在工作时,同时输入各位数码,并同时输出各位数码

,这种数码输入、输出方式为并行输入、并行输出方式。

(3)对于数码寄存器的分析

优点:存储时间短、速度快。

缺点:停电后,所存储的数码便全部丢失。

2.移位寄存器

移位寄存器不仅能寄存数码,还具有移位功能。移位是指在移位脉冲的控制下,触发器向左或向右的相邻位依次转移数码的处理方式。

移位寄存器分为单向移位寄存器和双向移位寄存器。

(1)单向移位寄存器

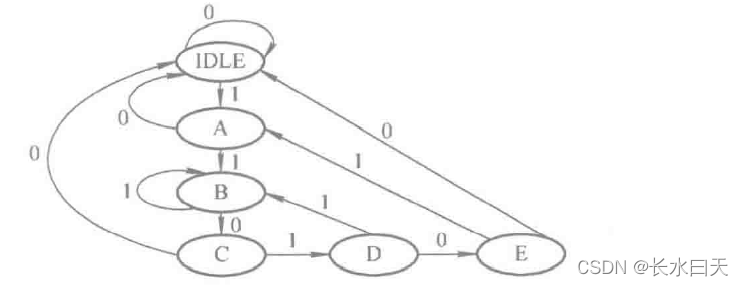

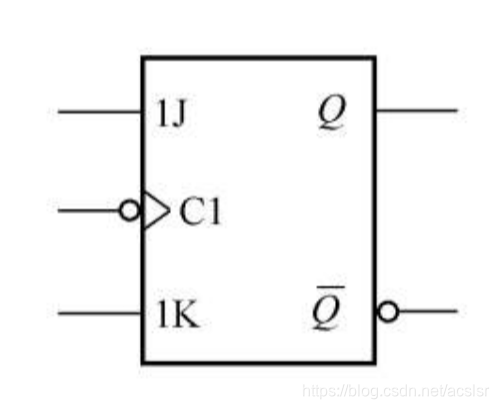

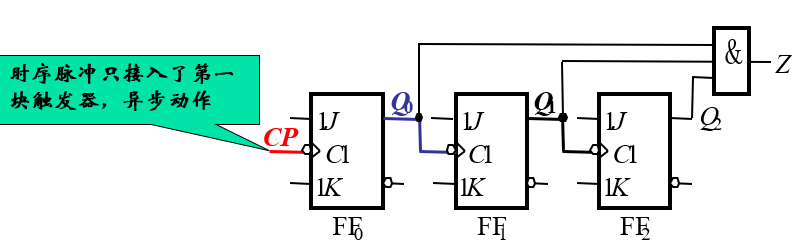

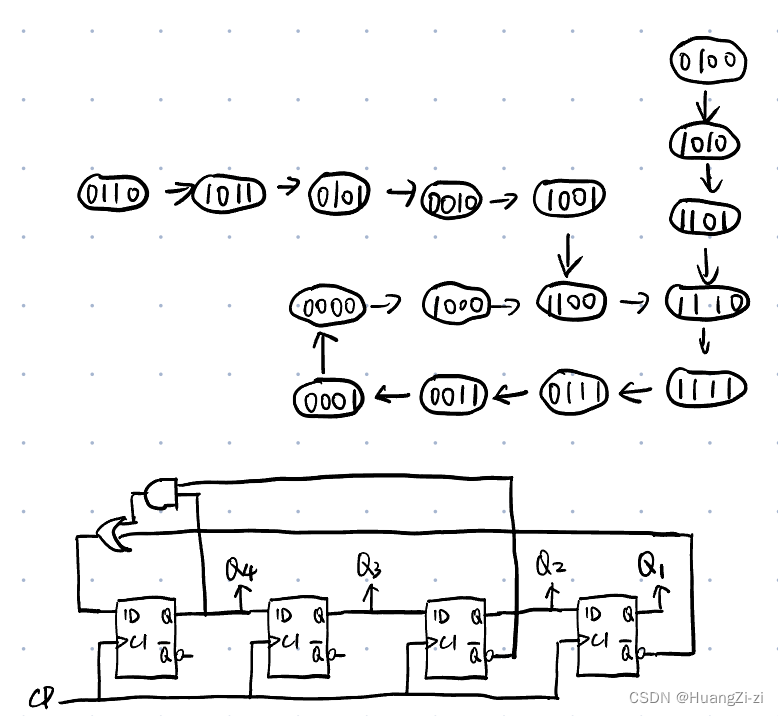

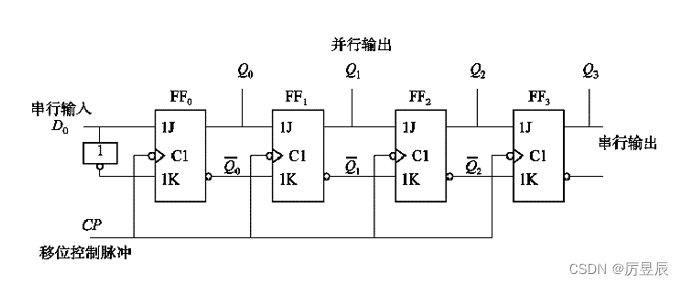

①电路组成

如图所示为由JK触发器构成的4位单向右移寄存器。图中各触发器的J、K端均与相邻低位触发器的、

端连接,左边最低位的JK触发器FF0的K端串接一个非门后再与J端相连,作为接收外来数据的输入端,各个JK触发器的J与K总是处于相反状态,使JK触发器只具有置0和置1的功能。移位控制信号同时加到各触发器的CP端。

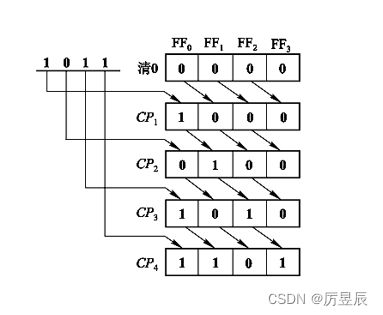

②工作过程

在CP下降沿作用下,待存数码送到FF0,其他各触发器的状态与CP作用前一瞬间低1位触发器的状态相同,即寄存器中的原有数码一次右移1位。

下面以存入数码1011为例,分析 4位右移寄存器的工作过程,要寄存数码=1011,一般先对寄存器 清0,然后将被存放数码从高位到低位 按移位脉冲节拍依次送到

端,当第 一个CP上升沿到来时

=1,则

=0001;当第二个CP上升沿到来时,

=0,

=0010,经过四个移位脉冲后寄存器状态为

=1011。如图所示:

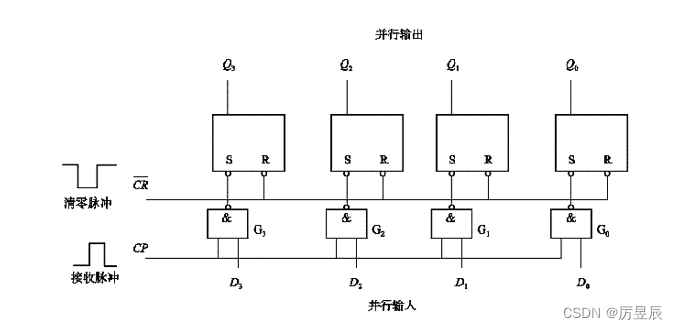

(2)集成双向移位寄存器

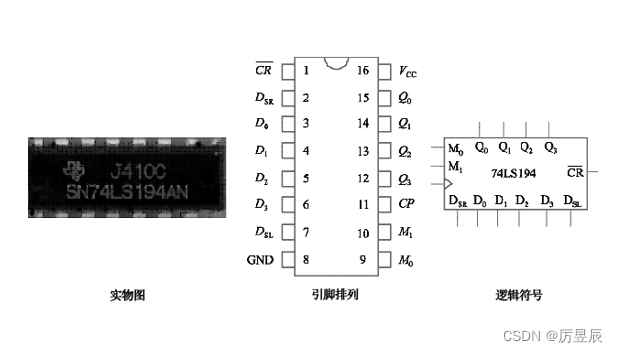

①74LS194芯片的实物和引脚排列

如图所示为74LS194芯片实物与其引脚排列:

是并行数据输入端;

是右移串行数据输入端,

是左移串行数据输入端。

是寄存器并行数据输出端。

和

是双向移位寄存器的控制端。

②74LS194芯片的逻辑功能

如图所示:

由表可知,74LS194芯片具有如下逻辑功能:

保持功能:当=

=0时,无论有无CP 作用时,寄存器中内容不变。

并行置数功能:当 =

=1时,在CP上升沿作用时,将数据输入端的数码并行送到寄存器中,使

=

。

右移功能:当=0、

=1 时,在移位控制信号CP上升沿作用时,寄存器中数码依次右移一位,且将

送到

。

左移功能:当=1、

=0 时,在CP上升沿作用时,寄存器中数码依次左移一位,且将

送到

。

异步清零功能:当=0时,直接清零,寄存器各位(

)均为0,不能进行置数和移位。只有当

=1时,寄存器允许工作。

下篇文章继续讲解计数器🥰🥰