文章目录

- 时序逻辑电路的设计方法

- 同步时序逻辑电路的设计方法

- 一般步骤

- 改进步骤

- 例:蚂蚁走迷宫

- 背景

- 分析

- 继续编码状态,然后写出状态图,然后卡诺图化简,得到方程

- 设计总结

时序逻辑电路的设计方法

同步时序逻辑电路的设计方法

一般步骤

一、逻辑抽象

- 确定输入/输出变量,电路状态数

- 定义输入/输出逻辑状态以及每个电路状态的含义,并对电路状态进行编号

- 按设计要求列出状态转换表,或画出状态转换图

二、状态化简

- 原则:若两个状态在相同的输入下有相同的输出,并转换到同一个次态,则称为等价状态;等价状态可以合并

三、状态分配

- 确定触发器数目

- 给每一个状态规定一个代码

(通常编码的取法、排列顺序都按照一定的规律)

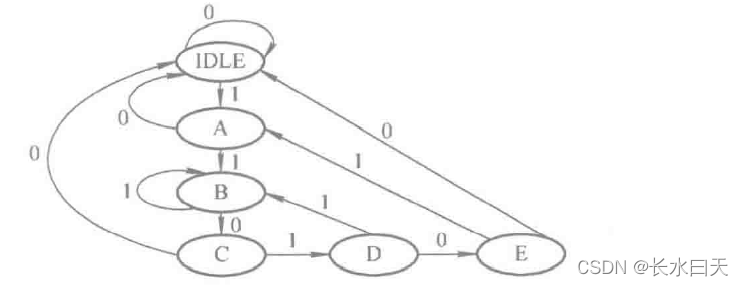

四、确定触发器类型

- 求出状态方程,驱动方程,输出方程

五、画出逻辑图

六、检查自启动

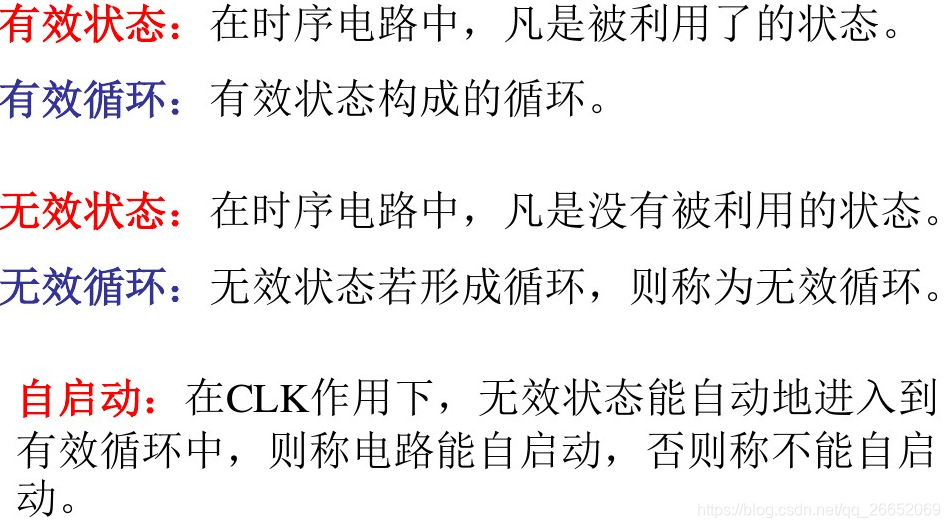

- 在设计的时候,我们一直要关注的是有限状态机,也就是状态图。在有效状态机中,会定义初态,输入,输出

- 转换的时候有两个可选Mealy和Moore

- !还是有一定规律可言,在设计的时候首先要学会这种有规律的方法,通过这种有规律的方法先去设计一个对的电路,然后再去求电路的好,再去求电路的巧

- !在规律性的东西里面,第一步,逻辑抽象是最重要的,因为在这一步,可以把一个实际问题转换成与状态转换图挂钩,然后再去谈如何实现的问题

例:设计一个数字密码锁

-

关心:

(1)输入是什么,是不是跟他相吻合

(2)如果没有enter键,输对了就开

(3)如果有enter键,串行移位,点enter判断输入是否正确,输入是并行的四位数 -

在设计的时候一定要明确需求,specification,要不然可能会导致设计产生歧义

-

先设计一个最简单的密码锁:

-

分析要求:顺序输入3个或3个以上“1”时,锁打开

(1)顺序输入,锁打开。意味着输入是移位进去的,因此输入变量的个数就是一个,而输出变量的个数也是一个,就是锁打开

(2)下一步要做的就是把锁打开和关闭和输入之间挂上联系

(3)做组合肯定不行,因为如果是组合的话要么就是同向要么就是反向,没有办法记忆我输入了几个“1”,所以这个电路一定是一个时序电路 -

设计

一、抽象画出状态图

Mealy和Moore都可以,这次先设计一个Mealy型的电路(电路在这个状态之下,如果有一个什么输入,来决定它的输出)

用X(1位)表示输入数据,用Y(1位)表示输出(密码是否相符)

二、状态化简(为了减小电路规模,减少触发器个数)

(1)定义:如果两个状态在相同的输入下有相同的次态和输出,那么这两个状态就是等价状态

(2)S2和S3是等价状态,可以合并

三、状态分配

选两个触发器,取n=2,令Q1Q0的00,01,10为S0,S1,S2,则

- 中间是x是因为没有使用,所以设计之初就把它列为无关项

- 这个表长得很像卡诺图,我们可以把它拆分成三个卡诺图

- 对卡诺图进行化简

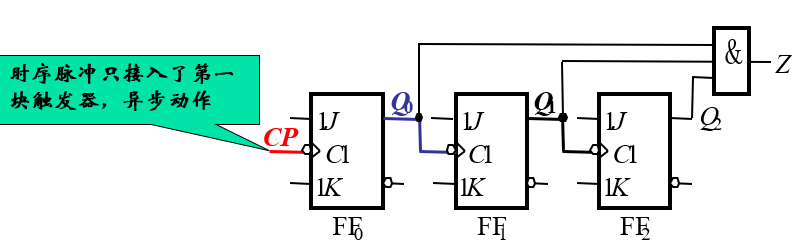

- 但是有一个问题。从电路连接中,能直接写出来的两种方程是驱动方程和连接方程,状态方程是不能直接写出来的,需要确定选用的触发器才能定下来,所以下一步需要选择触发器

四、选用JK触发器,求方程组

也就是可以得到J和K

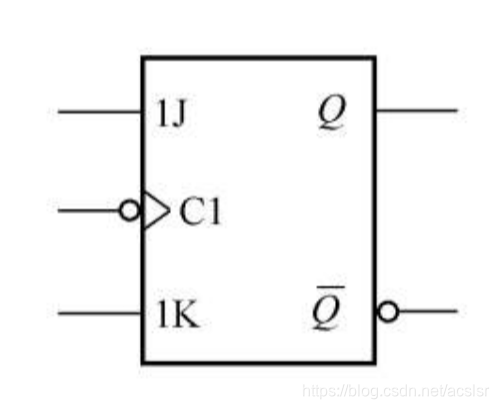

五、画逻辑图

六、检查电路的自启动

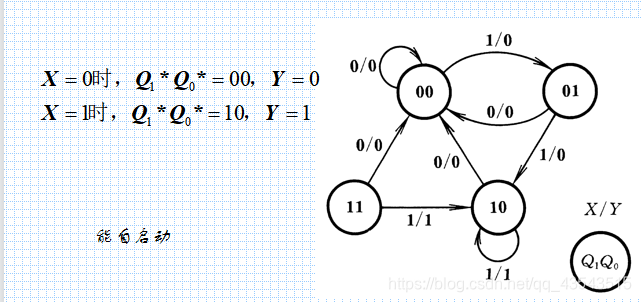

- 将状态“11”代入状态方程和输出方程,分别求X=0/1下的次态和现态的输出

- 得到:X = 0时,Q1Q0 = 00,Y = 0;X =1时,Q1Q0 = 10,Y = 1

- 所以能自启动

- 画出状态转换图

- 但是这这个设计中,如果一上电在11的状态,输入一个1,锁就打开了,这个设计其实不好

改进步骤

-

!!我们可以在设计时把检查自启动挪到前面

-

在第三步状态分配时,我们直接把x去掉,并不需要用这点化简来省那点电路,省完了还出问题

-

做设计的时候在下面人为的就填0

-

人为的填0有一个坏处就是电路不能化简,但是电路化简和整个电路的设计来讲,我们更倾向于不要去化那点简,因为化简只是改变驱动方程的复杂程度

-

建议设计的时候,把所有无效态的下一个状态都回到初态,放弃化简,没必要化简

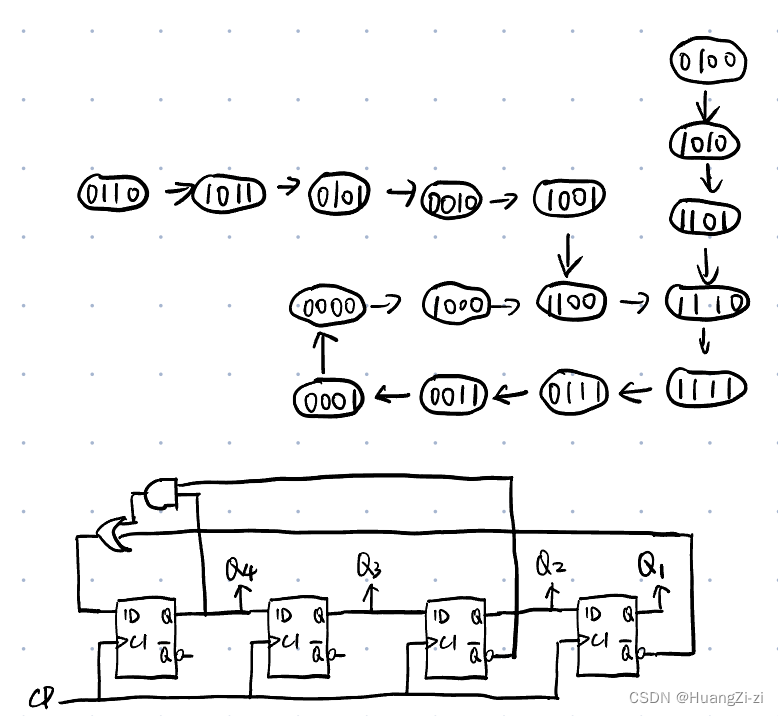

例:蚂蚁走迷宫

背景

- 两个触角为两个传感器,腿为执行机构

- 从迷宫任意一点走到出口(出口在墙上,不是孤岛)

分析

- 可以用摸着墙走的策略,右触角碰墙

- 从初态开始:蚂蚁可以在迷宫的任意部位,最艰难的时候就是两个触角都没碰到墙,这时给的指令就是一直往前走(状态1)直到撞到墙(状态2)

- 撞到墙可能有三种情况:右触角碰墙,左触角碰墙,两个触角都碰墙,但是无论是哪种情况,我们就左转,因为我们的策略是右触角碰墙

- 一直左转到两个触角都不碰墙,赶紧停下来,然后一直往前走(状态3)

- 这时候需要一边往前走一边向右稍微转一点确认墙就在我边上。如果在,就转回来继续走(状态4),重复这个边走边确认的过程。

- 如果向右确认的时候发现墙不在右边,说明遇到了拐角(状态5),这时接着右转,一定要边往前走边右转,如果原地转就出不来了

- 得到状态转换图

- 在这个设计中,压缩合并是有意义的,因为五个状态如果不压缩需要用三个触发器,如果能压缩一个就可以减少一个触发器

- 压缩后的状态转换图

继续编码状态,然后写出状态图,然后卡诺图化简,得到方程

- 最终的内部电路其实就这样

设计总结

- 在设计的时候首先要搞清楚你的输入和输出

- 电路的状态是根据你的策略,你的需要而定