一、实验目的

1、掌握时序逻辑电路的设计方法;

2、掌握基于 QuartusII 集成开发环境的时序逻辑电路设计流程;

3、熟练掌握VerilogHDL语言;

4、熟练掌握 DE2-115 开发板的使用方法;

二、实验任务及要求

1.任务一:计数器设计与仿真

设计一个模 200 的二进制加法计数器并在 quartusII5.1 中仿真。

2.任务二:分频器设计与仿真

设计并实现偶数分频器,对开发板上的 50Mhz 时钟分频,得到一个5MHz 的时钟。

3.任务三:实现一个带有闪烁功能的共阳极七段数码管的显示译码控制电路(在 1 个数码管上动态循环显示 0~F,每个数字显示时间为 1s)

三、实验原理与步骤

任务一

(1) 步骤:

①编写Verilog HDL语言,实现模200的二进制加法计数器;

②编译,编译成功后建立仿真波形文件,并调整波形文件尺度,直至波形窗口的竖直虚线出现;

③按格子给各输入赋值,计数结果用Unsigned Decimal显示,并保存仿真波形文件;

④执行仿真命令,观察得到的输出的值,进行逻辑分析;

⑤任务一完成,此时可关闭工程。

(2)源程序代码

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-N4KPClrO-1633920388618)(file:///C:\Users\User\AppData\Local\Temp\ksohtml\wps72E7.tmp.jpg)]](https://img-blog.csdnimg.cn/b59290f945c8442e9e1d7bc59f6dd122.png?x-oss-process=image/watermark,type_ZHJvaWRzYW5zZmFsbGJhY2s,shadow_50,text_Q1NETiBA5bCP5aSp5omN5omN,size_16,color_FFFFFF,t_70,g_se,x_16)

任务二

(1) 步骤:

①编写Verilog HDL语言,实现偶数分频器;

②编译,编译成功后建立仿真波形文件,并调整波形文件尺度,直至波形窗口的竖直虚线出现;

③按格子给各输入赋值,并保存仿真波形文件;

④执行仿真命令,观察得到的输出的值,进行逻辑分析;

⑤任务二完成,此时可关闭工程。

(2) 源程序代码

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-rW6BPtDj-1633920388622)(file:///C:\Users\User\AppData\Local\Temp\ksohtml\wps72E8.tmp.png)]](https://img-blog.csdnimg.cn/de442a39eea747128e06efb505b8e57c.png?x-oss-process=image/watermark,type_ZHJvaWRzYW5zZmFsbGJhY2s,shadow_50,text_Q1NETiBA5bCP5aSp5omN5omN,size_18,color_FFFFFF,t_70,g_se,x_16)

任务三:

①步骤

实现一个带有闪烁功能的共阳极七段数码管的显示译码控制电路(在 1 个数码管上动态循环显示 0~F,每个数字显示时间为 1s)。

可在 clk 的高电平期间让数码管亮,这 clk 低电平期间让数码管灭,达到 闪烁的效果。也可用某个计数器来实现闪烁效果。

②源程序代码

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-LTIlkWNW-1633920388627)(file:///C:\Users\User\AppData\Local\Temp\ksohtml\wps72E9.tmp.jpg)]](https://img-blog.csdnimg.cn/e974f60ac0a941448f801b4414fb0eb9.png?x-oss-process=image/watermark,type_ZHJvaWRzYW5zZmFsbGJhY2s,shadow_50,text_Q1NETiBA5bCP5aSp5omN5omN,size_20,color_FFFFFF,t_70,g_se,x_16)

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-EvBpW3Qm-1633920388636)(file:///C:\Users\User\AppData\Local\Temp\ksohtml\wps72F9.tmp.jpg)]](https://img-blog.csdnimg.cn/cd9072d21c574a29a9a48cec09e0dca6.png?x-oss-process=image/watermark,type_ZHJvaWRzYW5zZmFsbGJhY2s,shadow_50,text_Q1NETiBA5bCP5aSp5omN5omN,size_20,color_FFFFFF,t_70,g_se,x_16)

四、实验结果与分析

1.任务一

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-NnTRf4zh-1633920388639)(file:///C:\Users\User\AppData\Local\Temp\ksohtml\wps72FA.tmp.jpg)]](https://img-blog.csdnimg.cn/491e5c87499441638836320ee794ea70.png?x-oss-process=image/watermark,type_ZHJvaWRzYW5zZmFsbGJhY2s,shadow_50,text_Q1NETiBA5bCP5aSp5omN5omN,size_20,color_FFFFFF,t_70,g_se,x_16)

2.任务二

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-aKnNVL00-1633920388642)(file:///C:\Users\User\AppData\Local\Temp\ksohtml\wps72FB.tmp.jpg)]](https://img-blog.csdnimg.cn/62b8f5db4073495e8cf890d642c89de2.png)

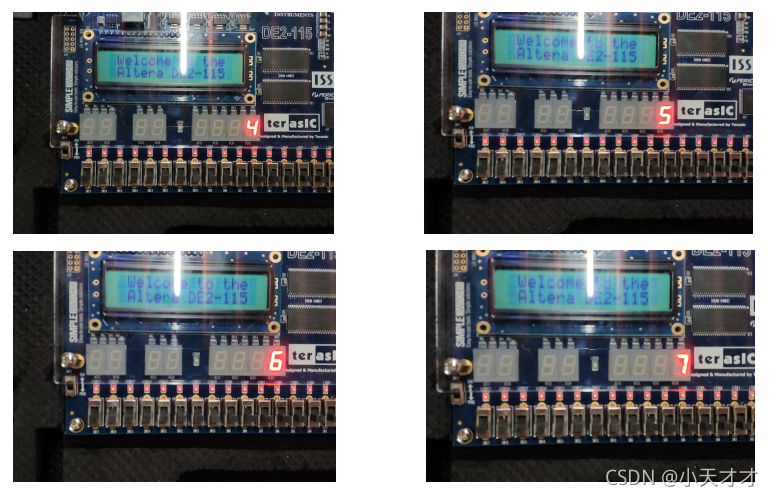

3.任务三

4.实验总结

经过三次的eda实验课程,已经可以基本掌握Verilog HDL语言的基本语法,也可以用这种语言完成一些加法器、全加器、分频器等设计,对于比较复杂的器件设计,比如本次实验的任务三,通过课上向老师询问解决办法,以及课前对相应的理论知识进行了很好的研习,使得这次实验的任务圆满完成。以后也要在课前及时回顾本次实验课所需的理论知识,避免在课上手忙脚乱,一时半会儿对本次实验手足无措,同时也希望自己在eda上的能力可以进一步得到提升。