步骤1:零件清单

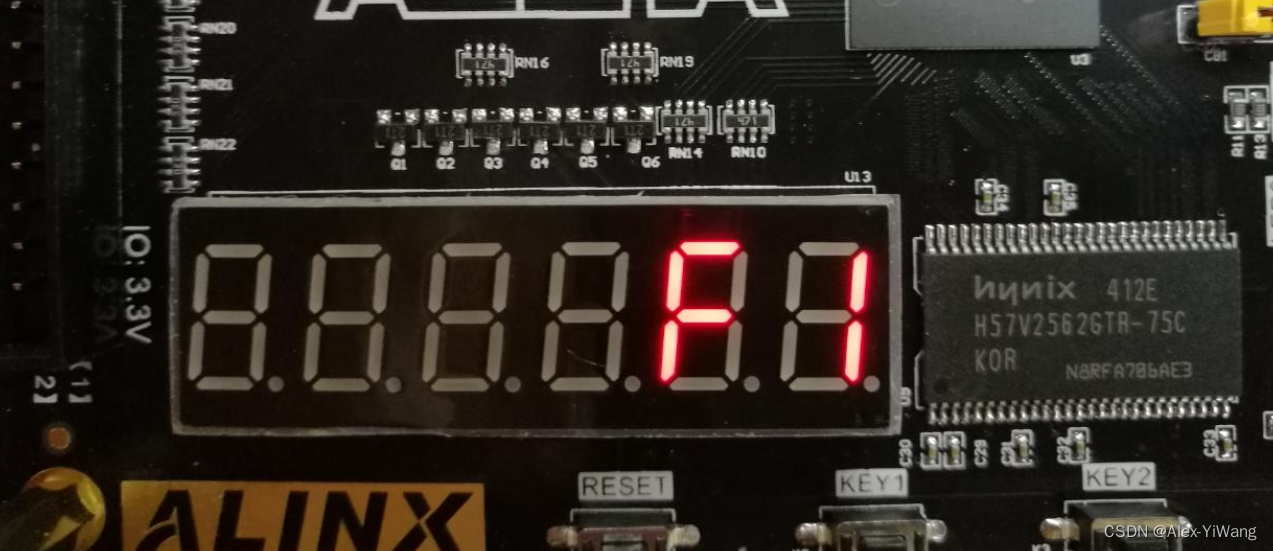

0。运行Ubuntu

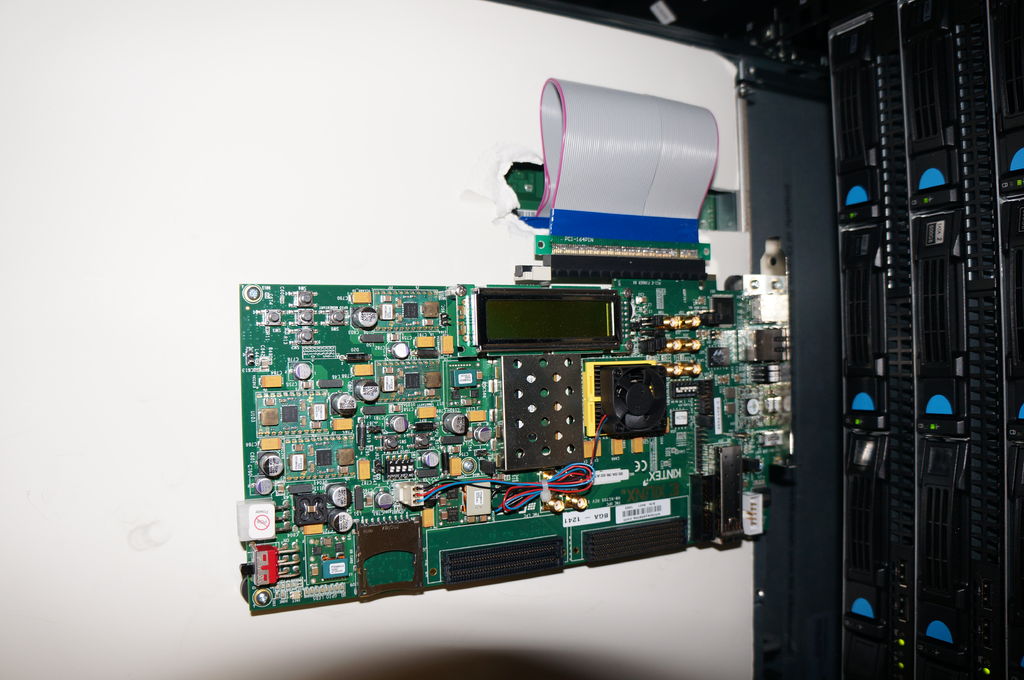

1的构建/主机计算机。 Xilinx VC707或KC705板

2。 FPGA板电源线

3。 USB转Micro-USB电缆

4。 8线PCIE带状电缆(可选)

步骤2:将板卡连接到主机

如果外形尺寸如果允许,将板卡直接插入主机板主板上的开放PCIE插槽中。在这些说明中,我们使用的是1u机架式服务器,需要使用PCIe带状电缆。

步骤3:连接编程电缆

将电缆的MICRO USB端连接到Digilent USB JTAG表面安装的编程模块,另一端连接到主机上的空闲USB端口

步骤4:连接电源线

将电源线连接到板上,并将另一端插入墙上的插座。

步骤5:安装Vivado

如果要使用Connectal Build服务,请跳过此步骤。

p》

Connectal当前支持版本2014.1

步骤6:安装Bluespec

如果您正在使用Connectal Build Service,请跳过此步骤。

在某些计算机上,基础的Haskell运行时需要特定版本的libgmp。这种依赖性似乎是人为的,可以使用以下命令轻松伪造:

sudo ln -s /usr/lib/x86_64-linux-gnu/libgmp.so.10.1.3 /usr/lib/x86_64-linux-gnu/libgmp.so.3

步骤7:安装Connectal

即使您在使用Connectal Build Service时,必须安装软件包才能对设备进行编程并执行设计。以下命令将添加连接存储库并下载/安装软件包:

sudo apt-add-repository -y ppa:jamey-hicks/connectal

sudo apt-get update

sudo apt-get install connectal

您将需要重新引导计算机(对于udev)。如果未自动加载portalmem驱动程序,请使用modprobe

sudo modprobe portalmem

加载它。安装脚本会将Connectal源代码写入/usr/share/connectal。

第8步:编译并运行设计

如果您使用的是Connectal Build Service,请按照此处的示例进行构建(请确保使用https://github.com/connectal-examples/simple.git并选择正确的构建目标)。否则,请继续执行此步骤以在本地下载并编译设计。

检出一个示例项目,然后为已安装的板(kc705)编译构建该项目。

git clone https://github.com/connectal-examples/simple.git

cd simple

make CONNECTALDIR=/usr/share/connectal IPDIR=~/connectalip build.kc705

最后,运行示例:

make CONNECTALDIR=/usr/share/connectal IPDIR=~/connectalip run.kc705

如果这是您在安装主板后的首次尝试,则运行命令将失败,并显示以下错误(或类似错误):

Failed to open /dev/portal1 fd=-1 errno=2

如果是这种情况,请重新引导主机再次运行计算机(用于检测BIOS PCIe)并重新调用运行命令:

mdk@xg06:~/sandbox/simple$ make CONNECTALDIR=/usr/share/connectal IPDIR=~/connectalip run.kc705

make -C kc705 BOARD=kc705 --no-print-directory run

/usr/share/connectal/scripts/run.pcietest bin/mk*.bin.gz bin/ubuntu.exe

+ set -e

+ dirname /usr/share/connectal/scripts/run.pcietest

+ cd /usr/share/connectal/scripts

+ pwd

+ export SCRIPT_DIR=/usr/share/connectal/scripts

+ echo run.pcie parameters are: bin/mkTop.bin.gz bin/ubuntu.exe

run.pcie parameters are: bin/mkTop.bin.gz bin/ubuntu.exe

+ SSHPARAM= -o StrictHostKeyChecking=no

+ [ != ]

+ BOARD_SERIAL=

+ [ != ]

+ TIMELIMIT=3m

+ [ != ]

+ [ != 1 ]

+ fpgajtag bin/mkTop.bin.gz

fpgajtag: Digilent:Digilent Adept USB Device:210203339470; bcd:700

fpgajtag: unzip input file, len 731639

fpgajtag: bypass already programmed bc

fpgajtag: bypass already programmed bc

fpgajtag: bypass already programmed bc

STATUS 00401079 done 0 release_done 0 eos 10 startup_state 0

fpgajtag: Starting to send file

fpgajtag: Done sending file

STATUS 00401079 done 0 release_done 0 eos 10 startup_state 0