定点数就是小数位宽不发生改变的数,小数点位置固定。

定点数位宽构成:{符号位,整数位,小数位}

当定点数为有符号数,数据的最高位为符号位,整数位和小数位需要根据精度去定义位宽。

假如一个定点数位宽为8位,1位符号位,0位整数位,7位小数位,定点数对应量化范围是-1 ~ +1,小数精度为 1/(2^7);那么134定点数为整数,但表示的是 134*(1/(2^7)),其值为134所对应的浮点数。

举例:-123的定点数对应二进制补码?浮点数? (数据格式:1位符号位,0位整数位,7位小数位)

二进制补码:2^8-123

浮点数:-123 * (1/(2^7))

有符号定点数加减法运算法则:

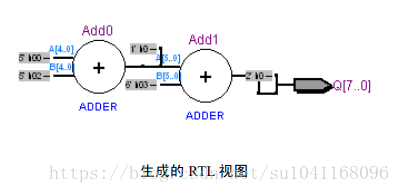

有符号定点数做加法:127+(-110) = 8‘b0111_1111 + 8'b1001_0010 = 9'b1_0001_0001 = 273;

实际结果应该为17;原因在于有符号定点数加法会产生溢出,需要在做加法之前把加数和被加数扩展一位位宽,最后的结果为{1位符号位,1位整数扩展位,7位小数位};对于负数,则需要把最高位扩展。

9’b0_0111_1111 + 9'b1_1001_0010 = 10'b10_0001_0001;因为加法结果为9bit,所以要把最高位1丢弃,结果为9'b0_0001_0001=17,{1位符号位,1位整数扩展位,7位小数位}。

有符号数乘法运算法则:

-1.2*0.8使用定点数进行定点化计算

{1位符号位,3位整数位,10位小数位}

先转换为 1.2*0.8

1.2定点数:2^10*1.2;0_0100_1100_1100

0.8定点数:2^10*0.8;0_0011_0011_0011

两数相乘之后,位宽26位,整数位6位,小数位20位

1.2*0.8=00_0000_1111_0101_1000_1010_0100=1005732

转化为负数2进制补码,加1位符号位,27位

2^27-1005732=133211996=111_1111_0000_1010_0111_0101_1100

即为-1.2*0.8的二进制补码。

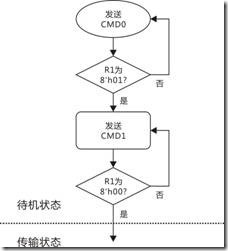

有符号数除法运算法则:

在做定点化除法运算时,最好把除 数被除数定义为一样位宽,小数点位置一样,也就是定点数的小数位宽和整 数位宽一致。这样计算结果好处理。

比如:除数是 10 位整数,8 位小数。被除数是 8 位整数,8 位小数,这时候只需要把被除数高位补 2bit0 即可变为相同位宽。

当除数被除数小数部分位宽不等时,例如,除数 8bit 整数,小数位 8bit;被除数 8bit 整数,小数位 4 位。需要在被除数的小数位低位补齐 4 个 bit0;保证小数位和除数一致。

公式:被除数=商*除数+余数

余数就是可以转化为小数部分;

无符号数除法的小数位宽:

FractRmd 是小数部分,IntRmd 是余数,2^F 是指余数的量化位宽,或者小数 量化位宽。无符号数的小数位宽和 F 设置一致,假如设置小数位宽为 16 那么 小数位宽就是 16 位。

100/1234=0.081037—转化定点数=0.081037*2^16=5310

将整数部分和小数部分拼接={整数部分,小数部分}

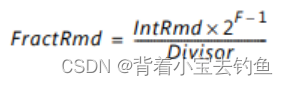

有符号数除法的小数位宽:

FractRmd 是小数部分,IntRmd 是余数,2^F-1 是指余数的量化位宽,这里因 为是有符号数,小数部分最高位用于符号位,剩余 F-1 位是小数位。例如设置有符号除法小数 16 位,那么实际小数只有 15 位,最高位为符号位。

如果使用小数需要和整数部分拼接,有符号数都是二进制补码的形式。

例如 16 位小数 有符号数 1111_1111_1111_1000=-(8/32768)

除法器输出商整数 3 位带有符号,1 位符号位 2 位整数位 101(十进制的-3) 将整数部分和小数部分拼接={整数[2:0],小数部分[14:0]} //1 位符号位 2 位整数位 15 位小数位。