项目目录

- 1.实验目的

- 2.准备阶段

- 3.实验原理

- 4.编写Verilog HDL程序

- 5.配置引脚

- 6.查看和分析RTL

- 7.下载程序

- 8.总结

1.实验目的

- 查阅AX4010黑金系列用户手册,编写按键程序,实验简单的按键控制LED的功能,同时学习 Quartus RTL Viewer 的使用

2.准备阶段

-

电脑安装Quartus13.1软件

-

FPGA开发板为黑金AX4010系列,型号为EP4CE10F17C8

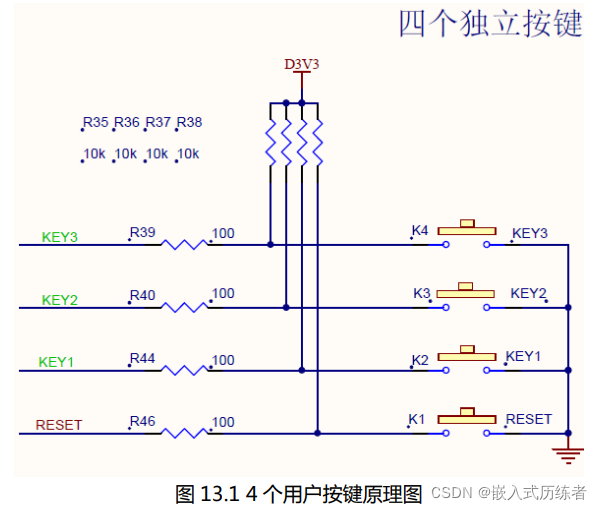

3.实验原理

- 由用户手册知按键和LED的原理图

此时我们知道按键按下为低电平有效,释放被上拉电阻拉到高电平,而LED点亮是高电平有效

4.编写Verilog HDL程序

`timescale 1ns / 1ps

module key_test

(input clk, //system clock 50MHZinput[3:0] key, //输入四个键信号,当按下键时,值为0output[3:0] led //LED显示输出

);reg[3:0] led_r; //定义第一阶段寄存器,生成四个D触发器reg[3:0] led_r1; //定义第二阶段寄存器,生成四个D触发器always@(posedge clk)begin led_r <= ~key; //~取反,因为按键按下为低电平有效endalways@(posedge clk)beginled_r1 <= led_r;endassign led = led_r1;

endmodule

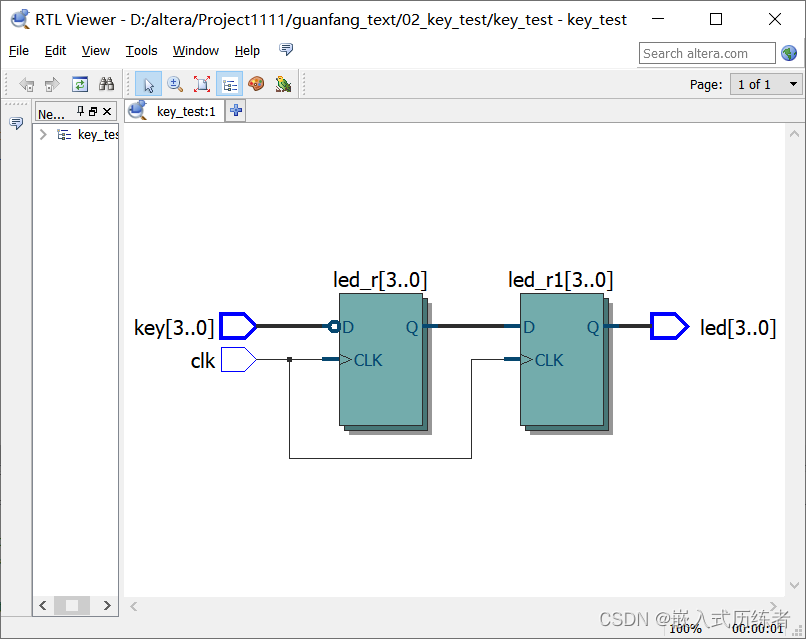

- 这个程序没有设计的很复杂,通过简单的硬件描述语言看透硬件描述语言和 FPGA 硬件的联系。首先我们将按键输入经过一个非门后再经过 2 组 D 触发器。一个经过 D 触发器的信号,会在D 触发器时钟上升沿锁存然后再送到输出。

5.配置引脚

这里不详细讲解,参考上一节博客【FPGA从0开始系列】在Quartus13.1下LED流水灯实验(一)

这篇博客将手把手教你从创建工程开始,再到编译,配置引脚,下载,固化程序等详细教程。

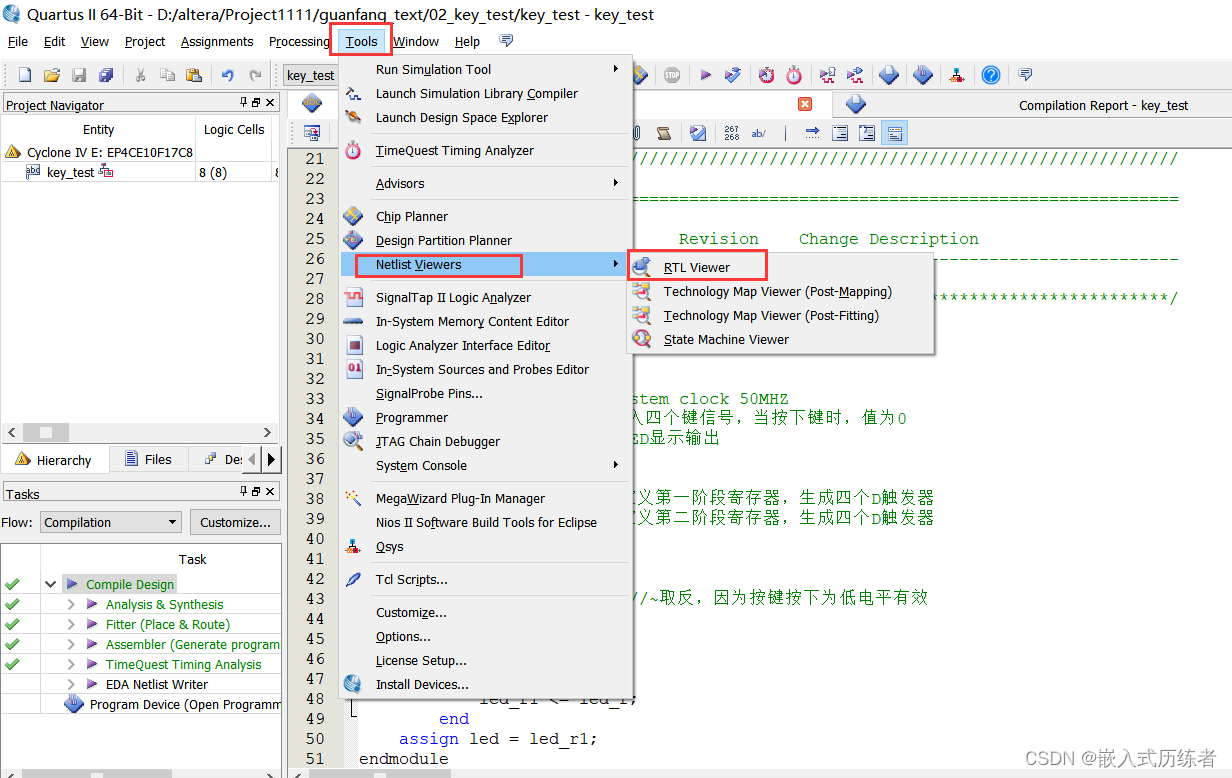

6.查看和分析RTL

- 仔细想想Verilog HDL(全称为Verilog Hardware Description Language ),HDL:硬件描述语言,老外起名字非常的讲究,这个D指的是Description 描述,而不是Design:设计,这一点认识十分重要!

- 描述,描述,实际上电路本身已经存在了,我们只需要给FPGA说一下电路图,让它自己在板子接通那些需要接通的线就OK了,但是电路原理图虽然直观,但是麻烦。而Verilog HDL本质上就是将原理图描述成文本语言,剩下的就交给EDA工具去完成,去布线。美滋滋!

- 电路不是Verilog HDL编程出来的,是已经存在了,只是用语言把它描述出来能,做到“心中有电路”

- 点击Tools------>Netlist Viewers------>RTL Viewers即可看到RTL,看到自己描述的电路。

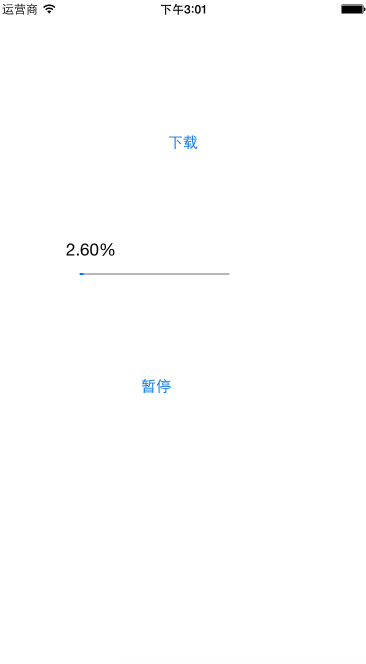

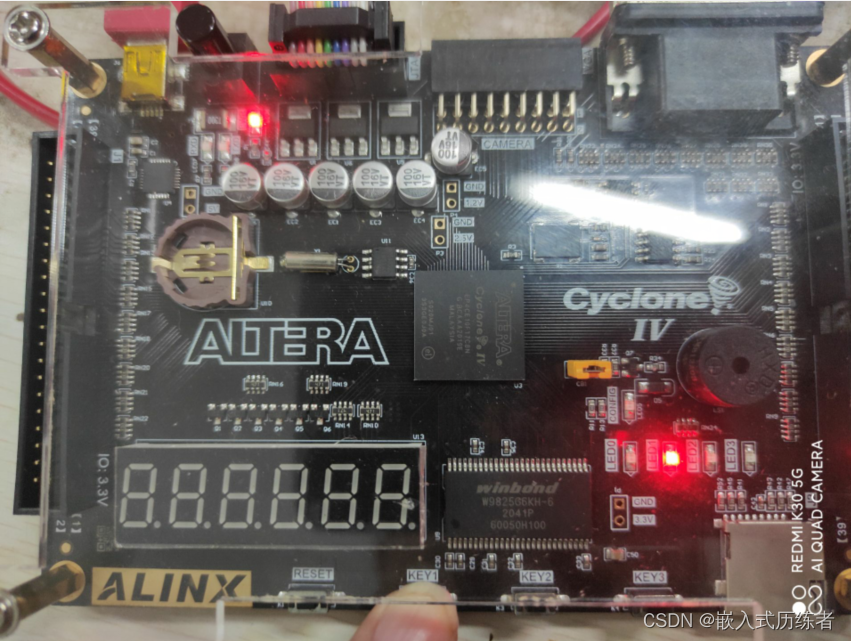

7.下载程序

- 按下KEY1点亮LED1灯,其他的RESET,KEY2,KEY3对应相应的LED0,LED2,LED3。

8.总结

- Verilog代码的过程并不是编程,而是把已经设计好的数字电路转换成文本语言的形式。

- 尤其是可综合的HDL,不应该看到的是语言本身一条条代码,而是要看到语言背后所对应的硬件电路结构,也就是原理图,要心中有电路!

module key_test

(input clk, //system clock 50MHZinput[3:0] key, //输入四个键信号,当按下键时,值为0output[3:0] led //LED显示输出

);

对于这样的模块的端口定义,所谓模块的端口,就是声明了模块的输入输出口。其格式是

module 模块名(口1,口2,口3,口4, ………);

标题4中的Verilog HDL其实是可以写的:

module key_test(input clk, input[3:0] key, output[3:0] led );

第一种是为了可读性考虑,但可能对于初学者,对下面一句话产生误解(特提一下)。夏宇闻的《从算法设计到硬线逻辑的实现》

除了endmodule语句外,每个语句和数据定义的最后必须有分号。

**转载请注明作者和出处!感谢,码字不易! **