首先找到tomcat得bin目录录下边得startup.bat 编辑文件

call "%EXECUTABLE%" start %CMD_LINE_ARGS%

换成

call "%EXECUTABLE%" run %CMD_LINE_ARGS%修改之后 如下

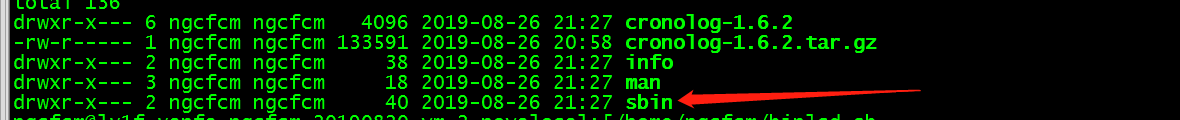

cronolog.exe 去下边得链接去下载,我也是花了一块钱去下载的,找了一圈全部都是csdn积分下载。

链接:https://pan.baidu.com/s/18macsXns113GcLAaIOQZcg

提取码:93r6

下载完毕就把cronolog.exe复制到tomcat的bin的目录下边别的文件不需要 只要cronolog.exe就可以了

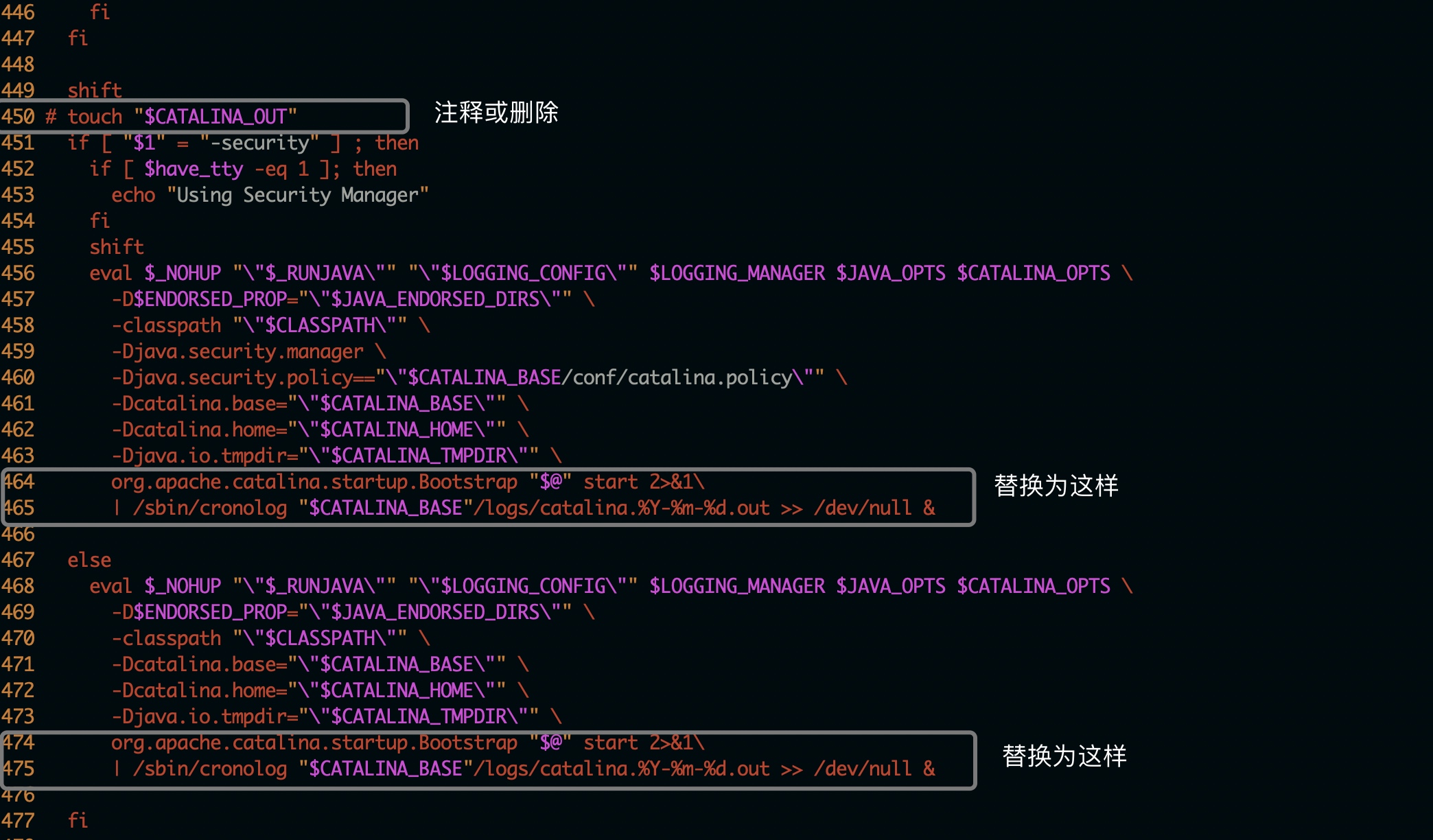

修改tomcat的 catalina.bat文件

%ACTION%后面加上 下边得全部复制 别漏了

| .\cronolog.exe %CATALINA_HOME%\catalinaLog\catalina.%%Y-%%m-%%d.outcatalinaLog这个文件是在你tomcat下的一个文件 你也可以自定义 如下

catalina.%%Y-%%m-%%d.out 这个就是一个文件名加一个时间戳 你也可以一定义都可以

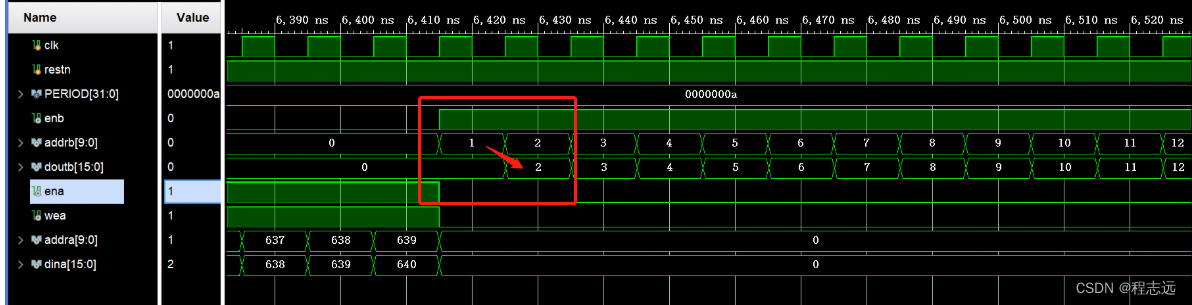

下边是改过之后的我用红框标记了

修改完毕之后 启动tomcat 去看下这个文件下有没有一个今天日期.out的文件 有了就表示成功了