在FPGA逻辑设计时,需要参考所需逻辑资源对FPGA进行选型,其中一项就是对BRAM的评估,在这里以xilinx UltraSCALE+系列FPGA为例,对BRAM进行简单介绍。

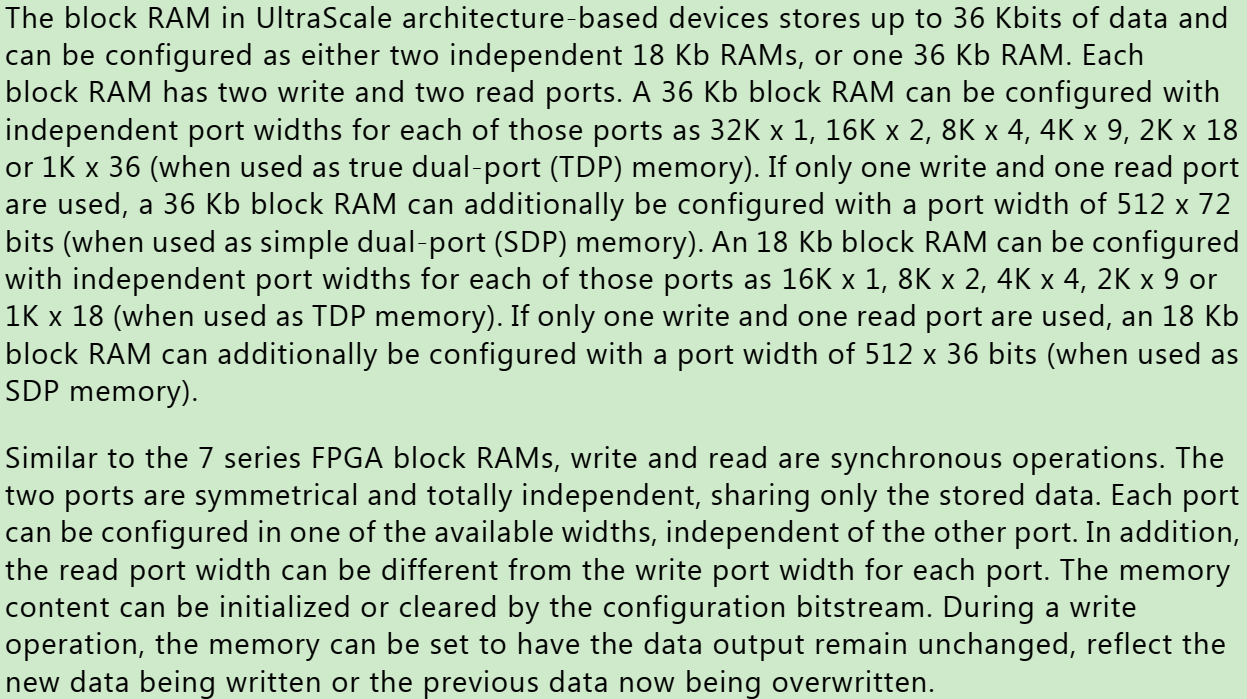

FPGA中RAM资源一般分为DRAM和BRAM两种,而Xilinx UltraSCALE+系列FPGA除了以上两种RAM之外,部分型号还包括UltraRAM。其中DRAM为Distributed RAM,是以FPGA中LUT(LUT in SLICEM)资源产生的,详细资料参考UG574:UltraScale ArchitectureConfigurable Logic Block User Guide;UltraRAM为一个时钟,两个端口(读写),同步读写,每个Block存储容量可达288Kb,一个时钟域可包含16个UltraRAM Blocks,而每个Block由4K x 7 、2 memory block组成,详细参考资料见UG573:UltraScale ArchitectureMemory Resources User Guide。

本文主要对BRAM进行简单介绍,并给出BRAM资源评估的方法。BRAM的详细参考资料参考UG573:UltraScale ArchitectureMemory Resources User Guide。

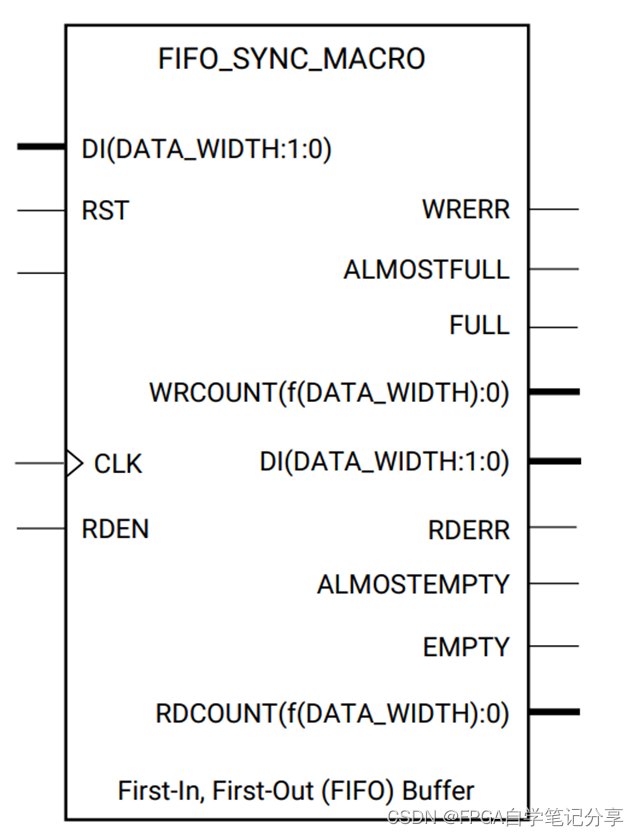

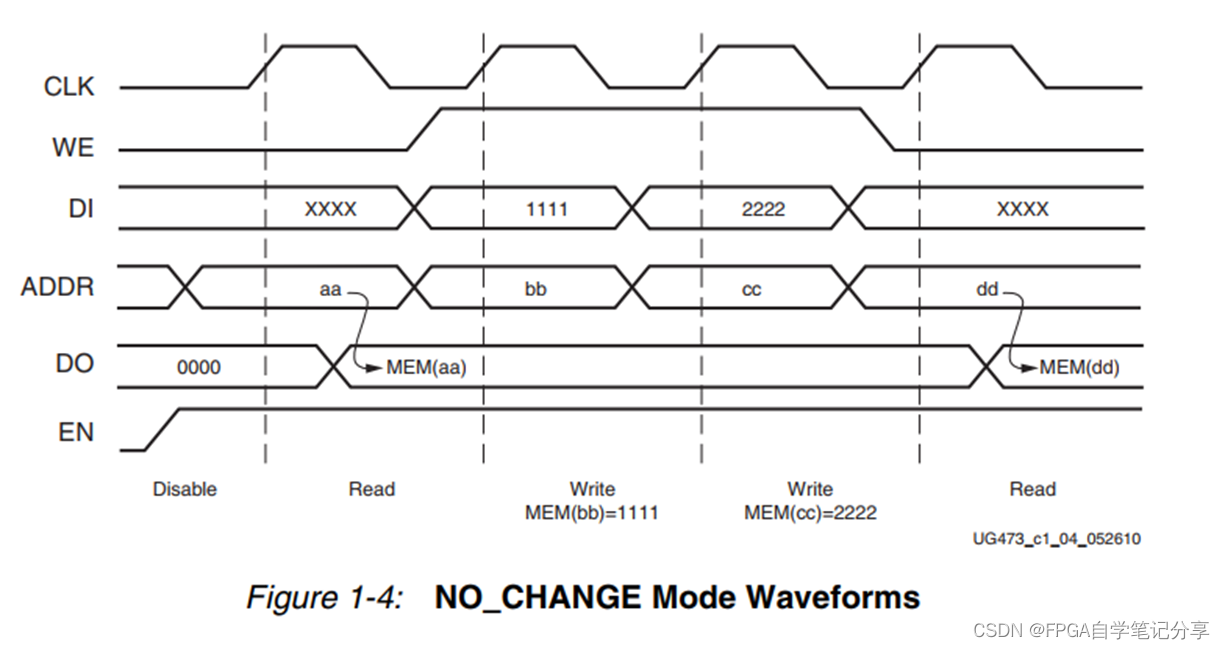

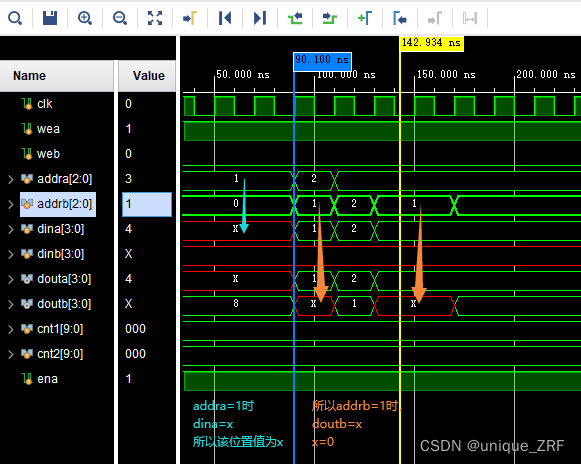

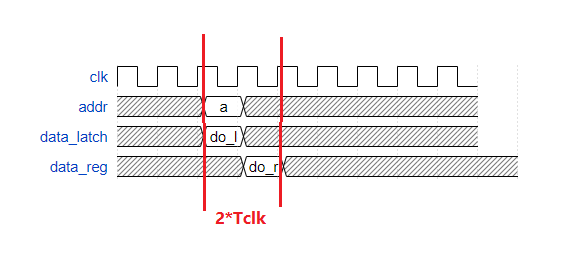

BRAM属于FPGA内嵌专用RAM,RAM块有较大的的存储空间,目前xilinx典型的BRAM有18Kbits和36Kbits。BRAM一定有时钟,DRAM可以是纯组合逻辑不用时钟,也可以增加一级reg使用时钟。BRAM读写端口可配,深度可配,多个BRAM block可组合级联,根据需要在允许范围内可以设置不同位宽不同深度(存储)的RAM块。

例如:需要将一个文件先存入RAM中,在FPGA系统启动后读取RAM中的数据进行处理,coe文件中存储数据为10230个32bit位宽的数据,那么在IP核中RAM的设置位宽设置为32bit Width,Depth可设置为>10230,如果设置为10230,则RAM存储容量为32*10230=327360bits≈39.96KB,这也是数据的真实数据大小。配置完成后IP配置项显示使用36K BRAM共计10个Blocks,即10*36*1024=368640bits=45KB,这是由于一个Block块的大小为36Kb,根据IP配置的深度,所需RAM块的个数大于9小于10,故共需10个36K BRAM块。

通常在配置BRAM时,可将设置深度比实际使用的大一些,留有一定裕量,一般根据情况灵活设置。