使用软件: Vivado

开发板: EGO1采用Xilinx Artix-7系列XC7A35T-1CSG324C FPGA

BRAM 队列实践

- 功能描述

- 功能实现

- 1. 添加BRAM的IP

- 2. 数码管显示

- 3. 时钟分频

- 4. 按键消抖

- 5. 顶层设计

- 结果

- 遇到问题及解决

- 仿真测试

功能描述

数码管3位显示数字,可以按键输入在数码管显示,队列结构,当队列满了之后,再按键时,将从队列头开始修改成当前输入的值。

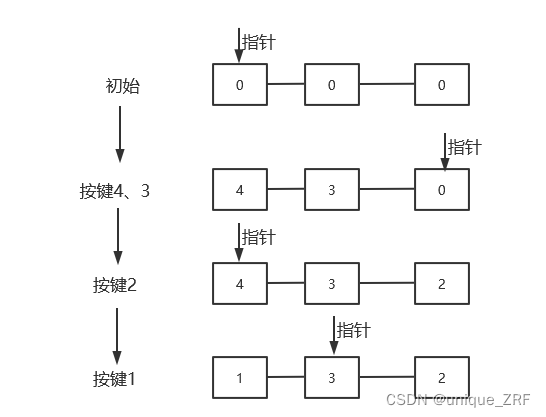

如下图所示:刚开始是0 0 0,

输入4之后变为4 0 0,

再输入3和2变为4 3 2

输入1之后变为 1 3 2

如此循环替换

功能实现

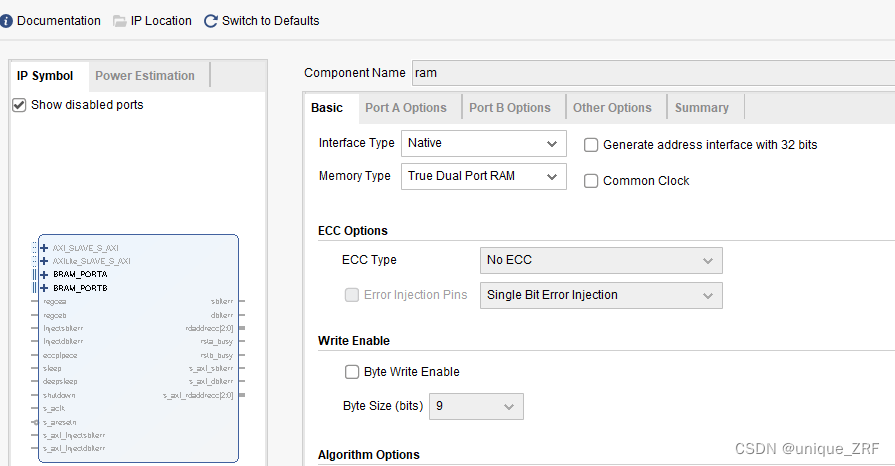

1. 添加BRAM的IP

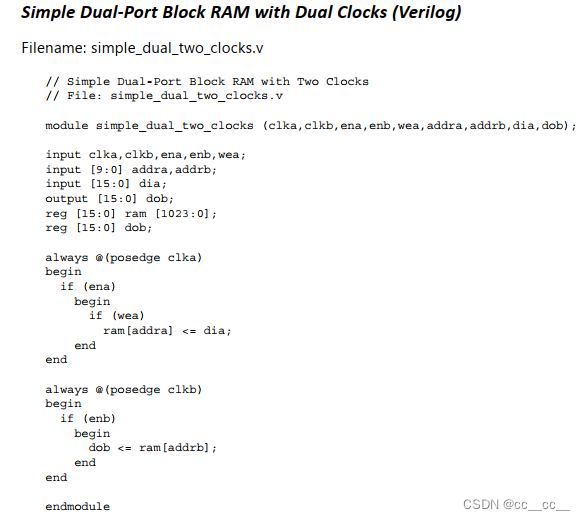

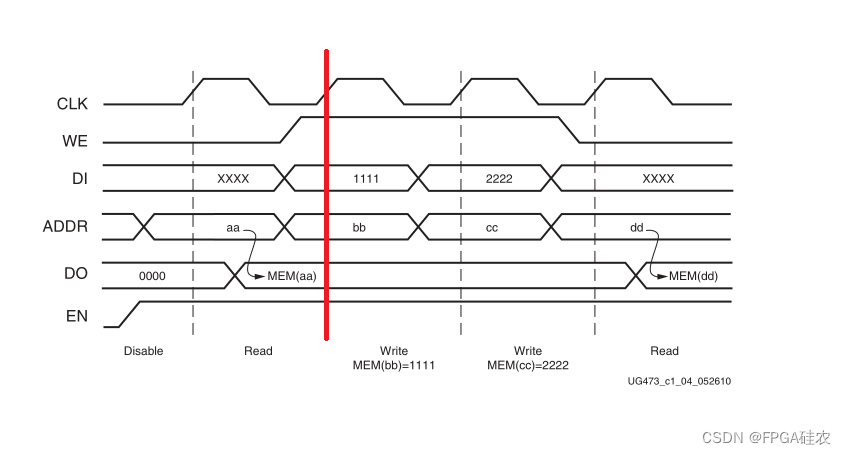

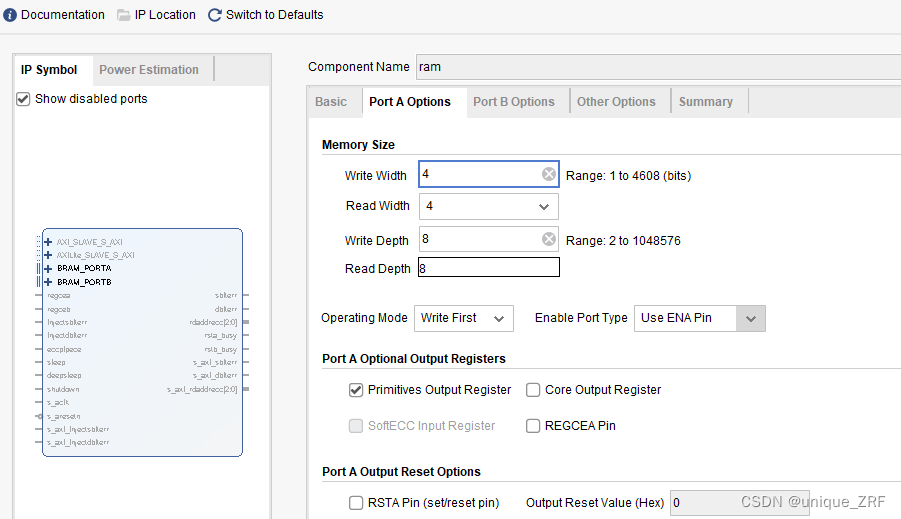

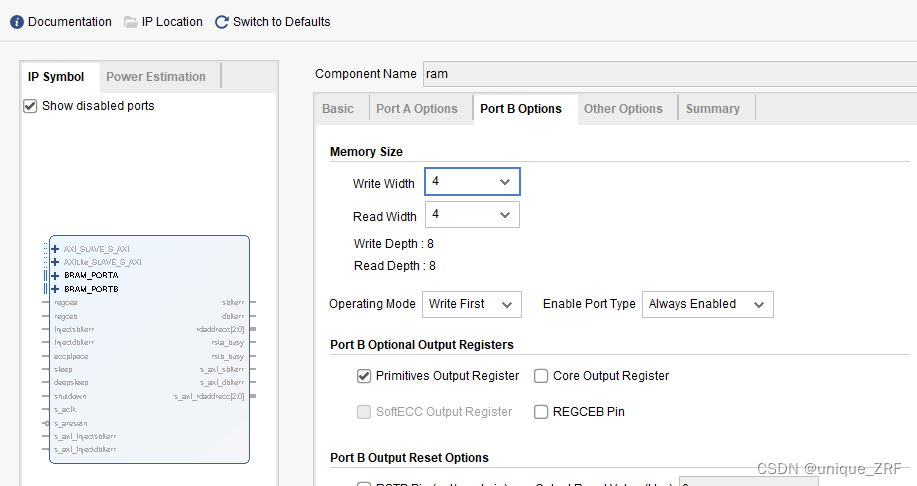

采用双端口,从A端口输入数据,B端口读出数据

其设置如下所示:

基础设置:

端口A设置:

端口B设置:

端口B设置:

2. 数码管显示

采用先前代码,将输入数据位数进行修改,生成IP核以备调用。

3. 时钟分频

采用参数化设计模块,实现代码复用

divclk代码如下:

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2022/10/20 19:39:34

// Design Name:

// Module Name: divclk

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//module divclk(clk,reset_n,clk_out);

input clk;

input reset_n;

output clk_out;

reg[31:0] cnt=0;

reg clk_out=0;

parameter CNT=1000000; //周期20ms = 50Hz cnt=100000000/50/2=1000000

always@(posedge clk or negedge reset_n)

beginif(!reset_n)//复位cnt<=0;else if(cnt==CNT)begincnt<=0;clk_out=~clk_out;endelsecnt=cnt+1'b1;

endendmodule对其复用:

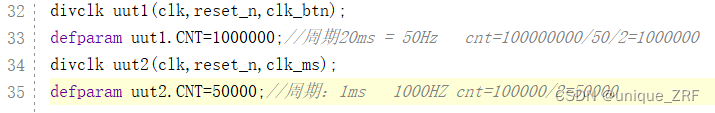

使用defparam来重新定义divclk中的初始参数CNT,实现代码复用

4. 按键消抖

使用前面按键消抖模块的代码即可实现

5. 顶层设计

`timescale 1ns / 1ps

//

// Create Date: 2022/10/20 19:37:03

// Revision 0.01 - File Created

// Additional Comments:

//

//module top_moudle(clk,reset_n,btn,seg,seg1,an,led);

input clk,reset_n;

input[4:0] btn;//按键

output[7:0] seg,seg1,an;

output[4:0] led;

reg[4:0] led;

//时钟分频

wire clk_btn;

wire clk_ms;

divclk uut1(clk,reset_n,clk_btn);

defparam uut1.CNT=1000000;//周期20ms = 50Hz cnt=100000000/50/2=1000000

divclk uut2(clk,reset_n,clk_ms);

defparam uut2.CNT=50000;//周期:1ms 1000HZ cnt=100000/2=50000//按键例化

wire[4:0] btnout;

reg[4:0] btn_out0,btn_out1,btn_down;

ajxd uut3(clk_btn,btn,btnout);

always@(posedge clk_ms)//将按键上升沿转换为1ms的高电平

beginbtn_out0<=btnout;btn_out1<=btn_out0;btn_down<=btn_out0&(~btn_out1);

end

reg wea=1,web=0;

reg[2:0] addra=0,addrb=1;

reg[3:0] dina,dinb=4'b0000;

wire[3:0] douta,doutb;

reg ena=1;

//bram 例化

ram ram(.clka(clk),.ena(ena),.wea(wea),.addra(addra),.dina(dina),.douta(douta),.clkb(clk),.web(web),.addrb(addrb),.dinb(dinb),.doutb(doutb)

);

//always@(btnout)

//begin

// led<=btnout;

// //if(btnout>5'b00000)

// // wea<=1;//写使能

//end

reg[3:0] temp;

reg[3:0] i=0;

always@(posedge clk_ms)

beginled<=btn_down;if(|btn_down==0)begintemp=0;ena=0;endelse begin//有按键按下ena=1; for(i=0;i<5;i=i+1)beginif(btn_down[i]==1)//获取最大键值temp=i;enddina<=temp;if(addra==3)addra<=1;elseaddra=addra+1'b1;end

end//数码管显示

reg[11:0] show_data=12'b000000000001;

smg uusmg(clk,show_data,seg,seg1,an);

reg[2:0] flag2=0;reg[3:0] doutb0,doutb1,doutb2;

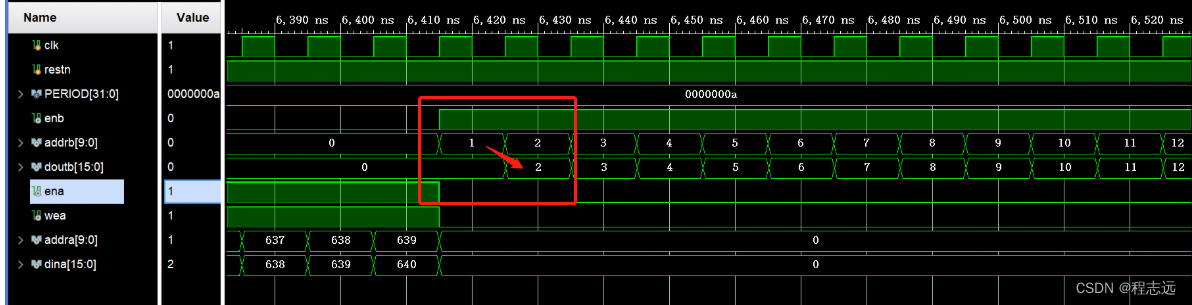

always@(negedge clk_ms)

begin//写入有2个周期的时延doutb0<=doutb;doutb1<=doutb0;doutb2<=doutb1;case(addrb)1:show_data[3:0]<=doutb2;2:show_data[7:4]<=doutb2;3:show_data[11:8]<=doutb2;default:show_data=show_data;endcase if(addrb==3) addrb<=1;elseaddrb<=addrb+1'b1;

endendmodule结果

运行结果

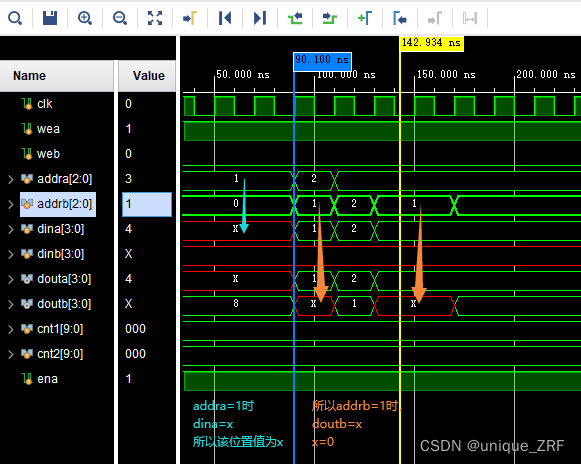

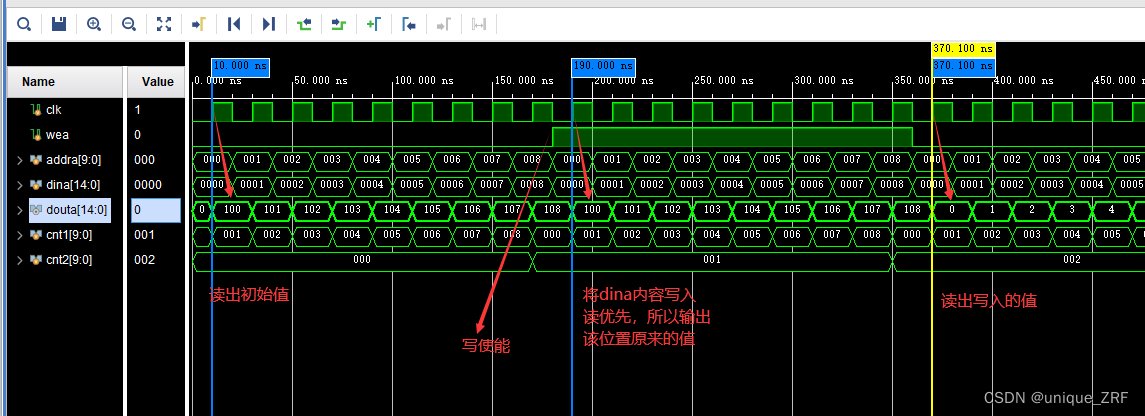

遇到问题及解决

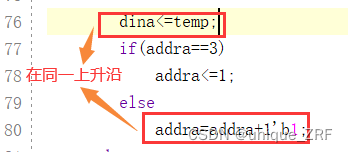

addra赋初值为1时,发现第一个按键数值在地址为2的位置显示。

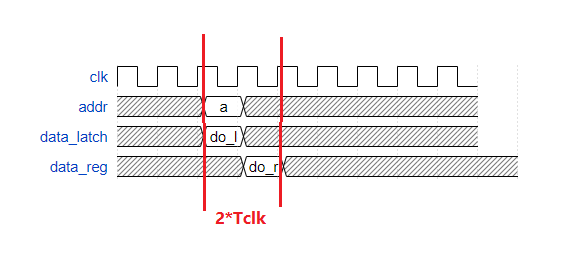

通过仿真发现,dina赋值跟addra+1在同一个上升沿时触发,

则 输入的值,直接写进了addra+1的地址,而不是addra, 所以可以看到数值在地址初值的下一个地址的位置。

仿真测试

测试用例:

`timescale 1ns / 1ps

//

// Create Date: 2022/10/25 10:48:58

// Revision 0.01 - File Created

// Additional Comments:

//

//module bram_test_sim(clk,ena,enb,wea,web,addra,addrb,dina,dinb,douta,doutb);

input clk,ena,enb,wea,web;

input[2:0] addra,addrb;

input[3:0] dina,dinb;

input[3:0] douta,doutb;

ram ram(.clka(clk),.ena(ena),.wea(wea),.addra(addra),.dina(dina),.douta(douta),.clkb(clk),.enb(enb),.web(web),.addrb(addrb),.dinb(dinb),.doutb(doutb)

);endmodule仿真代码

`timescale 1ns / 1ps

//

// Create Date: 2022/10/25 10:59:56

// Design Name:

// Module Name: sim_test

//module sim_test();

reg clk;//时钟输入

reg wea,web;//写使能

reg[2:0] addra=1,addrb=0;//地址输入

reg[3:0] dina,dinb;//数据输入

wire[3:0] douta,doutb;//数据输出

reg[9:0] cnt1,cnt2;

reg ena=1;

initial beginclk=0;wea=1;web=0;cnt1=0;cnt2=0;

end

bram_test_sim uut(//调用被仿真的模块完成内存读写.clk(clk),.ena(ena),.wea(wea),.addra(addra),.dina(dina),.douta(douta),.enb(1),.web(web),.addrb(addrb),.dinb(dinb),.doutb(doutb));always #10 clk=~clk;//周期20ns,模拟50M时钟

initial begin

#90;

ena=1;

dina=4'b0001;

addra=addra+1;

addrb=addrb+1;

#20

ena=1;

dina=4'b0010;

addra=addra+1;

addrb=addrb+1;

#20

ena=1;

dina=4'b0100;

addrb=1;

#20

addrb=1;

#20

addrb=2;endendmodule仿真结果:

addrb=1的位置输出doutb为X

addrb=2的位置输出doutb为1