1、下载安装包,我这下载的是cronolog-1.6.2.tar.gz

2、放到自己有权限的目录下面比如 /home/cronolog/

3、解压

tar zxvf cronolog-1.6.2.tar.gz4、进入cronolog安装文件所在目录

cd cronolog-1.6.22.4 运行安装

./configuremakemake install注:此时执行make install报错,提示Error 1

查看错误信息发现需要在 /usr/local/下新建sbin文件夹,但我这个账号没这个权限,现在又需要使用cronolog来分割日志,只能自己动手,丰衣足食了。

还记得解压完进入文件后执行的命令吗?没错就是./configure,看来解决办法应该在这里

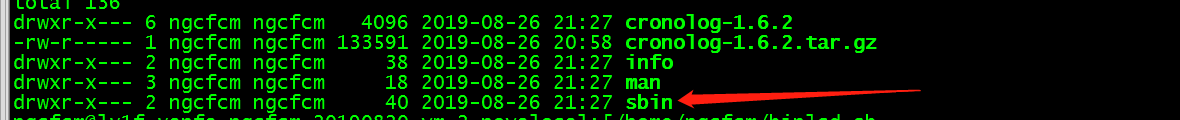

1、进入cronolog-1.6.2文件夹,看下都有什么文件

嗯,有个configure开头的,vim看下(不要吐槽我这个用notepade++打开的截图)

嗯,里面有关键字,改成有权限新建文件夹的目录,保存

再次运行

./configuremakemake install嗯,现在应该是安装成功了,在目录下会多出一个sbin文件夹,里面就是cronolog的可执行文件,可以愉快的分割日志了。