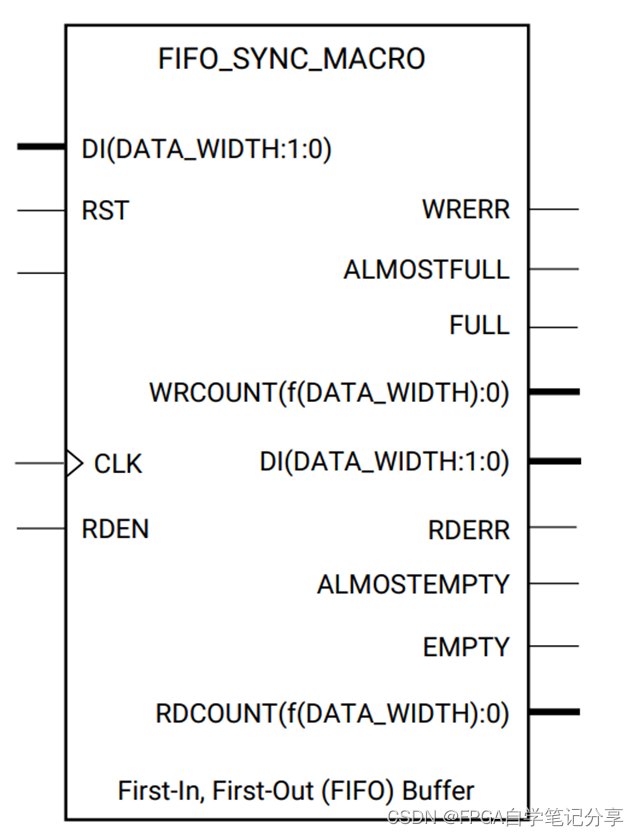

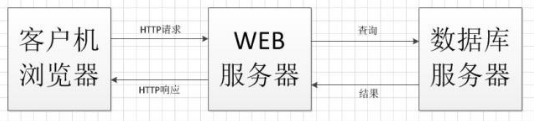

许多FPGA设计使用BRAM来实现FIFO。在Xilinx 7系列体系结构中,块RAM中的专用逻辑能够实现同步或双时钟(异步)FIFO。这消除了计数器、比较器或状态标志生成所需的额外CLB逻辑,并且每个FIFO仅使用一个块RAM资源。支持标准和首字跳转(FWFT)模式。

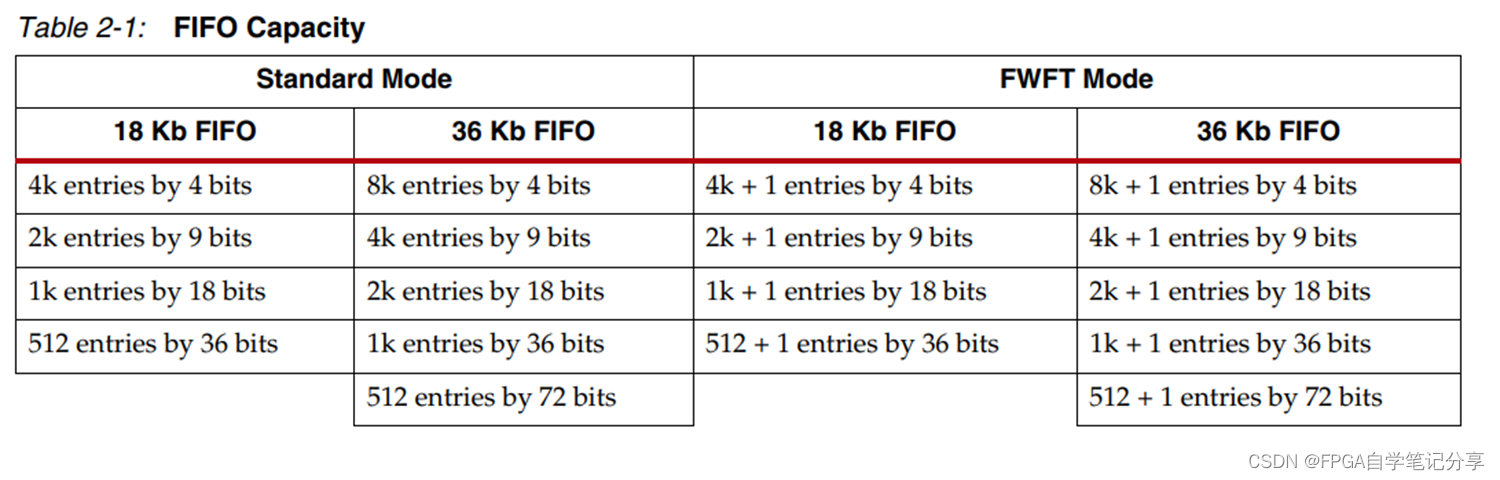

在7系列体系结构中,FIFO可以配置为18 Kb或36 Kb内存。对于18 Kb模式,支持的配置为4K x 4、2K x 9、1K x 18和512 x 36。36 Kb FIFO支持的配置是8K x 4,4K x 9,2K x 18、1K x 36和512 x 72。

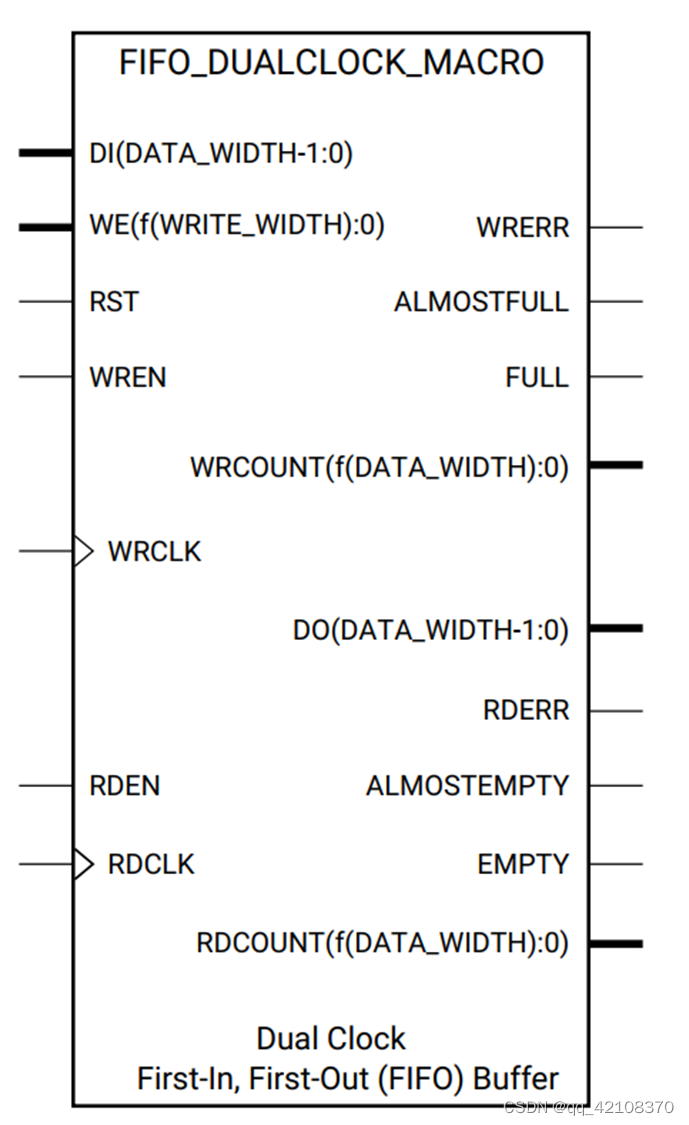

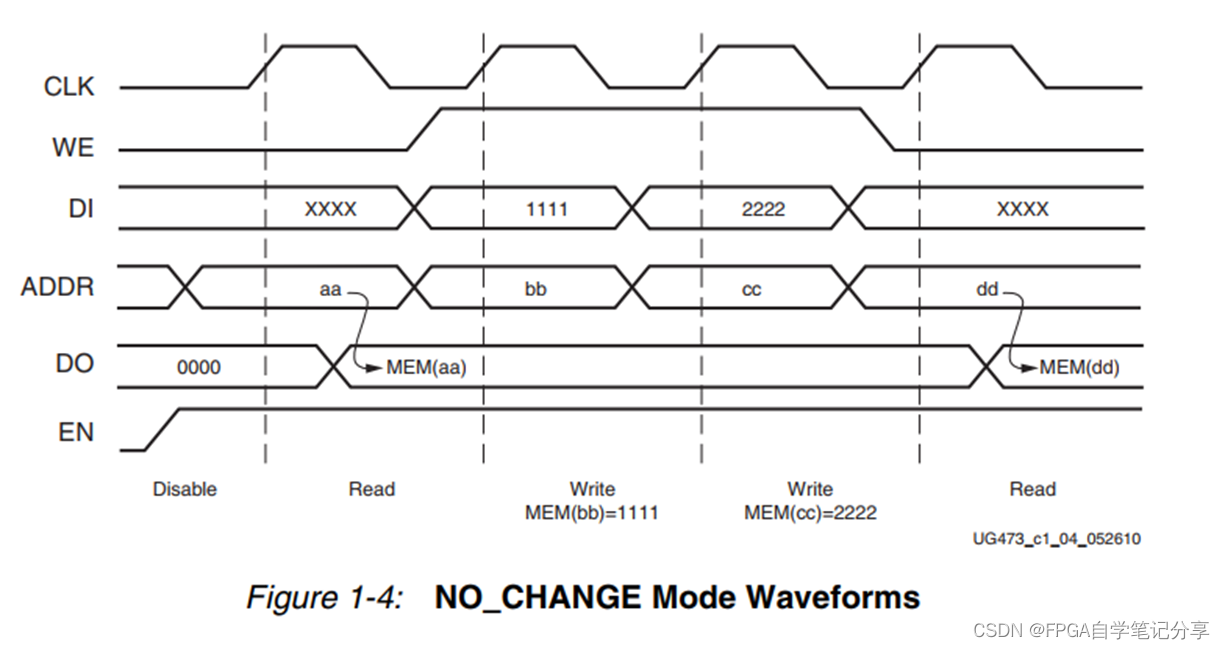

BRAM可以配置为具有公共或独立读写时钟的先进先出(FIFO)存储器。块RAM的端口A用作FIFO读取端口,端口B用作FIFO写入端口。数据在读取时钟上升沿从FIFO读取,并在写入时钟上升沿写入FIFO。在没有外部CLB逻辑帮助的情况下,FIFO模式不支持独立的读写端口宽度选择。

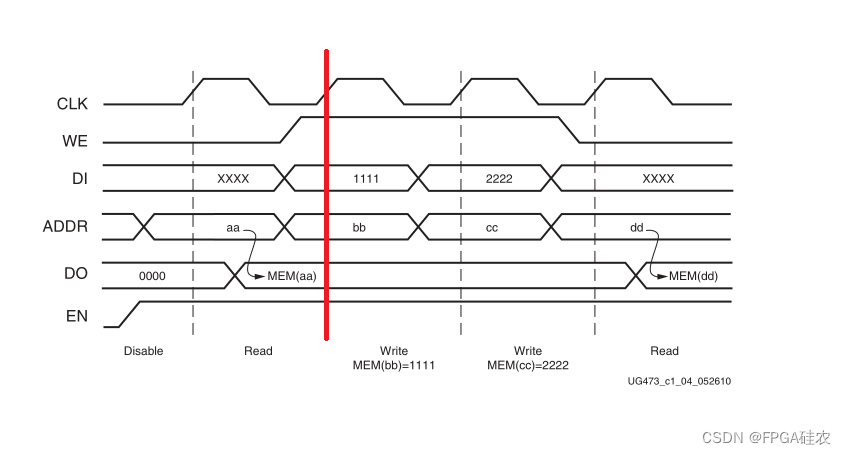

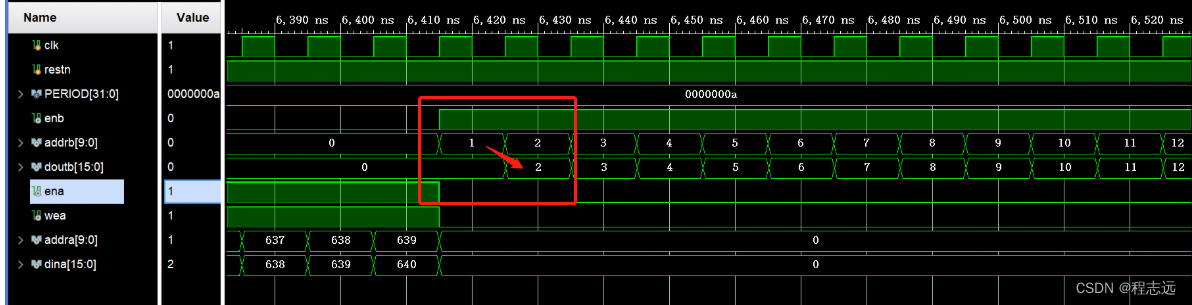

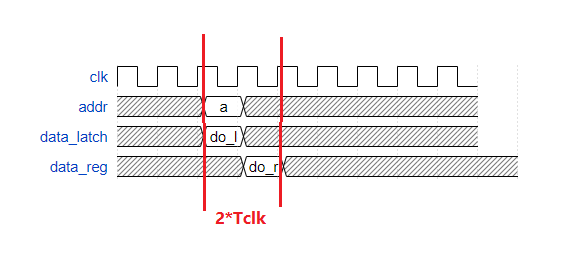

写入操作是同步的,每当WREN在WRCLK上升沿之前的一个设置时间处于活动状态时,将DI处可用的数据字写入FIFO。读取操作也是同步的,每当RDEN在RDCLK上升沿之前的一个设置时间处于活动状态时,在DO处呈现下一个数据字。数据流控制是自动的;还会显示WRCOUNT和RDCOUNT。

但是,使用时必须观察FULL和EMPTY标志,当FULL为高时停止写入,当EMPTY为高时,停止读取。如果违反了这些规则,则处于满状态时的WREN将会触发WRERR标志,处于空状态的活动RDEN将会触发RDERR标志。但是,在这两种情况下,FIFO内容都被保留,地址计数器保持有效。

当FIFO接近极限时,可编程的“几乎满”和“几乎空”标志会显示出来,为您提供早期警告。这两个标志值都可以通过配置设置为(几乎)FIFO地址范围内的任何位置。