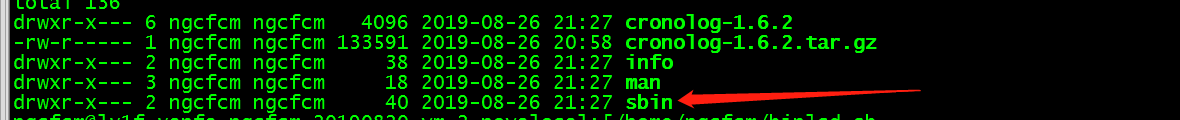

1、将文件复制到制定目录下,解压文件

tar xf cronolog-1.6.2.tar.gz

2、进入目录

cd cronolog-1.6.2

运行配置

./configure &>/dev/null

3、执行

make &>/dev/null

make install &>/dev/null

4、最后修改 tomcat bin目录下catalina.sh

if [ -z "$CATALINA_OUT" ] ; then

CATALINA_OUT="$CATALINA_BASE"/logs/catalina.out

修改为

if [ -z "$CATALINA_OUT" ] ; then

CATALINA_OUT="$CATALINA_BASE"/logs/catalina.out.%Y-%m-%d

(大概在配置文件200行的位置)

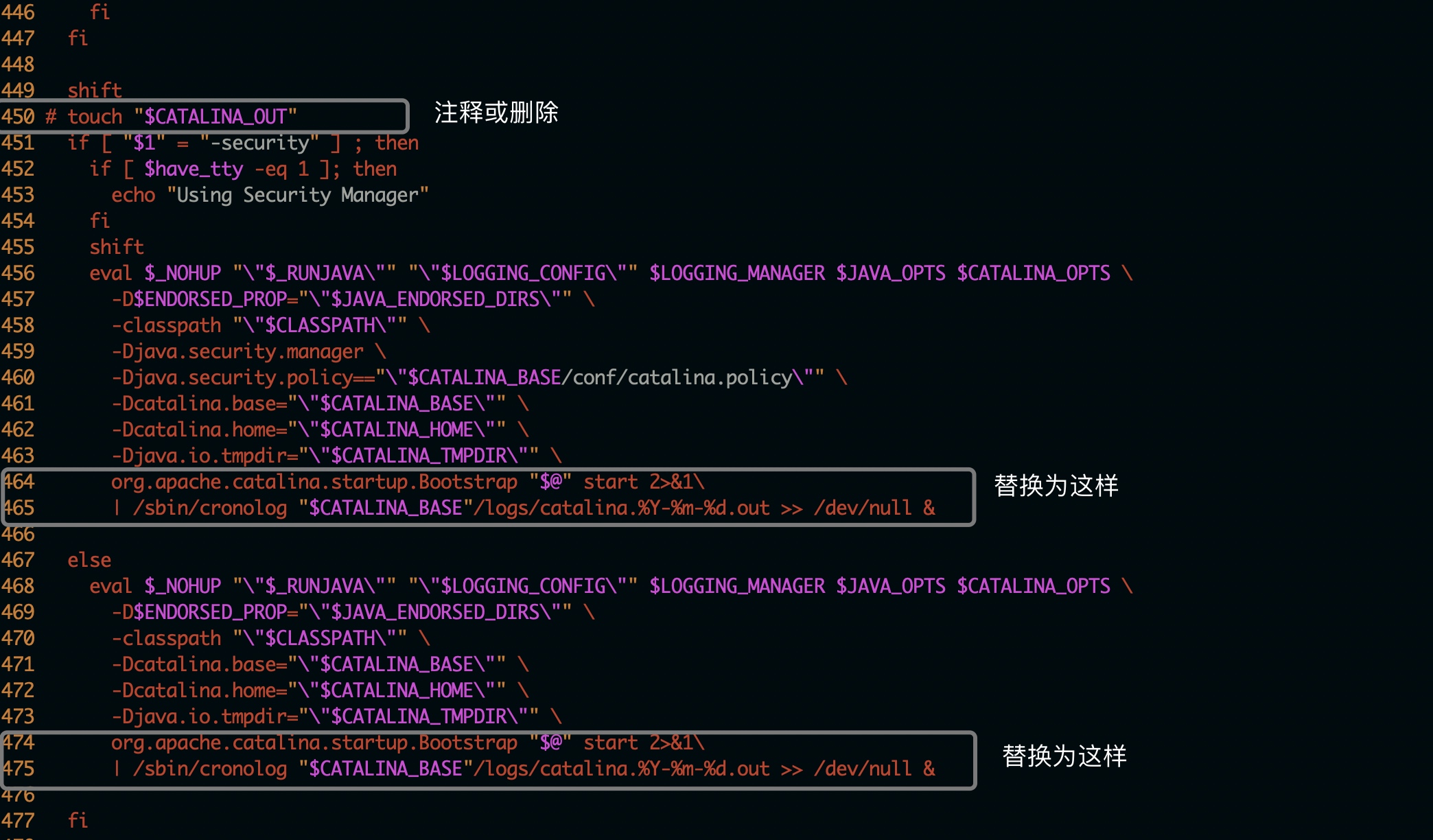

之后再去386行附近,将这行注释掉:

touch "$CATALINA_OUT"

最后一步,在配置文件400行附近,有两段相同的,都需要改动:

org.apache.catalina.startup.Bootstrap "$@" start \

>> "$CATALINA_OUT" 2>&1 &

修改为

org.apache.catalina.startup.Bootstrap "$@" start 2>&1 \

| /usr/local/sbin/cronolog "$CATALINA_OUT" >> /dev/null &

(注意:修改这里第一行最后反斜杠的后面不准有空格,不然会报错)

遇到问题:

configure: error: no acceptable cc found in $PATHchecking for working aclocal... found

checking for working autoconf... found

checking for working automake... found

checking for working autoheader... found

checking for working makeinfo... missing

checking for gcc... gcc

解决 :

安装组件即可

yum install gcc gcc-c++ gcc-g77

目前状况:

日志在存储在 catalina.out.%Y-%m-%d

解决:第三处改动 有两个地方需要改 只修改了一个地方

启动tomcat 报错解决

/tmp/apache-tomcat-6.0.39/bin/catalina.sh: line 382: org.apache.catalina.startup.Bootstrap: command not found

解决方法: 将注释的行 删除即可