就是20ms扫描2个状态,通过2个状态进行判断

module key_test(

input wire key_a,

input wire clk,

input wire rst_n,

output reg led

);

reg [19:0]cnt;

reg key_tma;

always@(posedge clk or negedge rst_n)

if(rst_n==1'b0)

cnt<=20'd0;

else if(cnt==20'd999_999)

begin

cnt<=20'd0;

key_tma<=key_a;

end

else

cnt<=cnt +20'b1;

reg key_tmb;

always@(posedge clk )

begin

key_tmb<=key_tma;

end

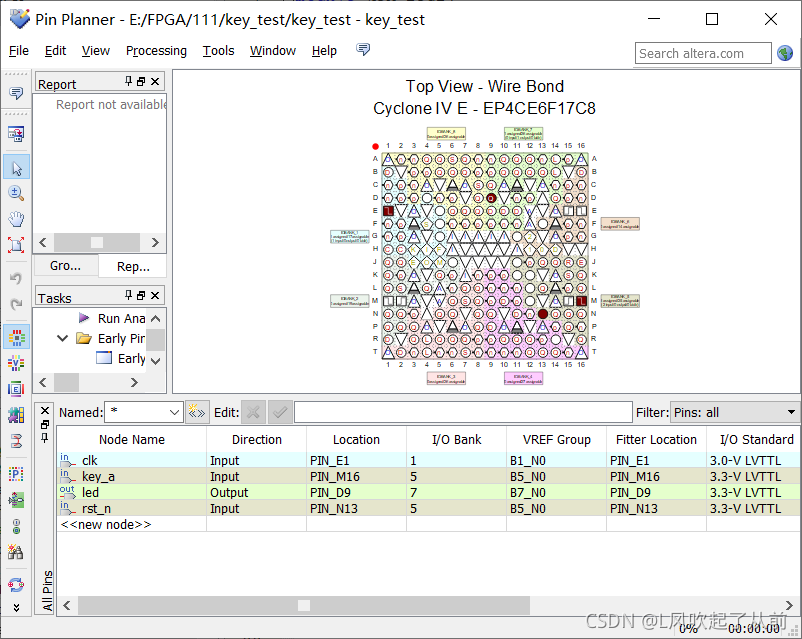

wire flag_key =key_tmb&(!key_tma);always@(posedge clk or negedge rst_n)if(rst_n == 1'b0)led <= 1'b1;else if(flag_key == 1'b1)led <= ~led ;elseled <= led ; endmodule引脚配置