并行通信是指数据的各个位用多条数据线同时进行传输

优点:传输速度快

缺点:占用引脚资源多

串行通信是将数据分成一位一位的形式在一条传输线上逐个传输

优点:通信线路简单、占用引脚资源少

缺点:传输速度慢

同步通信:带时钟同步信号的数据传输;发送方和接收方在同一时钟的控制下,同步传输数据。

异步通信:不带时钟同步信号的数据传输。发送方与接收方使用各自的时钟控制数据的发送和接收过程。

串行通信的传输方向:

单工 :数据只能沿一个方向传输

半双工:数据传输可以沿两个方向,但需要分时进行

全双工:数据可以同时进行双向传输

下面是常见的串行通信接口

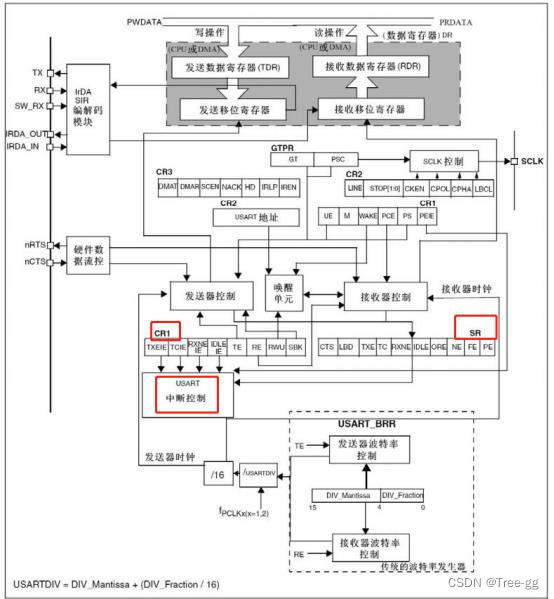

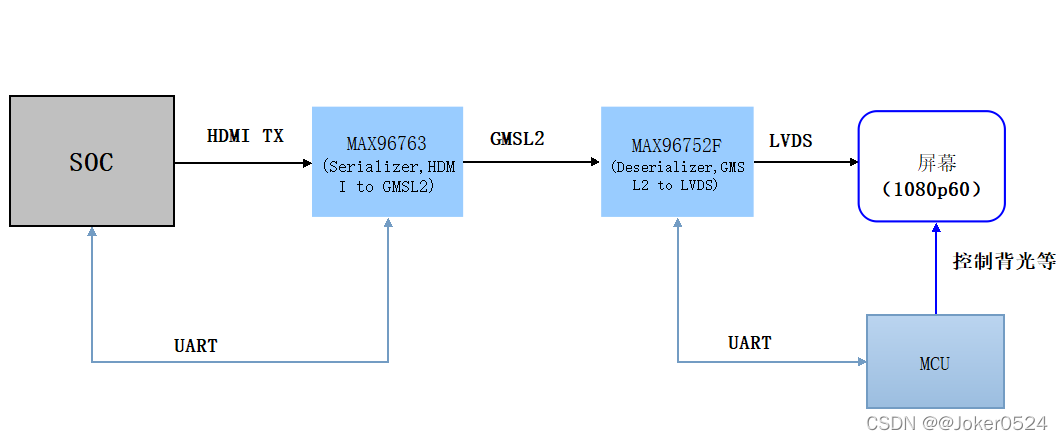

UART (universal asynchronous receiver-transmitter) 是一种采用异步串行通信方式的通用异步收发传输器。它在发送数据时将并行数据转换成串行数据来传输,在接收数据时将接收到的串行数据转换成并行数据。协议层: 通信协议(包括数据格式、传输速率等) 物理层:接口类型、电平标准等。

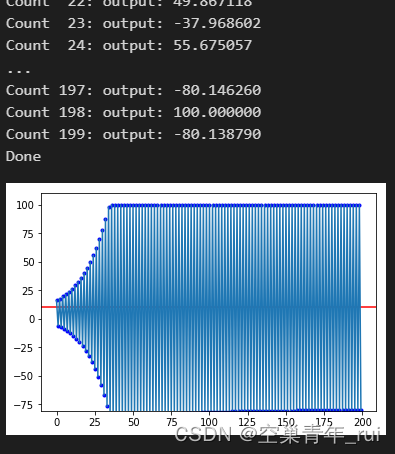

UART串口通信需要两根信号线来实现,一根用于串口发送,另外一根负责串口接收。

串口通信的速率用波特率表示,它表示每秒传输二进制数据的位数,单位是bps(位/秒) 常用的波特率有9600、19200、38400、57600以及115200等。

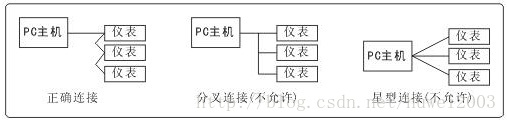

针对异步串行通信的接口标准有RS23、RS422、RS485等

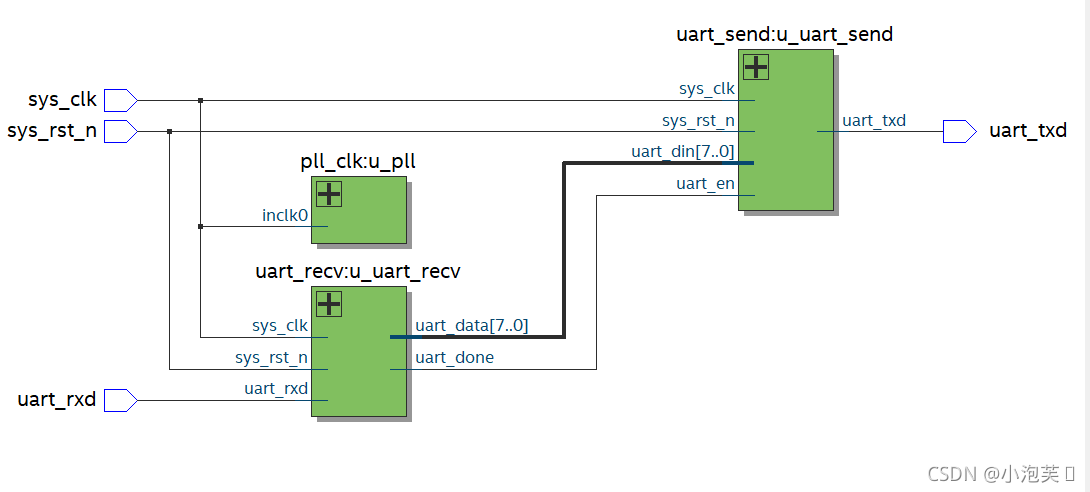

1.通信实验:开发板与上位机通过串口通信,完成数据环回实验

2.程序设计:

首先是分频时钟,用pll去设计ip核,输入时钟是50MHZ,输出一个时钟为1MHz,用于仿真。

具体ip核设计可以去看前面一篇文章:pll锁相环(可以根据系统时钟进行倍频、分频、相位偏移等等,而普通的计数器只能分频)_小泡芙❤的博客-CSDN博客

接收模块:

module uart_recv(input sys_clk, //系统时钟input sys_rst_n, //系统复位,低电平有效input uart_rxd, //UART接收端口output reg uart_done, //接收一帧数据完成标志信号output reg [7:0] uart_data //接收的数据);//parameter define

parameter CLK_FREQ = 50000000; //系统时钟频率

parameter UART_BPS = 9600; //串口波特率

localparam BPS_CNT = CLK_FREQ/UART_BPS; //为得到指定波特率,//需要对系统时钟计数BPS_CNT次

//reg define

reg uart_rxd_d0;

reg uart_rxd_d1;

reg [15:0] clk_cnt; //系统时钟计数器

reg [ 3:0] rx_cnt; //接收数据计数器

reg rx_flag; //接收过程标志信号

reg [ 7:0] rxdata; //接收数据寄存器//wire define

wire start_flag;//*****************************************************

//** main code

//*****************************************************

//捕获接收端口下降沿(起始位),得到一个时钟周期的脉冲信号

assign start_flag = uart_rxd_d1 & (~uart_rxd_d0); //对UART接收端口的数据延迟两个时钟周期

always @(posedge sys_clk or negedge sys_rst_n) begin if (!sys_rst_n) begin uart_rxd_d0 <= 1'b0;uart_rxd_d1 <= 1'b0; endelse beginuart_rxd_d0 <= uart_rxd; uart_rxd_d1 <= uart_rxd_d0;end

end//当脉冲信号start_flag到达时,进入接收过程

always @(posedge sys_clk or negedge sys_rst_n) begin if (!sys_rst_n) rx_flag <= 1'b0;else beginif(start_flag) //检测到起始位rx_flag <= 1'b1; //进入接收过程,标志位rx_flag拉高else if((rx_cnt == 4'd9)&&(clk_cnt == BPS_CNT/2))rx_flag <= 1'b0; //计数到停止位中间时,停止接收过程elserx_flag <= rx_flag;end

end//进入接收过程后,启动系统时钟计数器与接收数据计数器

always @(posedge sys_clk or negedge sys_rst_n) begin if (!sys_rst_n) begin clk_cnt <= 16'd0; rx_cnt <= 4'd0;end else if ( rx_flag ) begin //处于接收过程if (clk_cnt < BPS_CNT - 1) beginclk_cnt <= clk_cnt + 1'b1;rx_cnt <= rx_cnt;endelse beginclk_cnt <= 16'd0; //对系统时钟计数达一个波特率周期后清零rx_cnt <= rx_cnt + 1'b1; //此时接收数据计数器加1endendelse begin //接收过程结束,计数器清零clk_cnt <= 16'd0;rx_cnt <= 4'd0;end

end//根据接收数据计数器来寄存uart接收端口数据

always @(posedge sys_clk or negedge sys_rst_n) begin if ( !sys_rst_n) rxdata <= 8'd0; else if(rx_flag) //系统处于接收过程if (clk_cnt == BPS_CNT/2) begin //判断系统时钟计数器计数到数据位中间case ( rx_cnt )4'd1 : rxdata[0] <= uart_rxd_d1; //寄存数据位最低位4'd2 : rxdata[1] <= uart_rxd_d1;4'd3 : rxdata[2] <= uart_rxd_d1;4'd4 : rxdata[3] <= uart_rxd_d1;4'd5 : rxdata[4] <= uart_rxd_d1;4'd6 : rxdata[5] <= uart_rxd_d1;4'd7 : rxdata[6] <= uart_rxd_d1;4'd8 : rxdata[7] <= uart_rxd_d1; //寄存数据位最高位default:; endcaseendelse rxdata <= rxdata;elserxdata <= 8'd0;

end//数据接收完毕后给出标志信号并寄存输出接收到的数据

always @(posedge sys_clk or negedge sys_rst_n) begin if (!sys_rst_n) beginuart_data <= 8'd0; uart_done <= 1'b0;endelse if(rx_cnt == 4'd9) begin //接收数据计数器计数到停止位时 uart_data <= rxdata; //寄存输出接收到的数据uart_done <= 1'b1; //并将接收完成标志位拉高endelse beginuart_data <= 8'd0; uart_done <= 1'b0; end

endendmodule 发送模块

module uart_send(input sys_clk, //系统时钟input sys_rst_n, //系统复位,低电平有效input uart_en, //发送使能信号input [7:0] uart_din, //待发送数据output reg uart_txd //UART发送端口);//parameter define

parameter CLK_FREQ = 50000000; //系统时钟频率

parameter UART_BPS = 9600; //串口波特率

localparam BPS_CNT = CLK_FREQ/UART_BPS; //为得到指定波特率,对系统时钟计数BPS_CNT次//reg define

reg uart_en_d0;

reg uart_en_d1;

reg [15:0] clk_cnt; //系统时钟计数器

reg [ 3:0] tx_cnt; //发送数据计数器

reg tx_flag; //发送过程标志信号

reg [ 7:0] tx_data; //寄存发送数据//wire define

wire en_flag;//*****************************************************

//** main code

//*****************************************************

//捕获uart_en上升沿,得到一个时钟周期的脉冲信号

assign en_flag = (~uart_en_d1) & uart_en_d0;//对发送使能信号uart_en延迟两个时钟周期

always @(posedge sys_clk or negedge sys_rst_n) begin if (!sys_rst_n) beginuart_en_d0 <= 1'b0; uart_en_d1 <= 1'b0;end else begin uart_en_d0 <= uart_en; uart_en_d1 <= uart_en_d0; end

end//当脉冲信号en_flag到达时,寄存待发送的数据,并进入发送过程

always @(posedge sys_clk or negedge sys_rst_n) begin if (!sys_rst_n) begin tx_flag <= 1'b0;tx_data <= 8'd0;end else if (en_flag) begin //检测到发送使能上升沿 tx_flag <= 1'b1; //进入发送过程,标志位tx_flag拉高tx_data <= uart_din; //寄存待发送的数据endelse if ((tx_cnt == 4'd9)&&(clk_cnt == BPS_CNT/2))begin //计数到停止位中间时,停止发送过程tx_flag <= 1'b0; //发送过程结束,标志位tx_flag拉低tx_data <= 8'd0;endelse begintx_flag <= tx_flag;tx_data <= tx_data;end

end//进入发送过程后,启动系统时钟计数器与发送数据计数器

always @(posedge sys_clk or negedge sys_rst_n) begin if (!sys_rst_n) begin clk_cnt <= 16'd0; tx_cnt <= 4'd0;end else if (tx_flag) begin //处于发送过程if (clk_cnt < BPS_CNT - 1) beginclk_cnt <= clk_cnt + 1'b1;tx_cnt <= tx_cnt;endelse beginclk_cnt <= 16'd0; //对系统时钟计数达一个波特率周期后清零tx_cnt <= tx_cnt + 1'b1; //此时发送数据计数器加1endendelse begin //发送过程结束clk_cnt <= 16'd0;tx_cnt <= 4'd0;end

end//根据发送数据计数器来给uart发送端口赋值

always @(posedge sys_clk or negedge sys_rst_n) begin if (!sys_rst_n) uart_txd <= 1'b1; else if (tx_flag)case(tx_cnt)4'd0: uart_txd <= 1'b0; //起始位 4'd1: uart_txd <= tx_data[0]; //数据位最低位4'd2: uart_txd <= tx_data[1];4'd3: uart_txd <= tx_data[2];4'd4: uart_txd <= tx_data[3];4'd5: uart_txd <= tx_data[4];4'd6: uart_txd <= tx_data[5];4'd7: uart_txd <= tx_data[6];4'd8: uart_txd <= tx_data[7]; //数据位最高位4'd9: uart_txd <= 1'b1; //停止位default: ;endcaseelse uart_txd <= 1'b1; //空闲时发送端口为高电平

endendmodule 顶层模块

module uart_top(input sys_clk, //外部50M时钟input sys_rst_n, //外部复位信号,低有效//uart接口input uart_rxd, //UART接收端口output uart_txd //UART发送端口);//parameter define

parameter CLK_FREQ = 50000000; //定义系统时钟频率

parameter UART_BPS = 115200; //定义串口波特率//wire define

wire uart_en_w; //UART发送使能

wire [7:0] uart_data_w; //UART发送数据

wire clk_1m_w; //1MHz时钟,用于仿真调试//*****************************************************

//** main code

//*****************************************************

pll_clk u_pll( //时钟分频模块,用于调试.inclk0 (sys_clk),.c0 (clk_1m_w)

);uart_recv #( //串口接收模块.CLK_FREQ (CLK_FREQ), //设置系统时钟频率.UART_BPS (UART_BPS)) //设置串口接收波特率

u_uart_recv( .sys_clk (sys_clk), .sys_rst_n (sys_rst_n),.uart_rxd (uart_rxd),.uart_done (uart_en_w),.uart_data (uart_data_w));uart_send #( //串口发送模块.CLK_FREQ (CLK_FREQ), //设置系统时钟频率.UART_BPS (UART_BPS)) //设置串口发送波特率

u_uart_send( .sys_clk (sys_clk),.sys_rst_n (sys_rst_n),.uart_en (uart_en_w),.uart_din (uart_data_w),.uart_txd (uart_txd));endmodule 仿真模块

`timescale 1 ns/ 1 ns

module uart_top_tb();parameter T = 20;

reg sys_clk;

reg sys_rst_n;

reg uart_rxd;wire uart_txd;wire uart_en_w; //UART发送使能

wire [7:0] uart_data_w; //UART发送数据

wire clk_1m_w; reg uart_en; //发送使能信号

reg [7:0] uart_din; //待发送数据reg uart_done; //接收一帧数据完成标志信号

reg [7:0] uart_data; initial

begin sys_clk = 1'b0;sys_rst_n = 1'b0;uart_rxd = 1;#200 sys_rst_n = 1'b1;//模拟发送一帧数据#200 uart_rxd = 0; //起始位#110000 uart_rxd = 0; #110000 uart_rxd = 1; #110000 uart_rxd = 1; #110000 uart_rxd = 0; #110000 uart_rxd = 0; #110000 uart_rxd = 1; #110000 uart_rxd = 0; #110000 uart_rxd = 1; //停止位#1500000 $stop;end

always #(T/2) sys_clk = ~sys_clk; pll_clk u_pll( //时钟分频模块,用于调试.inclk0 (sys_clk),.c0 (clk_1m_w)

);u_uart_recv( .sys_clk (sys_clk), .sys_rst_n (sys_rst_n),.uart_rxd (uart_rxd),.uart_done (uart_en_w),.uart_data (uart_data_w));u_uart_send( .sys_clk (sys_clk),.sys_rst_n (sys_rst_n),.uart_en (uart_en_w),.uart_din (uart_data_w),.uart_txd (uart_txd));

endmodulertl图:

![[控制算法]](https://img-blog.csdnimg.cn/c0b83b286f664051b930b5519a7d5981.png)