voliate原理

voliate

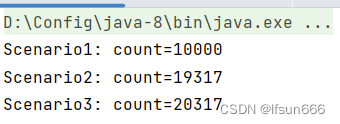

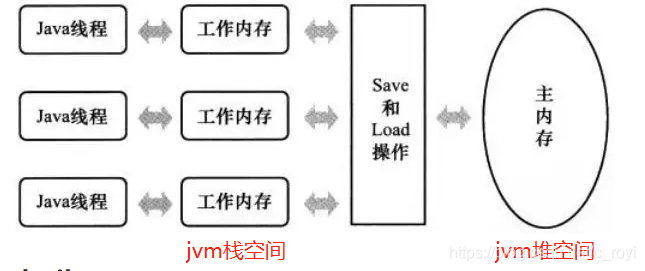

当使用voliate关键字修饰共享变量(实例变量、静态变量)时,它将具备两个特性:可见性和禁止指令重排序优化

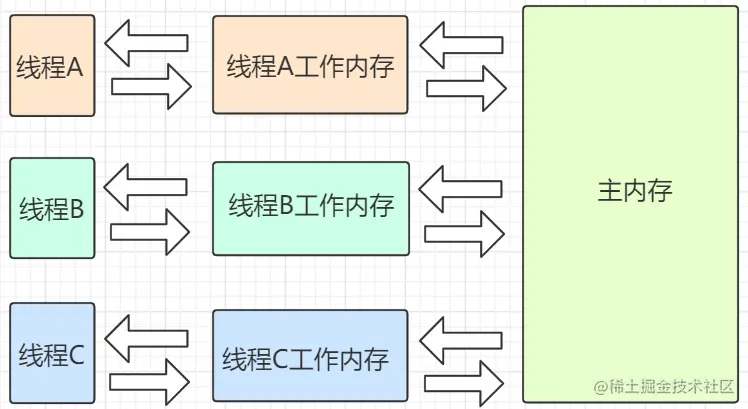

1.可见性

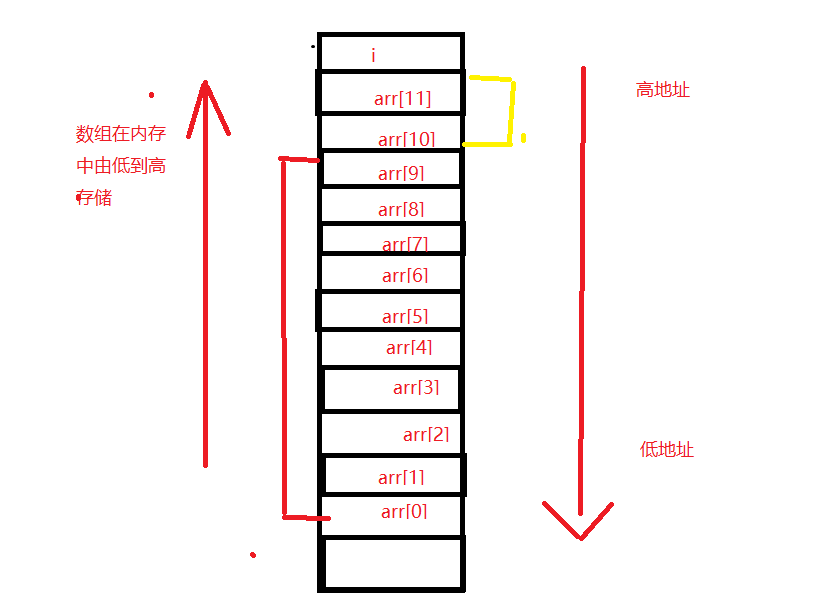

- 变量被修改后,会立即保存在主存中,并清除工作内存中的值。

- 新值对于线程来说都是可见的。

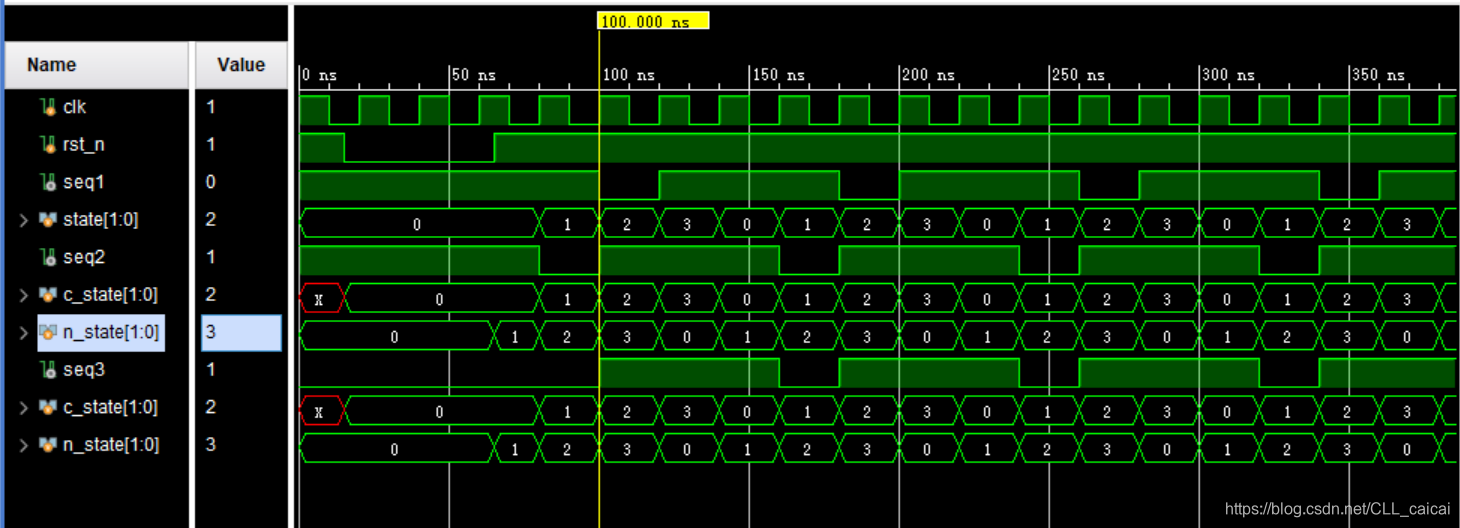

2.禁止指令重排序优化

指令重排序是指CPU在正确处理指令依赖(数据依赖)并且保障程序执行得到正确结果的情况下,调整代码的执行顺序,允许将多条指令不按照程序规定顺序分开发送给各相应电路单元处理。

- voliate禁止指令重排序是通过lock前缀指令实现的,lock前缀的指令相当于一个内存屏障,指令重排序时不能把后面的指令重排序到lock前缀指令之前,同时它会强制将对工作内存的修改操作立即写入主内存中。

使用条件

- 对变量的写不依赖当前值,或者确保只有一个线程修改其值。

- 该变量没有包含在具有其他变量的等式。