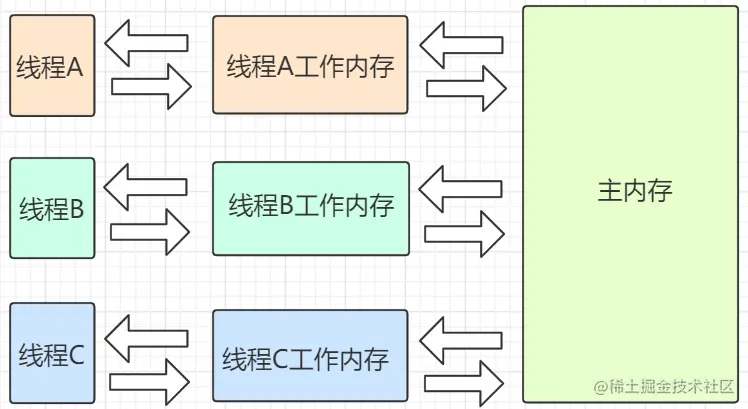

voliate的作用是作为指令关键字,确保本条指令不会因为编译器的优化而省略,而且要求每次从内存中直接读取值

当使用voliate 声明变量值时,系统总是重新从它所在的内存读取数据,直接访问变量地址,而编译器对于访问该变量时也不再进行优化

voliate关键字影响编译器的结果,用voliate 声明的变量表示该变量随时可能发生变化(因为编译器优化时可能将其放入寄存器中),与该变量有关的运算,不要再进行编译优化以免出错。

寄存器常用的优化方法:1.将内存变量缓存到寄存器中

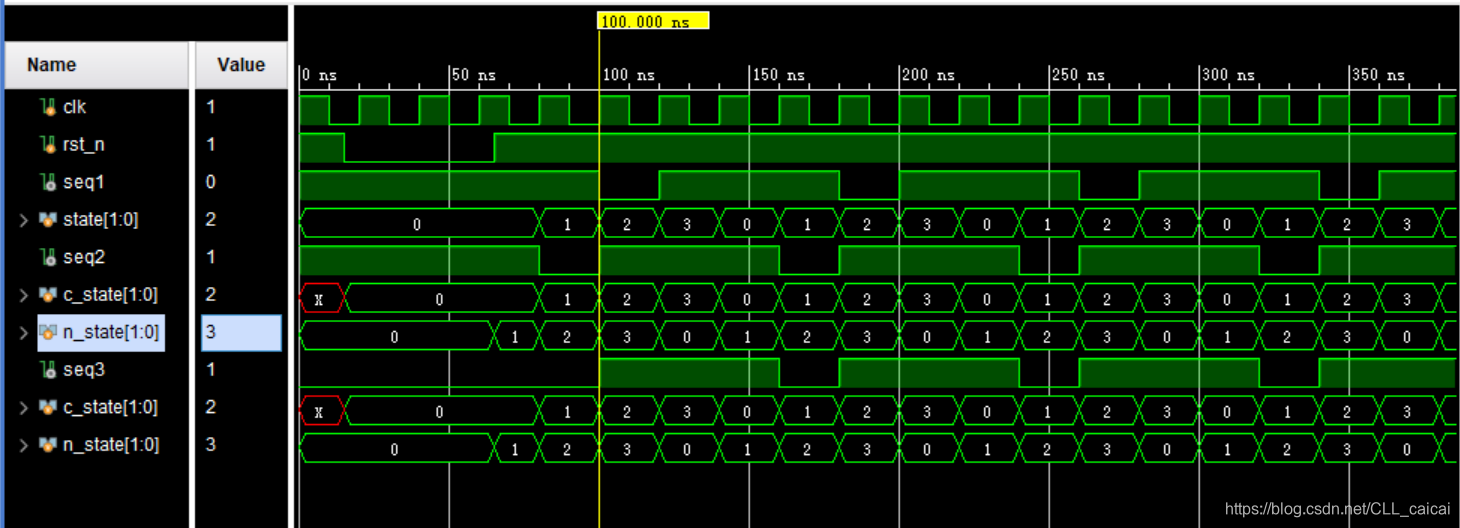

2.调整指令顺序,充分利用CPU指令流水线,进行指令重新排序读写指令。

下面来看一个程序

int main(){

int i = 0; int arr[] = { 1, 2, 3, 4, 5, 6, 7, 8, 9, 10 }; for (i = 0; i < 12; i++) { arr[i] = i; printf("hehe\n"); } return 0;

}

结果会是什么?出现了数组越界访问,程序还对吗?

但是在vs2013运行的结果却是死循环,为什么?

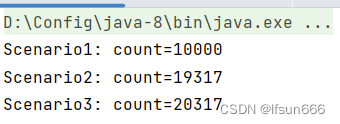

而且当我们将调试器换为release时竟然运行出来了12个hehe?!!

首先我们看看为什么会是循环

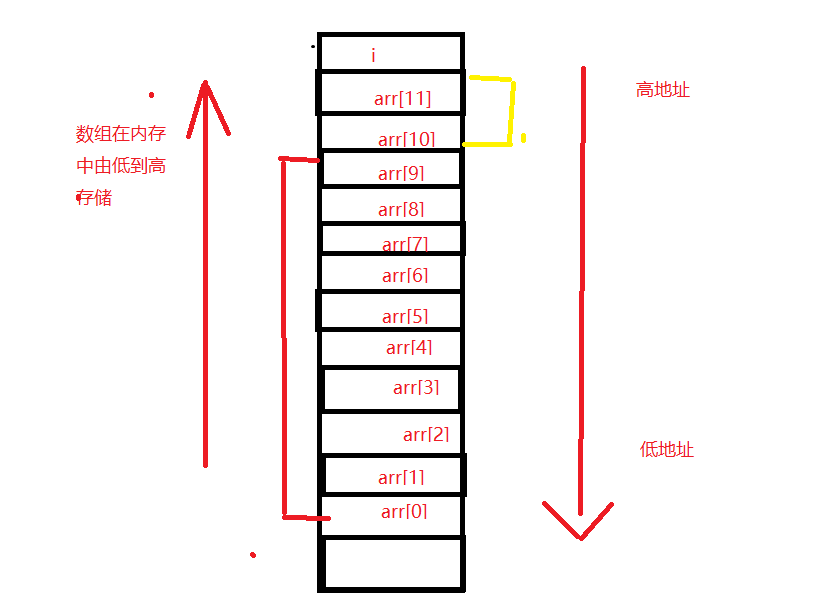

内存的存储中的存储是由高到低的

而数组则是由低到高的

当到arr[12]时arr[12]的地址又与i的地址相同了,i又被初始为零

在vs2013中有两个预留的间隔,而在vc6中只有一个预留的间隔所以编译器不一样结果也不一样

其次我们看看编译器是怎样优化

编译器 更改了指令的顺序,将i的初始时序放到了数组下面,避免了循环,这个可以在反汇编中查看