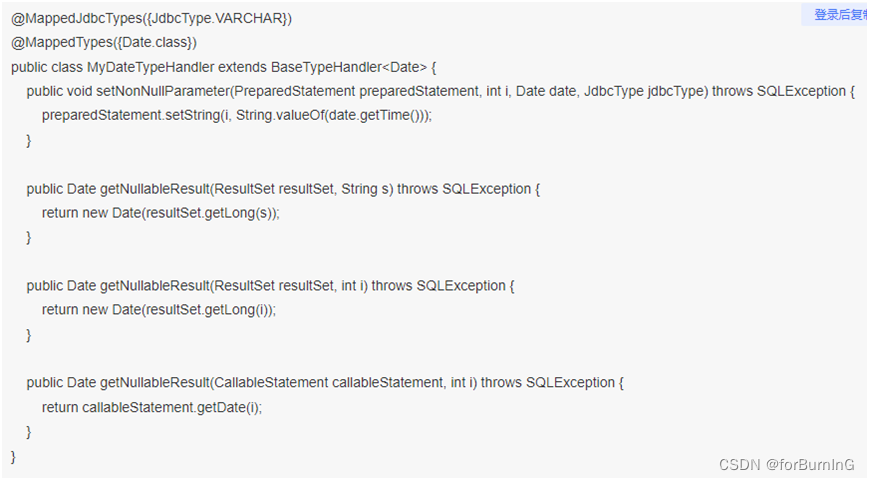

3段式状态机:

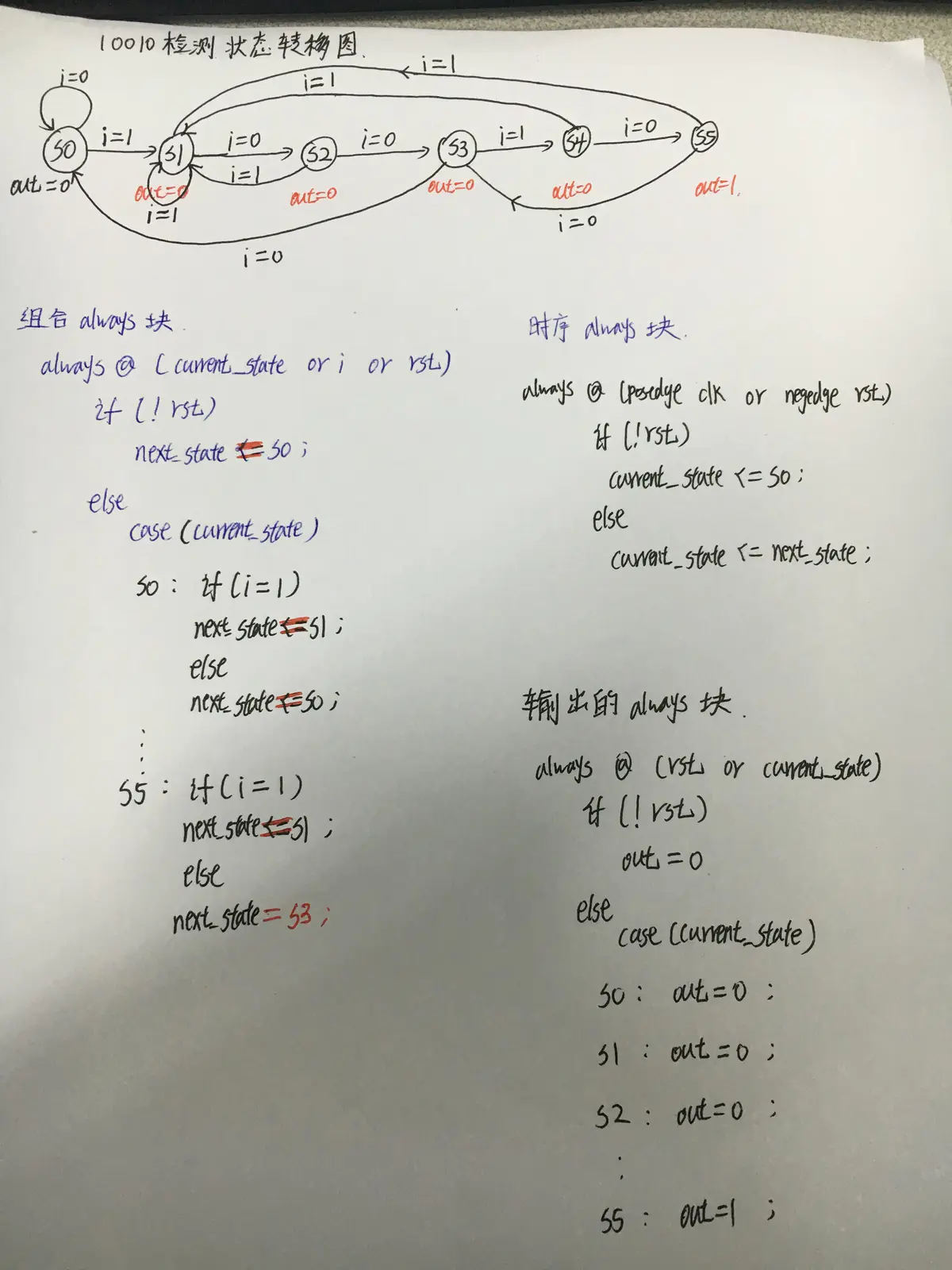

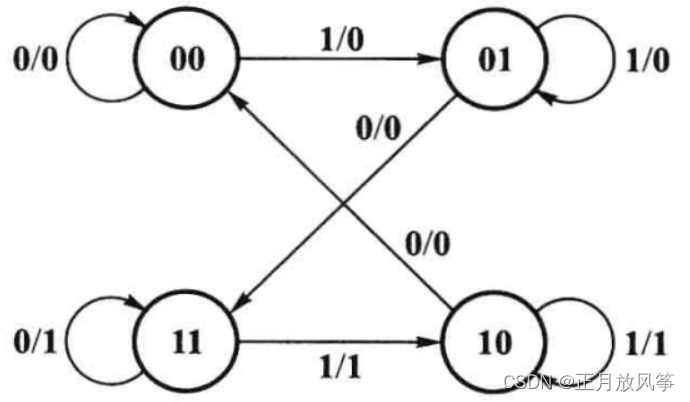

3段式状态机写法,写出下图状态转换图。

1 确定输入输出信号,及其类型(是wire还是reg);

2 声明内部信号,一般需要定义current_state和next_state;

3 用3个always语句描述状态机。第一个用来次态和现态的转换,第二个always用于现态在输入情况下转换为次态的组合逻辑;第三个语句用于现态到输出的组合逻辑输出。

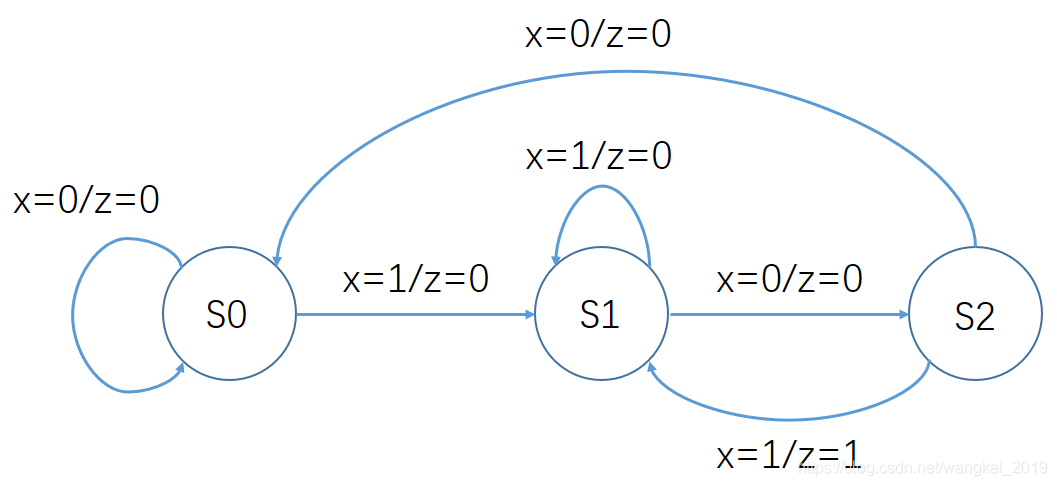

// 3段式状态机写法,写出上图状态转换图。

module finite_fsm(

output reg z_o,

input clk,

input Rst_n,

input w_i); // 输出端口,输入端口,和输出端口类型声明//参数声明

parameter IDLE = 2'b00;

parameter S0 = 2'b01;

parameter S1 = 2'b10;//内部信号声明

reg[1:0] current_state;

reg[1:0] next_state;// 时序逻辑 第1个always用来 时钟来时,转换次态和现态

always @ (posedge clk or negedge Rst_n) beginif(!Rst_n) // 复位current_state <= IDLE;elsecurrent_state <= next_state;

end// 次态的组合逻辑 第2个always 规定在有输入时转换为哪一个次态

always @ (w_i or current_state) begincase(current_state)IDLE:beginif(w_i) next_state = S0;else next_state = IDLE;endS0: beginif(w_i) next_state = S1;else next_state = IDLE;endS1: beginif(w_i) next_state = S1;else next_state = IDLE;enddefault : next_state = 2'bxx;endcase

end//输出逻辑 第3个always 规定在每个状态的输出

always @ (*) beigncase(current_state)IDLE: z_o = 1'b0;S0: z_o = 1'b0;S1: z_o = 1'b1;default: z_0 = 1'b0;endcase

end

endmoduleMoore状态机(输出与输入变量无直接关系)

米利状态机(输出与输入变量直接相关)

(1)一段式:整个状态机写到一个always模块里面,在该模块中既描述状态转移,又描述状态的输入和输出;

(2)二段式:用两个always模块来描述状态机,其中一个always模块采用同步时序描述状态转移;另一个模块采用组合逻辑判断状态转移条件,描述状态转移规律以及输出;

(3)三段式:在两个always模块描述方法基础上,使用三个always模块,一个always模块采用 同步时序 描述状态转移,一个always采用组合逻辑判断状态转移条件,描述状态转移规律,另一个always模块描述状态输出(可以用组合电路输出,也可以时序电路输出)。