| 芯片设计验证社区·芯片爱好者聚集地·硬件相关讨论社区·数字verifier星球 |

|---|

| 四社区联合力荐!近500篇数字IC精品文章收录! |

| 【数字IC精品文章收录】学习路线·基础知识·总线·脚本语言·芯片求职·EDA工具·低功耗设计Verilog·STA·设计·验证·FPGA·架构·AMBA·书籍 |

解读AXI协议乱序机制

- 一、写在前面

- 二、解读AXI协议的乱序机制

- 2.1 核心思想

- 2.2 信号列表

- 2.2.1 AXI3信号列表

- 2.2.2 AXI4信号列表

- 2.2.3 总结

- 2.3 传输顺序

- 2.3.1 读顺序

- 2.3.2 写顺序

- 2.3.3 读写操作的合作

- 2.4 互连线中ID信号的扩展

- 2.5 ID信号的位宽

- 2.6 总结

- 三、其他数字IC基础协议解读

- 3.1 UART协议

- 3.2 SPI协议

- 3.3 I2C协议

- 3.4 AXI协议

一、写在前面

AXI协议相较于UART,SPI,I2C来说,无论是内容还是难度都上了一个层级,放在一篇文章中进行解读未免篇幅过长,因此,有关AXI一些共性的、通用的问题,作者单独以前缀为【AXI】的标题进行小范围的串联,最终再汇总为深入浅出解读AXI协议,与从零开始的Verilog AXI协议设计,此为作者所思所考的推进顺序,单看【AXI】的每一篇,可能很多读者未免感到有些管中窥豹的疑惑,但若等作者更完此专栏再行观看,从头到尾进行阅读,应该就会有有茅塞顿开的收获与领悟。

二、解读AXI协议的乱序机制

2.1 核心思想

AXI协议中的乱序操作的本质,实际上是构建在Transaction ID这组信号的理解之上完成的,同时Transaction ID这组信号在AXI3与AXI4中的区别也很大,后文会提及。总而言之,通过加大设计上的实现难度,来支持AXI协议的乱序操作,增大面积的同时提高了操作效率,就是乱序操作的本质。

2.2 信号列表

2.2.1 AXI3信号列表

| Transaction通道 | Transaction ID |

|---|---|

| 写地址通路 | AWID |

| 写数据通路 | WID |

| 写回复通路 | BID |

| 读地址通路 | ARID |

| 读数据通路 | RID |

主设备提供的ID号:AWID,WID,ARID.

从设备提供的ID号:BID,RID.

2.2.2 AXI4信号列表

| Transaction通道 | Transaction ID |

|---|---|

| 写地址通路 | AWID |

| 写回复通路 | BID |

| 读地址通路 | ARID |

| 读数据通路 | RID |

主设备提供的ID号:AWID,ARID.

从设备提供的ID号:BID,RID.

2.2.3 总结

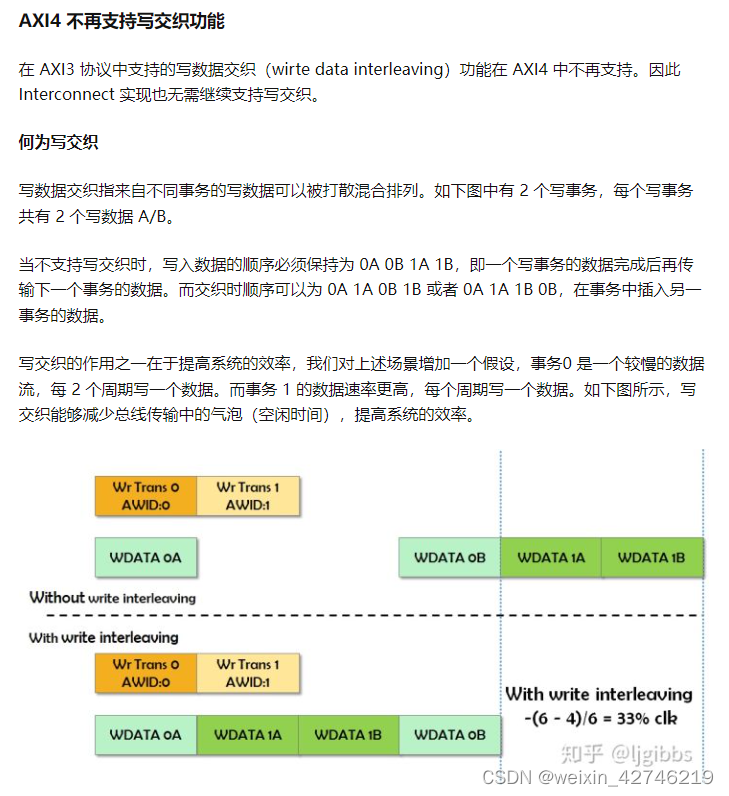

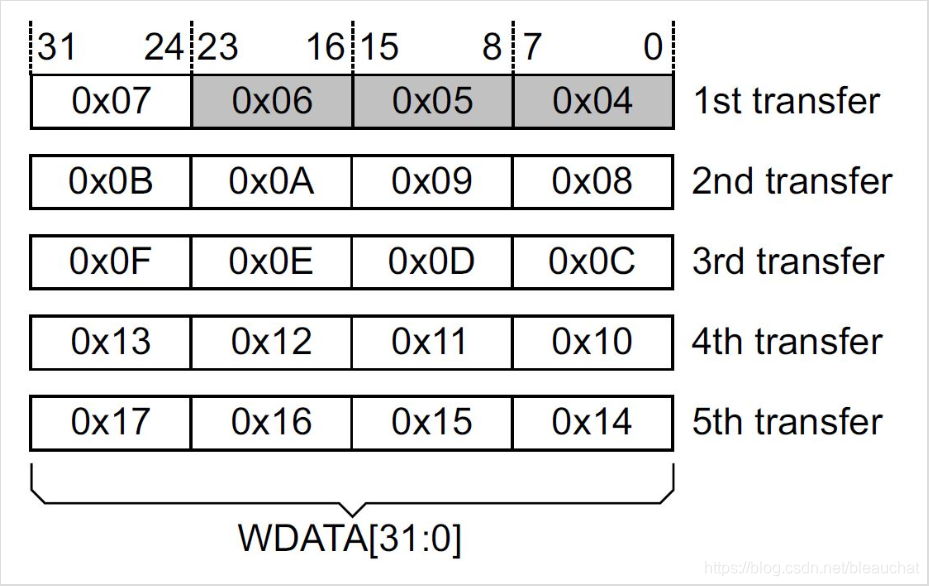

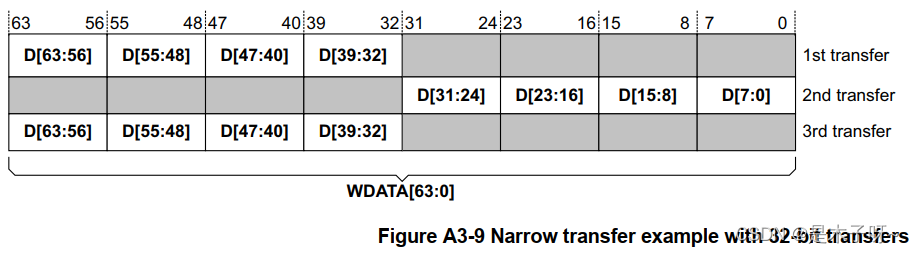

在AXI4中,比较AXI3和AXI4中我们可以发现ARM公司取消了写数据通路的ID信号WID,换言之,在AXI4中,设计者不需要考虑write interleaving的情况,什么叫write interleaving呢?

按照AXI3所言,每个transaction的写数据会有一个WID,不同WID的写数据transfer可以间插发送。但同一WID的写数据之间需要保序。

举例如下:假如transaction ID1有a和b两个transfer,写transaction ID2有c和d两个transfer,transaction1和2依次发送。

假如在支持write interleaving的情况下,实际的transfer顺序可以是a c d b / a b c d(在AXI3中不同WID的写数据transfer可以间插发送。但同一WID的写数据之间需要保序)

但是在AXI4中,transfer的顺序不能出现a c d b的这种情况(即取消了WID进而导致的取消了write interleaving的支持所产生的影响)

因为AXI3协议很老了,因此后文中我们默认还是更多侧重AXI4协议讲解AXI的乱序机制和原则

2.3 传输顺序

2.3.1 读顺序

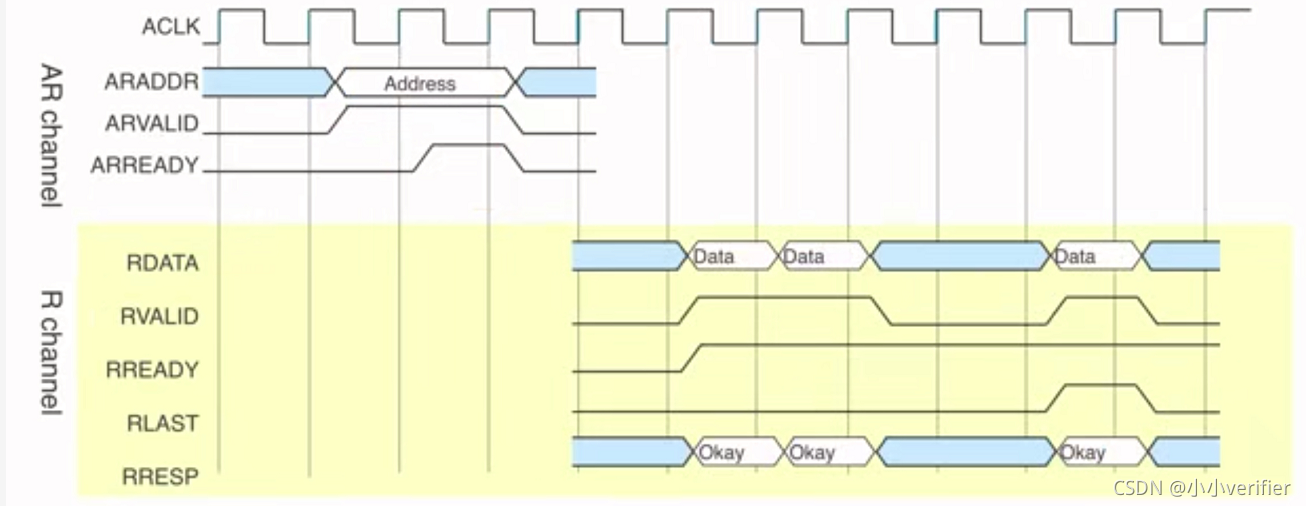

AXI的读顺序涉及到的信号为ARID和RID,ARID来自主设备,RID来自从设备,遵循的原则如下

- 对于主设备而言, 同一个ARID序号需要按照发射顺序返回读取的值,不同的ARID序号可以以任意顺序返回值,允许read interleaving。

- 对于从设备而言,同样执行“相同ARID顺序返回,不同ARID乱序返回的”原则

- 从设备控制的RID需要和主设备控制的ARID值相匹配

- 衡量从设备乱序能力的参数为“read data reordering depth”,这个参数代表从设备可以储存多少未执行待排序的命令,若从设备永远按顺序执行(非乱序),read data reordering depth的值为1.

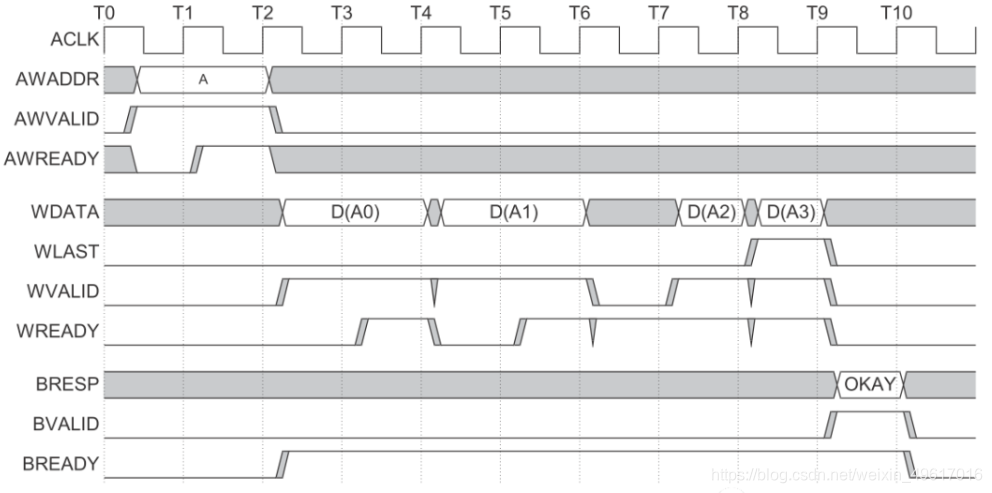

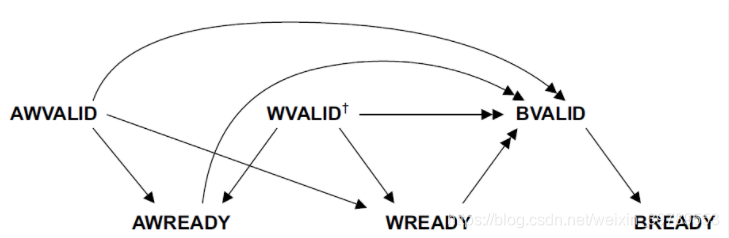

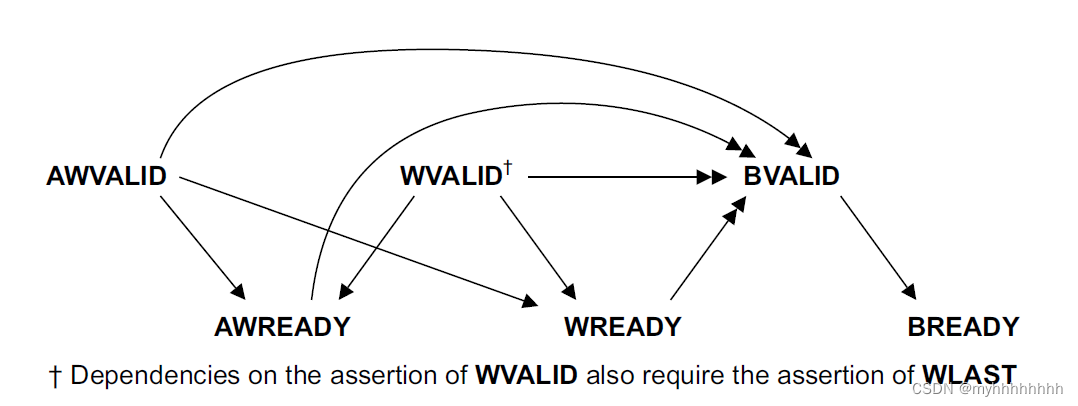

2.3.2 写顺序

AXI的读顺序涉及到的信号为AWID和BID,AWID来自主设备,BID来自从设备,遵循的原则如下

- 对于主设备而言, 同一个AWID序号需要按照发射顺序返回值,不同的AWID序号可以以任意顺序返回值(这里返回的值是指写回复通路中的ID信号和response信号),不允许write interleaving。

- 对于从设备而言,同样遵循相同AWID顺序,不同AWID乱序的原则

- 从设备BID需要匹配主设备的AWID

2.3.3 读写操作的合作

对于AXI协议而言,读写通路分离,因此从协议规定的层面上,没有读写传输之间的约束关系,无论ID编号是否相同,读写操作不需要遵循顺序关系,乱序即可。

对于不支持outstanding操作的主设备而言,要么发送读请求,要么发送写请求,必须确保前一个请求完成后才能发送后一个请求,遵循的原则如下

- 对于读transaction而言,接收到最后一个读数据意味着可以开始写transaction

- 对于写transaction而言,接收到写回复的时候意味着可以开始读请求

同时对于支持outstanding操作的主设备而言,每一次的读写transaction操作都需要比较地址是否有覆盖,只有当不同的transaction间地址不相同时,才可以在不等待前一个信号完成时发送新的信号。

原因:避免内存冲突的出现,outstanding下,transaction发送后默认是乱序执行的,假如outstanding中同时存在对相同地址的读写行为,先读后写和先写后读,读行为返回的值可能是不相同的,为了避免这种情况,在电路设计时,主设备transaction的发送需要比较是否有可能会造成冲突的地址信号。

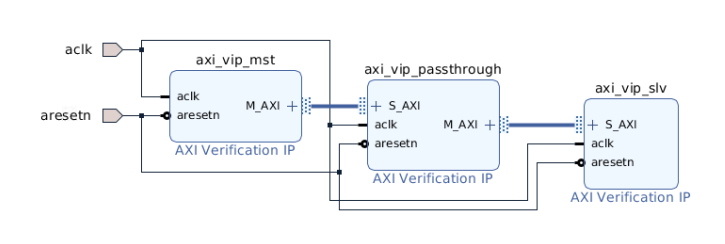

2.4 互连线中ID信号的扩展

当一个主设备连接到互联网络时,互联网络可以额外标记“ARID,AWID,WID(AXI4中WID取消)”。通过这种形式,主设备就不需要知道有哪些ID值被其他主设备使用(即主设备之间不需要沟通ID号的使用问题),互联网络可以独一无二的标记从不同主设备送出的Transaction ID号,从设备同理,RID和BID也可以在互联网络中也可以拥有一些额外的位,以此来确定读数据和写回复信号传输具体传输到哪一个主设备上,因此Transaction ID这个信号在主设备界面的位宽、实际网络中传输的位宽、从设备界面的位宽是有可能不一样的。

2.5 ID信号的位宽

协议中并没有规定Transaction ID的位宽是多少,但是推荐情况如下

- 主设备界面,Transaction ID为4 bits

- 经互连网络的标记和填充,Transaction ID扩展为8 bits(4 bits额外)

- 从设备界面,Transaction ID为经互联网络扩展后的8 bits(默认4 bits,经扩展8 bits)

以上为推荐值,无规定值

2.6 总结

通过Transaction ID这组信号,AXI4协议可以完成自身的乱序机制,从AXI3到AXI4的进化中,write interleaving被取消了,大的方向下,AXI遵循着相同ID顺序执行,不同ID乱序执行的原则,同时从主设备-互联网络-从设备的连接中,Transaction ID可能会出现额外的位扩展。在原版的协议中,除了从读写行为的乱序模型分析外,还通过主从设备的角度讲述乱序模型的规定和原则,感兴趣的读者可自行阅读。

三、其他数字IC基础协议解读

3.1 UART协议

- 【数字IC】深入浅出理解UART

- 【数字IC】从零开始的Verilog UART设计

3.2 SPI协议

- 【数字IC】深入浅出理解SPI协议

- 【数字IC】从零开始的Verilog SPI设计

3.3 I2C协议

- 【数字IC】深入浅出理解I2C协议

3.4 AXI协议

- 【AXI】解读AXI协议双向握手机制的原理

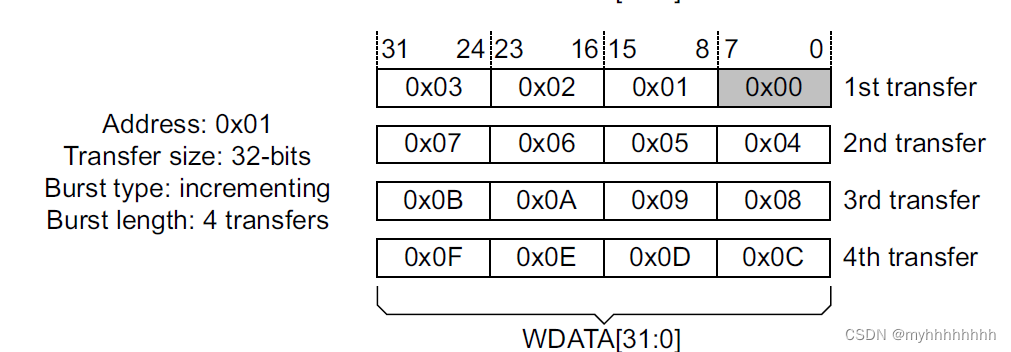

- 【AXI】解读AXI协议中的burst突发传输机制

- 【AXI】解读AXI协议事务属性(Transaction Attributes)

- 【AXI】解读AXI协议乱序机制

- 【AXI】解读AXI协议原子化访问

- 【AXI】解读AXI协议的额外信号

- 【AXI】解读AXI协议的低功耗设计

- 【数字IC】深入浅出理解AXI协议