提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档

一、AXI中关于非对齐问题理解

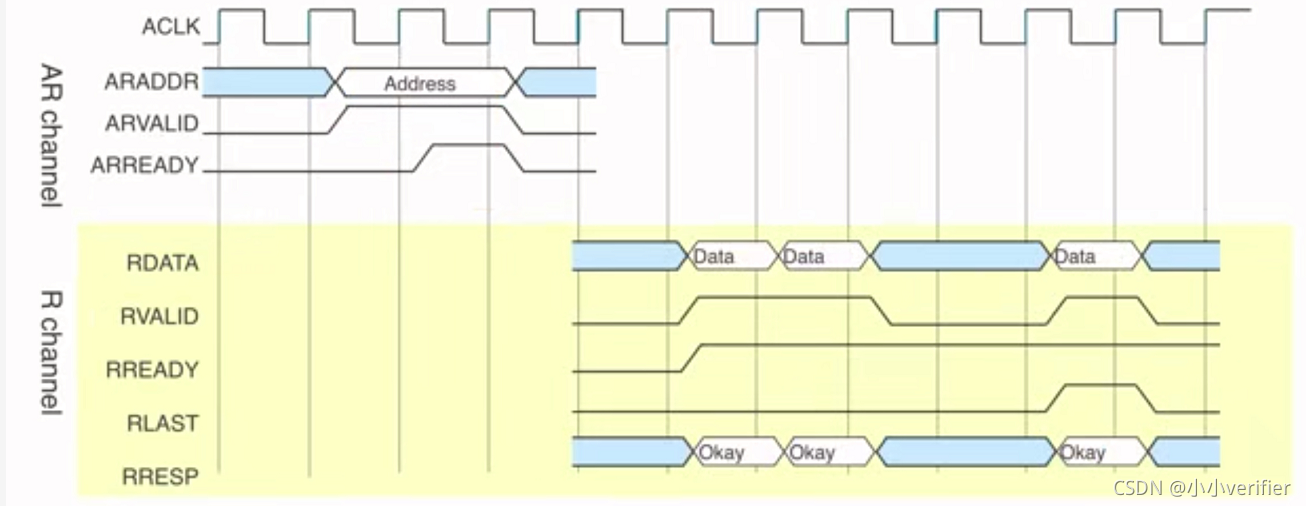

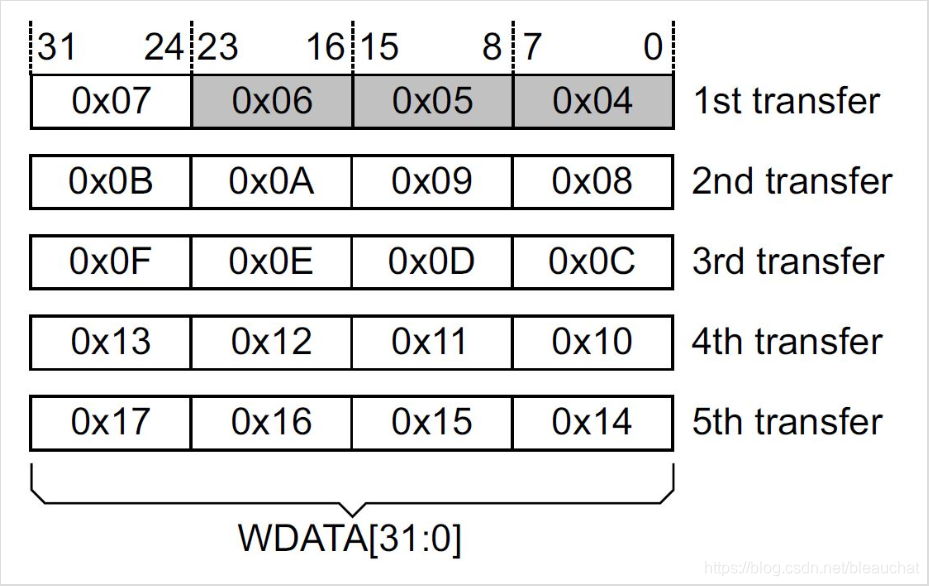

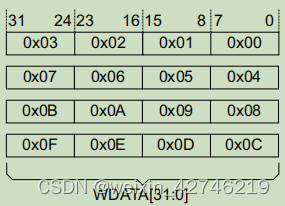

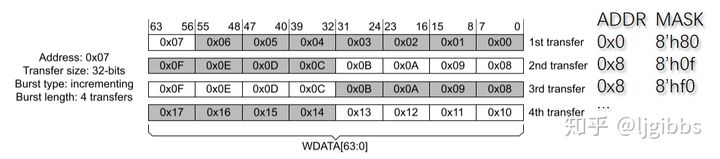

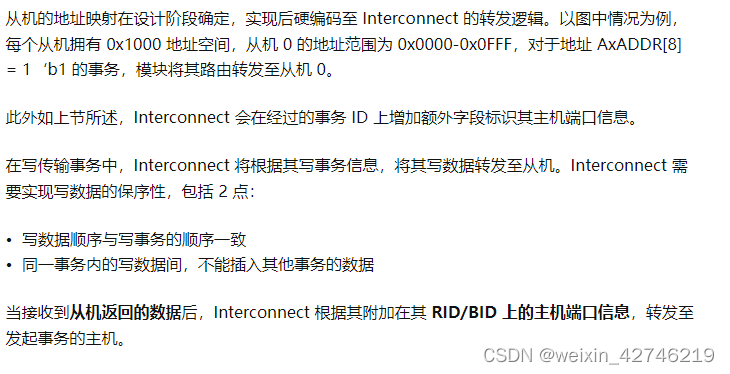

AXI 协议支持地址非对齐的传输,允许突发传输的首字节地址,即起始地址与突发传输位宽不对齐。举个例子,总线位宽为 32bit 时,如果起始地址为 0x1002 ,则产生了非对齐现象。与16bit 位宽总线对齐的地址需要能被 2 整除;与 32bit 位宽总线对齐的地址需要能被 4 整除;与 64bit 位宽总线对齐的地址需要能被 8 整除。如下图所示:(32位数据的对齐图)

对于非对齐传输,主机会进行两项操作:

1.即使起始地址非对齐,也保证所有传输是对齐的。

2.在首个 transfer 中增加填充数据,将首次传输填充至对齐,填充数据使用 WSTRB 信号标记为无效。

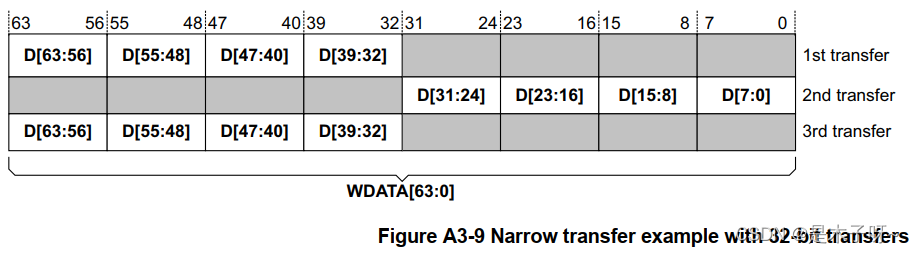

注意:此处对齐与否应该取决于突发传输的宽度,而不是总线位宽。例如下图所示:

这个例子是窄传输+非对齐传输。数据总线位宽为64bit,但是突发传输的数据位宽为32bit,起始地址为0x07,首先将首个传输填充至与突发传输位宽 32 bit对齐,即填充3字节(0x06~0x04),至此非对齐的问题就已经解决了。接下问题就简化为窄传输,在 transfer 1st 中 再填充 4 个字节(0x03~0x00)。

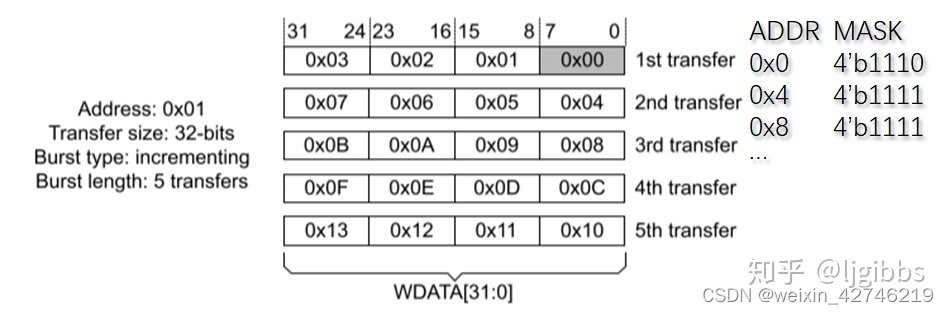

如下图所示:

起始地址为 0x1,非对齐,但主机通过添加一字节的填充数据将 transfer 1st 的实际地址调整为对齐的 0x0,并用 WSTRB 信号为 4'b1110 标识出最低字节上无效的填充数据。相当于第一tansfer中WDTA[31:0]中低8位数据是主机自行填充的无效数据,然后再加上原本主机需要传输的前三个字节的数据,这样就构成了4字节的传输发送给从机,从机在接收后通过WSTRB信号识别出低8位无效,然后将WDATA中[8:31]位数据即0x01,0x02,0x03存入相应的地址中去。那么在接下来的tansfer中32位总线宽度的数据就从0x04地址开始传输了,相当于将原来不齐的地址传输变成对齐传输。

二、实现细节

1. 协议建议 AW/AR READY 信号,的默认电平为高电平。若默认电平为低,则每次传输至少需要 2 个周期才能完成,第一个周期置高 VALID 信号,第二个周期从机才会置高 READY 信号。相当于每次传输增加 1 个周期时间开销,这在某些情况下会对传输效率有较大的影响。

2. 写数据通道拥有STROBE字节选通信号,而都通道中没有,用于标识写数据中有效的传输字节。

3. 写数据通道设计有缓存,可超前于从机响应本次传输操作,发起下一次写传输操作。缓存能力是视情况而定的。当缓存能力用尽,从机会置低 ready 信号。例如:outstanding模式。

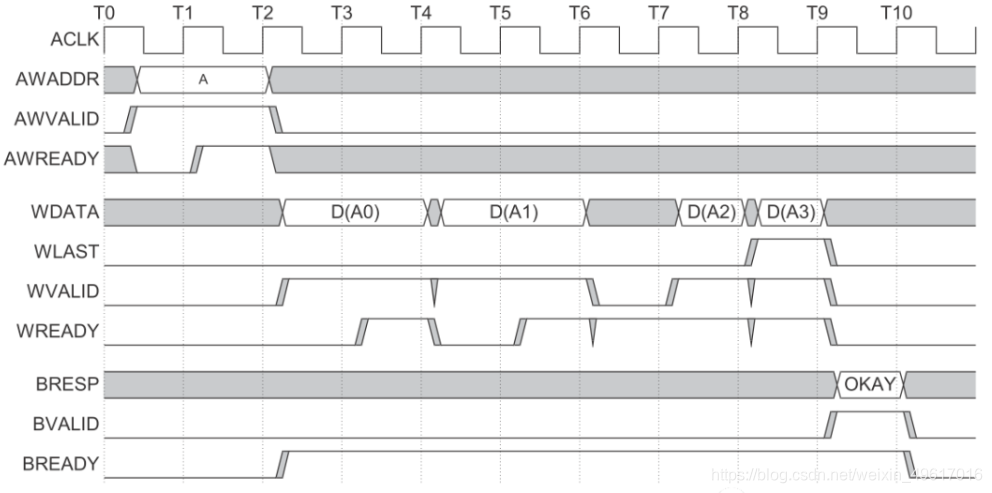

4. 所有写传输操作都需要以写回复通道上接收写响应作为完成信号。再次强调,写回复是针对一次传输操作(transcation)的,而不是针对每一次写数据(data transfer)。

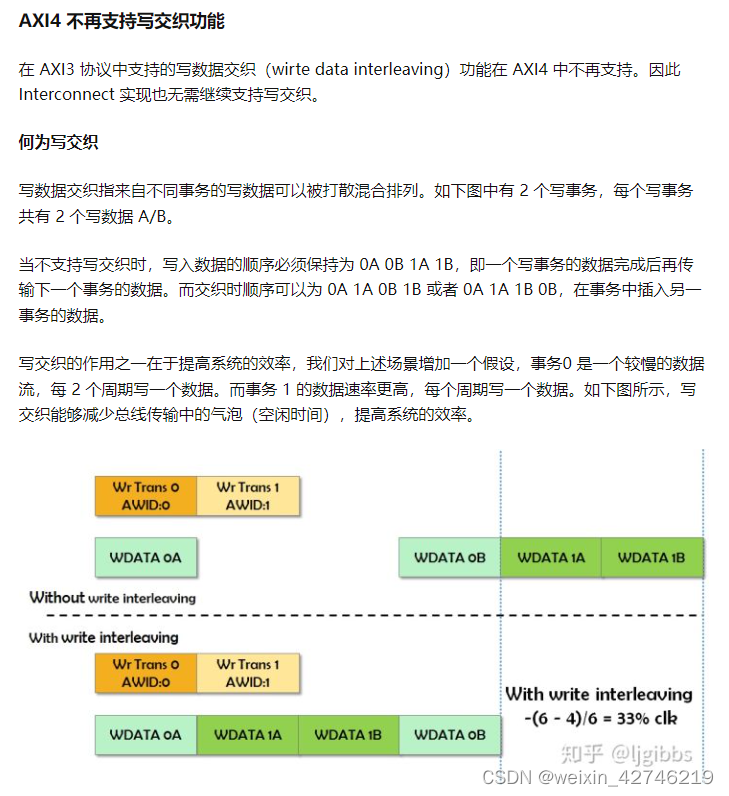

5. AXI4 不再支持 WID 信号,这和 AXI4 的乱序机制有关,AXI4 规定所有数据通道的数据必须顺序发送。

6. 一般情况下 AXI 的五个通道之间是独立的。但凡事都免不了例外,是吧。AXI 的通道间需要保证以下三种联系(relationship):

1)写回复必须在其所属传输的最后一个写数据完成后。

2)读数据必须在接收到读地址信号后产生

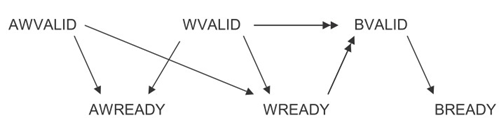

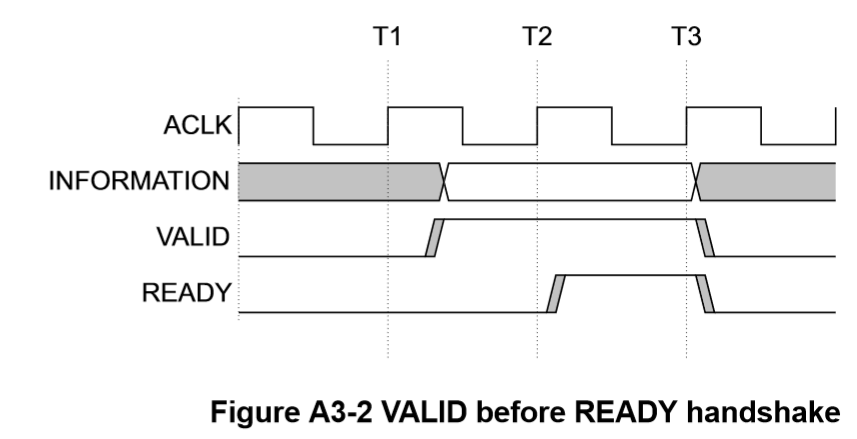

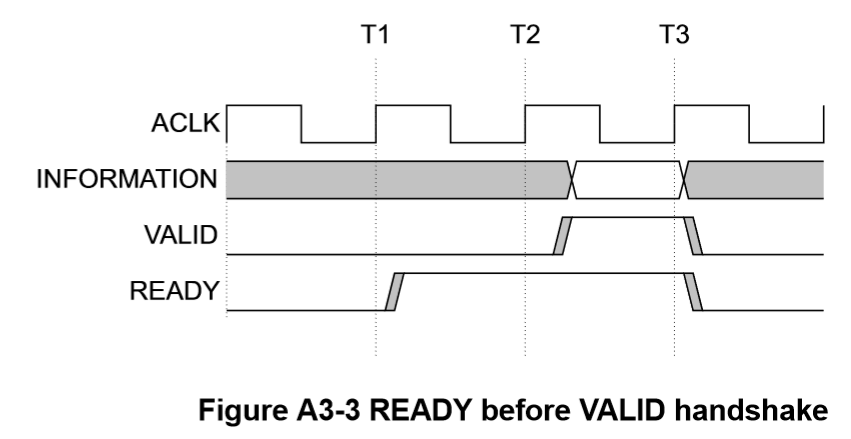

3)通道间的握手需要满足通道间的握手依赖性,握手依赖的目的是为了防止死锁,例如:发送方的 VALID 一定不能依赖接收方 READY 信号;接收方 READY 信号可以检测到 VALID 置起后再置起有效,换句话说,可以依赖 VALID 信号。

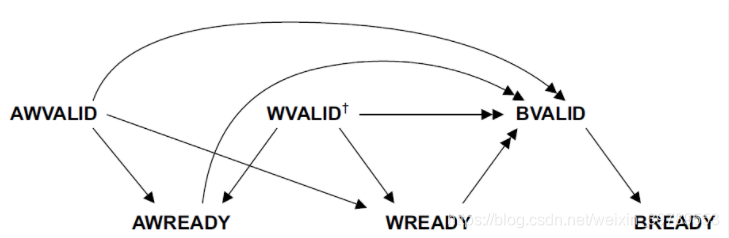

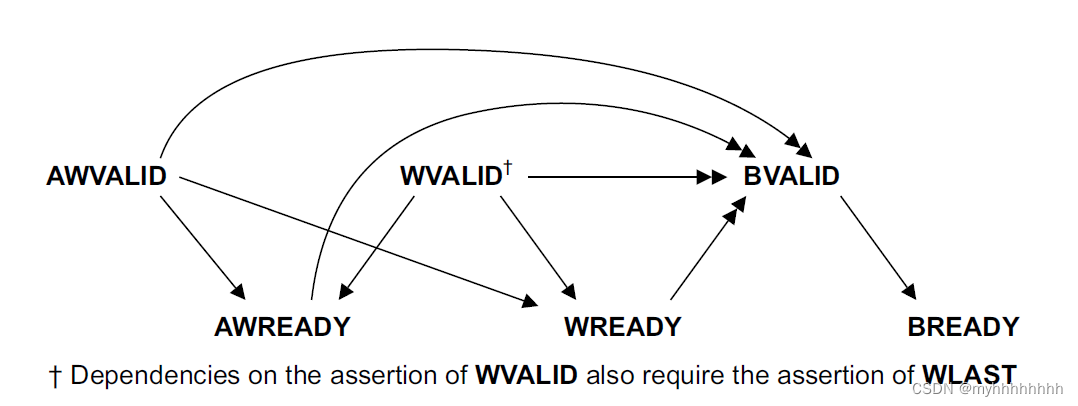

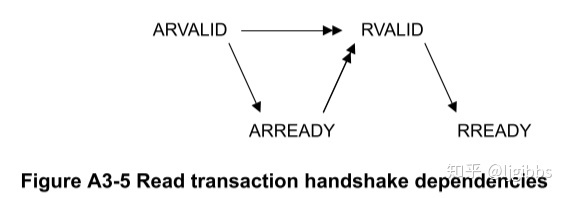

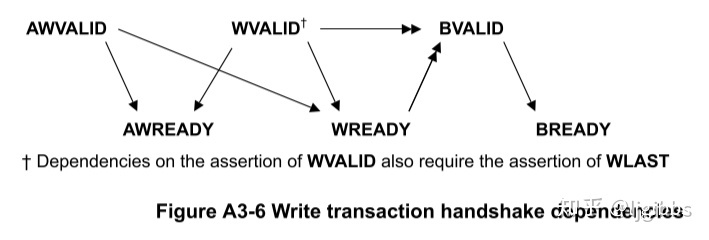

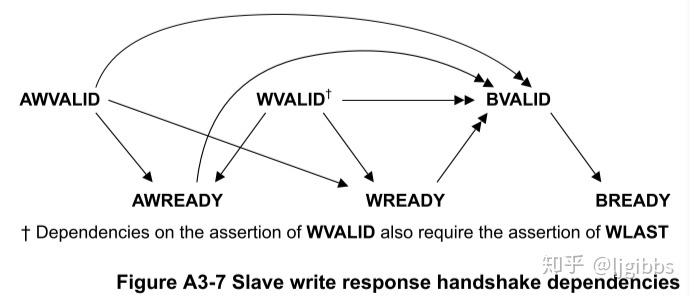

图中的单头箭头表示:其指向的信号可以在箭头起始信号置起之前或之后置起(无依赖)

图中的双头箭头表示:其指向的信号必须在箭头起始信号置起之后置起(指向信号依赖起始信号)

读传输情况:

写传输情况:

注意:别忽略WLAST和RLAST信号。

在 AXI4 中,写传输相较此前增加了从机置起 BVALID 信号所需的依赖。如下图所示:

注意:

AXI 协议并没有对写数据以及写地址通道中的握手信号先后顺序做出规定。因此,实现中数据可以先于地址完成握手。这适用于一些情况,手册中举了个例子,比如写地址通道为了满足时序,触发器的级数与写数据通道不同,这样一来两通道握手的先后顺序可能不同。

这反映了 AXI 通道间的独立性,利用该特性可调整路径中的触发器,满足时序约束。

7. 在 AXI 传输事务(Transaction)中,数据以突发传输(Burst)的形式组织。一次突发传输中可以包含一至多个数据(Transfer)。每个 transfer 因为使用一个周期,又被称为一拍数据(Beat)。

8. 注意:单次 burst 传输中的数据,其地址不能跨越 4KB 边界。

协议中之所以规定一个burst不能跨越4K边界是为了避免一笔burst交易访问两个slave(每个slave的地址空间是4K/1K对齐的);4K对齐最大原因是系统中定义一个page大小是4K,而所谓的4K边界是指低12bit为0的地址。

9. 对于 WRAP 模式,突发传输长度仅能为2,4,8,16

10. 一次突发传输不能在完成所有数据传输前提前结束(early termination);在写传输事务中,发送方可以通过置低所有的写有效位,使写数据无效。在读传输事务中,主机可以直接丢弃读取到的数据

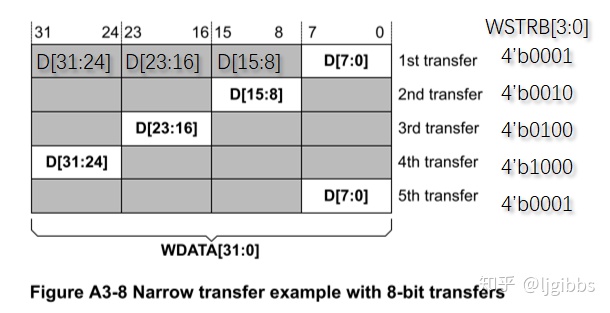

11. 当本次传输中数据位宽小于通道本身的数据位宽时,称为窄位宽数据传输(Narrow Transfer),窄位宽数据传输中主机需要告知从机数据通道中哪些字节是有效的,需要使用到写数据通道中的 WSTRB 信号。

12. 当主机是因为从机或者其他客观条件限制,需要进行窄传输时,可以一次性将数据放置于数据总线上,只需在每次传输期间改变 WSTRB 信号即可。如下图所示:主机将 D[31:0] 防置于总线,在接下来的四个周期中,仅需对 WSTRB 进行移位,即可依次完成 4 个字节的传输。

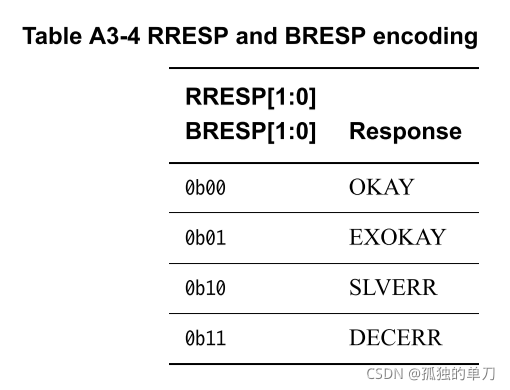

13. 注意:在写传输事务中,单个写回复(WRESP)针对的是整个 burst,而不是 burst 中单个 transfer。但是在读传输事务中,从机可以为突发传输中每一个读传输数据产生不同的读回复信号(RRESP)。

单机多事务场景

超前传输(outstanding transaction)特性是 AXI 总线能够实现高性能传输的原因之一。

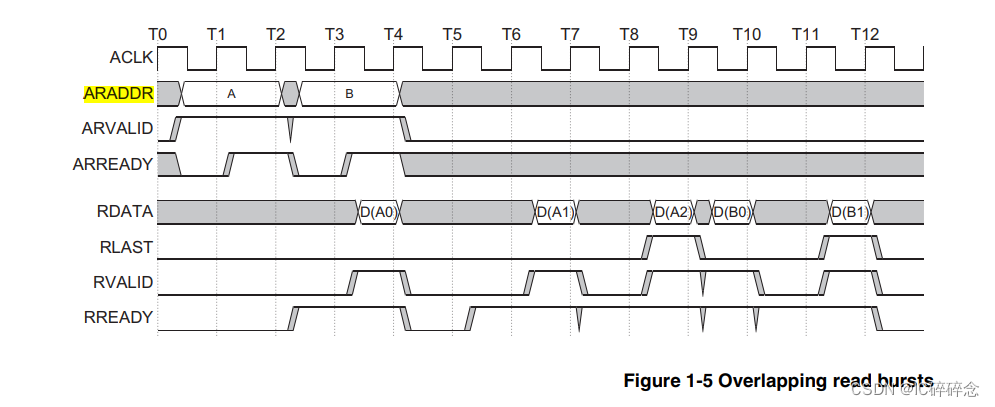

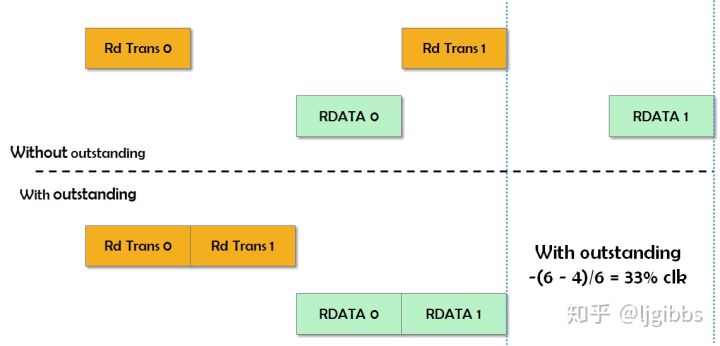

主机在当前传输事务完成前,就可以开始下一个传输事务。因此系统中可能存在多个进行中的传输事务。假设多个事务能够被从机并行处理,可提高系统的性能。下图基于场景 A,举了一个超前读传输事务的例子。

其中假设从机在接收到读传输事务后,需要 1 个周期来准备读数据,每个事务仅包括一个 transfer。称为例 A0。

在未进行超前传输的场景下,主机发出传输事务后,等待从机返回数据后,再开始下一次传输。显然,超前传输在该场景中能够减少 33% 的传输时间。

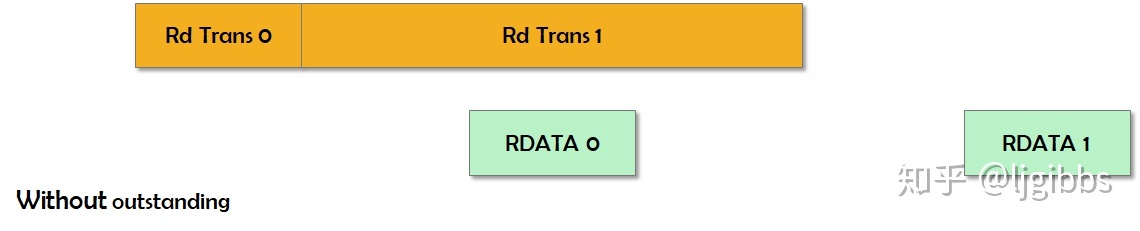

AXI 从机可选地支持超前传输,假设从机不支持超前传输,只需要在接收到 Trans0 后,置低 AxREADY 信号,阻止主机超前传输。在返回读数据后,再置高 AxREADY 信号,接收下一事务。如下图所示,主机将 Trans1 保持在总线上直至从机接收。

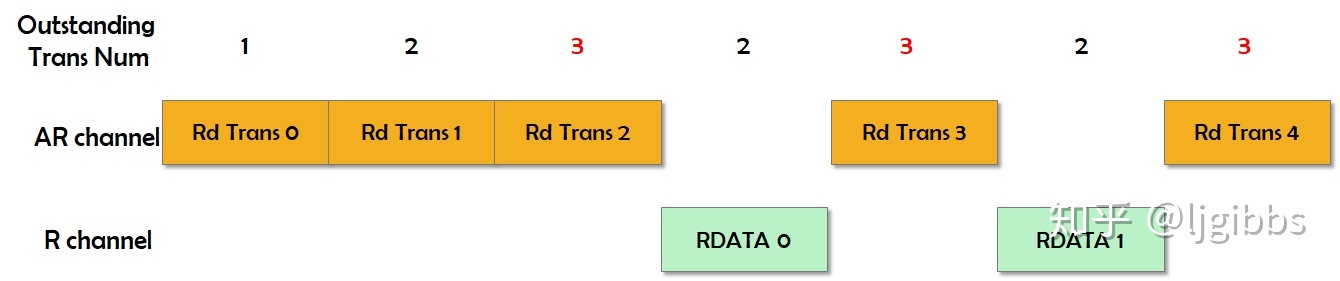

使用超前传输深度(outstanding depth)这一指标,衡量一个主机超前传输的能力,表示主机正在进行中的(在途的)事务数量。下图中的主机最多共有 3 个事务在途,在有事务结束后才会发出新事务。

更大的超前传输深度需要主机准备更大的缓存区用于保存在途事务的信息,并接收缓存读数据。通过较大的超前传输深度能够提高系统的性能。

多事务乱序

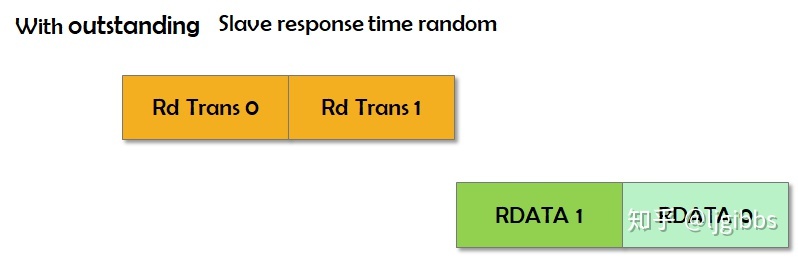

假设从机对不同传输事务准备读数据的周期不同,比如从机对于事务 0 的准备时间是 2 个周期,而对于事务 1 不需要准备周期,这样一来会造成下图中的情况,称为例 A1。

假设从机一旦数据就绪就会发送,上图中事务 1 的数据 RDATA1 率先于 RDATA0 就绪并发送,主机会产生困扰:先返回的是哪个事务的数据。

当从机对每个事务的处理时间一致时,主机可以通过顺序关系判断数据所属的事务。

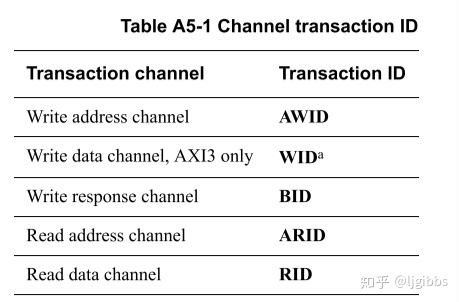

但是一般从机的数据准备时间不由主机控制,数据就绪顺序与事务到达顺序不一致是可能的。因此超前传输需要相应的机制来标识数据所属的事务。AXI 协议在各通道设计了 ID 信号,如下图所示。其中 WID 信号在 AXI4 中被取消,这点会在后续的文章中详细讨论。根据 ID 信号发送方不同,4 个 ID 信号可划分为:

- 主机制定并发送:AWID ARID,用于标识传输事务

- 从机制定并发送:RID BID,用于标识数据或者回复,代表传输事务完成

首先从读事务的 ARID 来看,主机为发出的读事务设定 ARID。

(1)协议规定,对于 ARID 一致的多个事务,从机必须按照接收事务的顺序,返回其读数据。

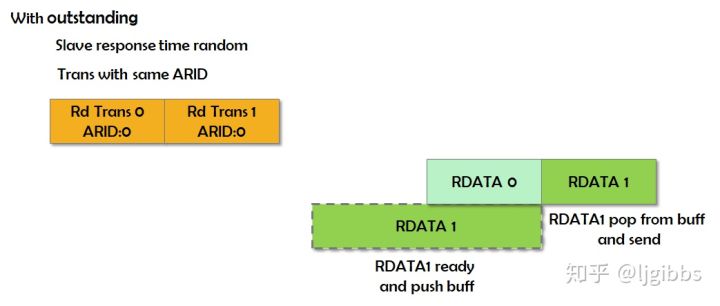

注意: 实现中可以为每个 ARID 维护一个缓冲区用于维护读数据的顺序。基于上述的例 A1,假设主机发出的两个事务 ARID 一致,则出现下图中例 A2 的场景。

第二个事务的 RDATA1 在就绪后进入重排序缓存(reorder buff)等待,在 RDATA0 发出后从缓存中读取发送。

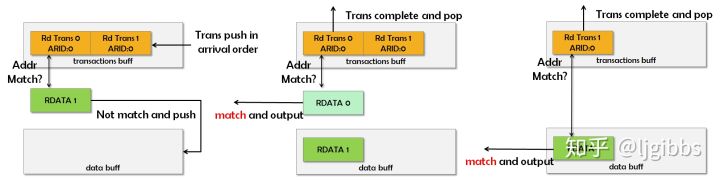

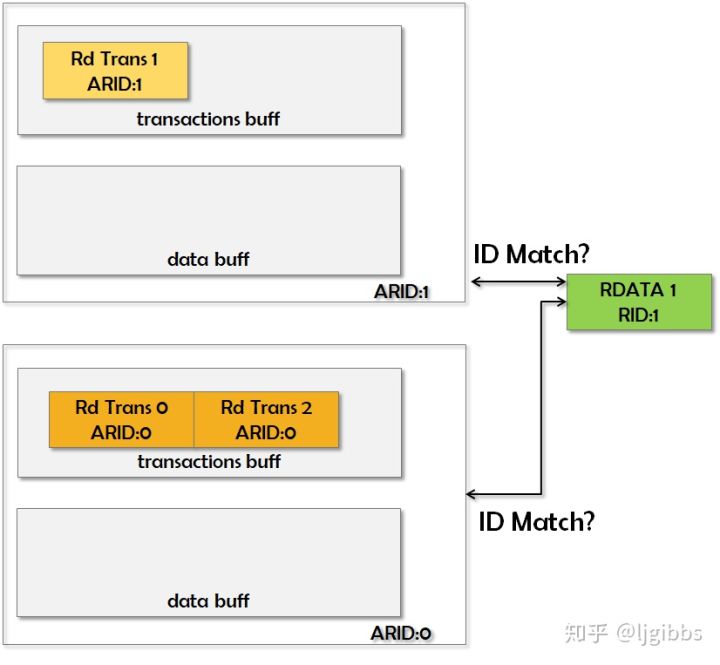

AXI 的传输顺序要求从机实现重排序缓存以及机制,下图是一个笔者设计的重排序实现模型。

重排序模型包括两个缓存区:事务缓冲区与数据缓冲区。事务缓存区按照到达顺序存放读事务,就绪的数据与缓冲区中首个事务比较,若地址匹配则直接输出,否则进入数据缓存区。

当事务所有的传输完成后,从缓冲区中清除。

重排序缓存区的大小,即重排序深度,在设计阶段决定,协议不支持主机对从机重排序深度的调整。

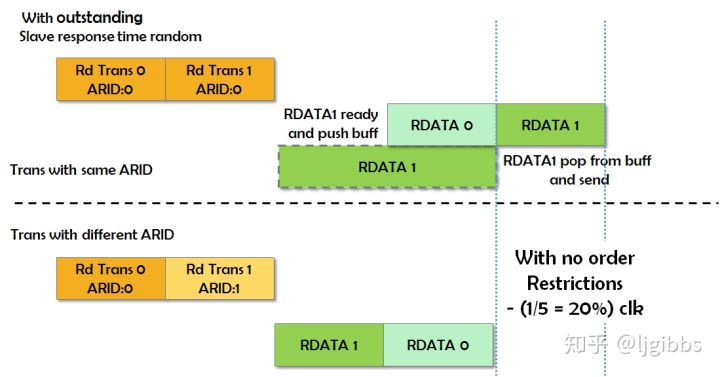

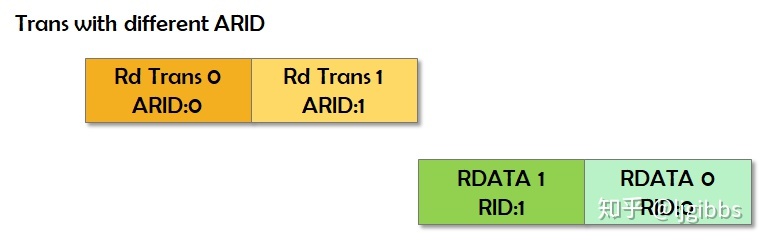

(2)协议规定,具有不同 ARID 的事务之间可以乱序(no ordering restrictions)。从机只需要维护各个 ARID 所属事务的返回顺序。基于例 A2,假设两个事务的 ID 不同,那么会变成下图中的景象,是为例 A3:

在事务 1 的数据就绪后,不再受到顺序返回的约束,即可直接返回。通过将传输事务设置为不同 ARID 后,能够加速上述场景的传输。

但是对于主机存在一个问题:对于多个不同 ARID 事务的数据,这些数据可能是乱序的,如何判断数据属于哪个事务?

正如前文所述,AXI 协议在读数据通道上也设置了 ID 信号 RID,用于从机标识该数据所属的事务。协议要求从机在发回数据时,填入与其事务 ARID 相匹配(match)的 RID 。这里笔者认为一般从机会直接将 RID 设置为与 ARID 一致,因此例 A3 中的信号应该是这样:

主机在接收数据后,可通过其 RID 与事务的 ARID 进行匹配。

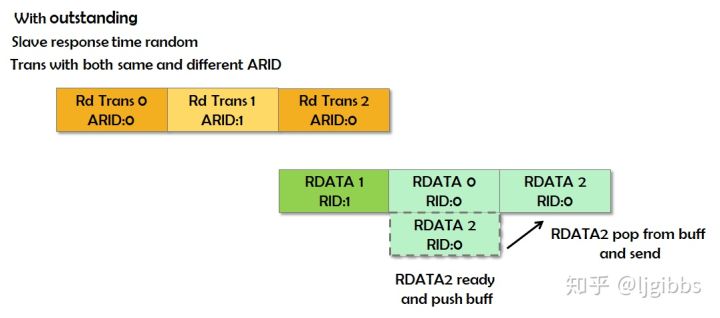

在实际的总线中,从机接收到的可能是混合有相同与不同 ARID 的事务。接下来的例子展示从机如何维护相同 ARID 事务的顺序,并通过对不同 ARID 事务乱序返回提高传输效率的,是为例 A4。

图中从机保证了 ARID = 0 两项事务的数据返回顺序。同时 ARID = 1 的事务 1 在后抵达的情况下,其读数据在就绪后在 事务0 之前发出,实现了乱序。

对于支持不同 ARID 的从机来说,实现为每个 ARID 准备了一个事务与数据缓冲区,如下图所示。就绪数据根据其 RID 分配至匹配的处理模块。

当 ARID 数量较多时,硬件开销无疑很大。不过不用担心,一般从机支持的 ARID 数量都是比较有限的,不会超过 16 个。

写事务实际上与读事务类似,不再过多讨论,总结为以下三点:

(1)相同点

对于相同 AWID 的写事务,从机必须按照主机发出的顺序完成。包括发送写回复信号

对于不同 AWID 的写事务,从机完成的顺序没有限制

(2)不同点

在写事务中,从机需要发送写回复信号给主机。使用与 AWID 匹配的 BID 标识写回复所属的事务 ID。实际上从机给出写回复可以类比读事务中给出读数据的过程。

(3)读写事务的相关性

协议规定读写事务之间本身不存在顺序约束,并且 AWID 与 ARID 之间不存在关联。当然具体应用中主机可以在发送事务时,增加顺序约束,但这与协议无关了。

读取DDR的时候如果碰到其他master也在读取同一地址可能会导致发生延迟。那么如果乱序处理,可以先读取其他地址的数据。加上outstanding功能,即使这一个命令的数据被延迟很久很久,也不会太影响带宽以及CPU的效率。

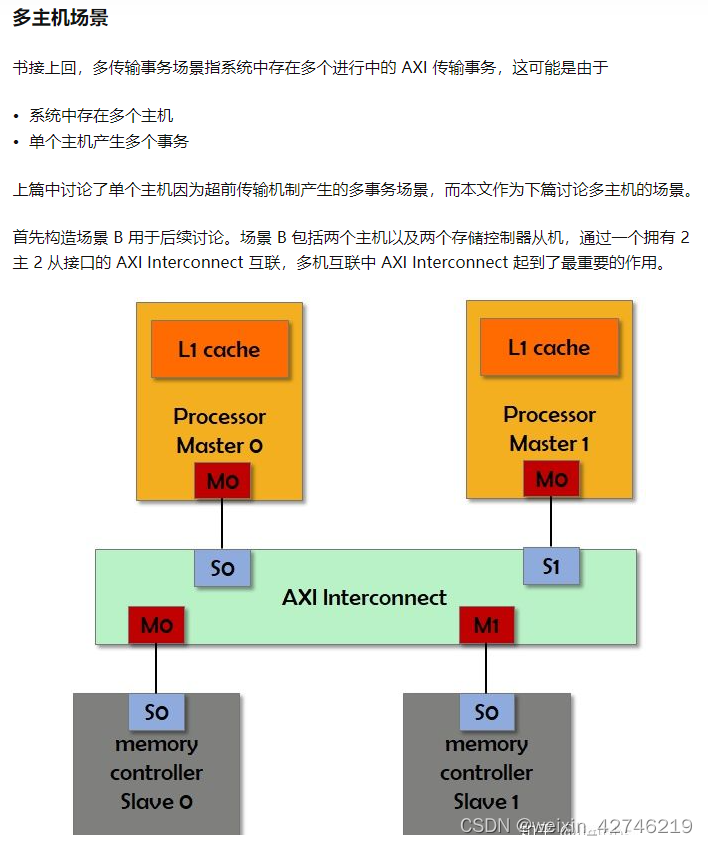

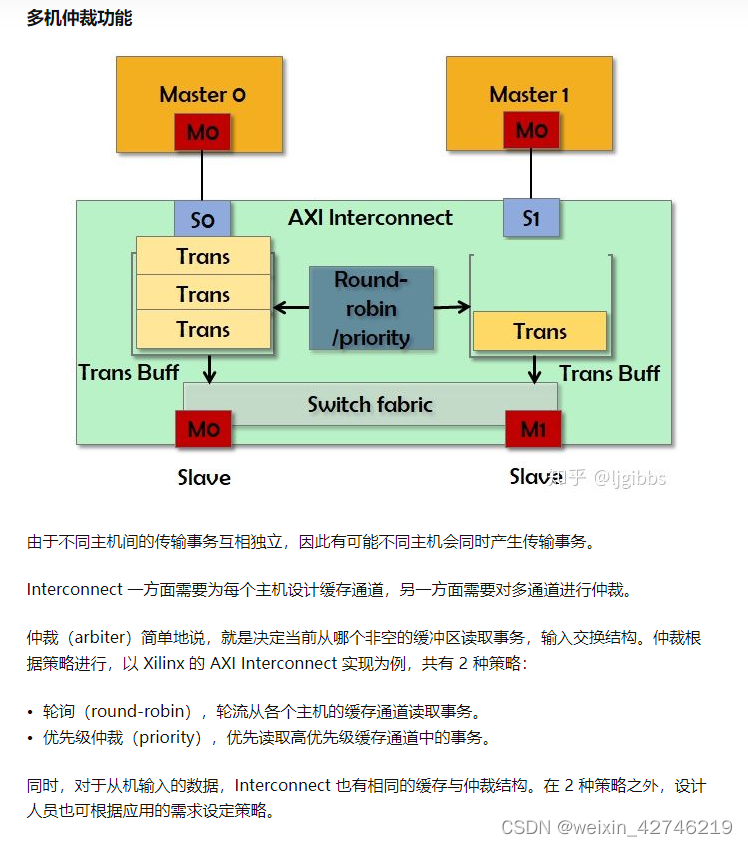

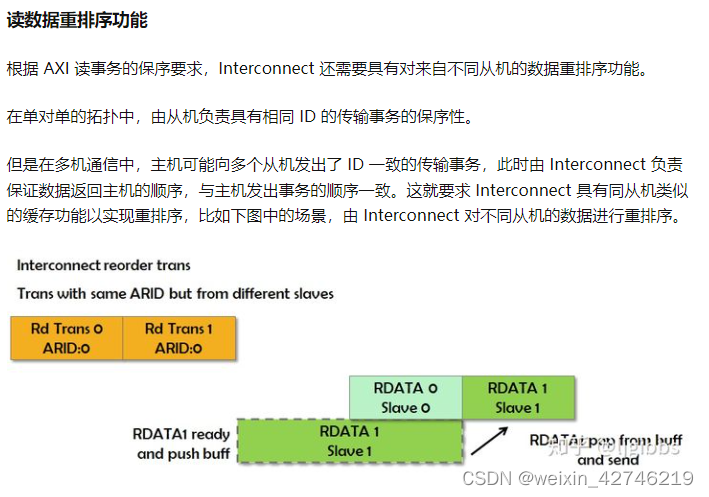

多主机场景

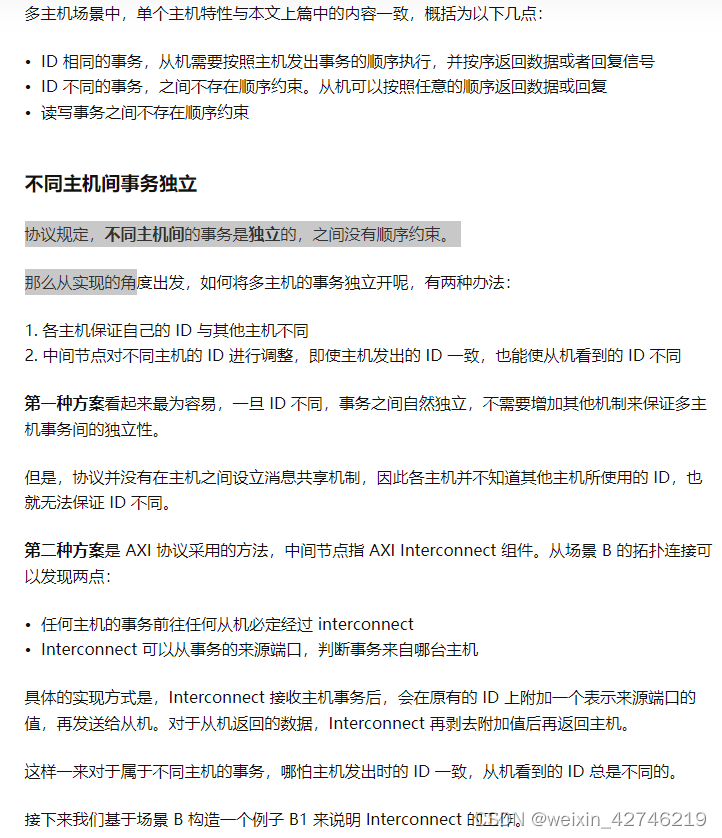

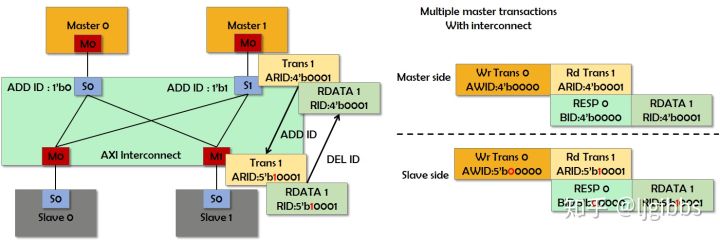

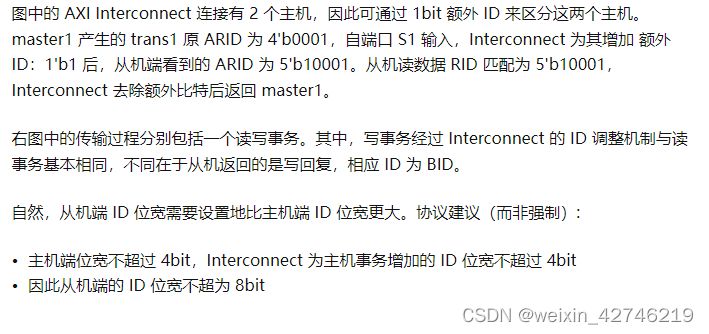

总结

引用:https://zhuanlan.zhihu.com/p/149112312