文章目录

- 前言

- 一、通道信号

- 二、AXI 握手机制

- 三、读写Timing

- 3.1 写数据

- 3.2 读数据

- 四、通道间的依赖关系

- 4.1 写地址通道( AW )

- 4.2 写数据通道( W )

- 4.2 写响应通道( B )

- 4.3 读数据( R )

- 五、信号详细解释

- 5.1 ACLK和ARESETn

- 5.2 Burst传输

- 5.3 Protection Level Support

- 5.4 Cache Support

- 5.5 Response响应

- 5.6 Write Data Strobe

- 5.7 Atomic 访问

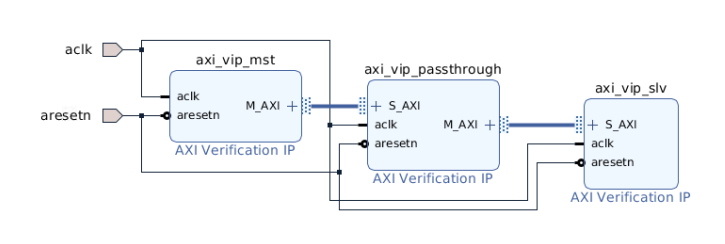

前言

AXI是一个并行总线,其主要特点包括:

- 读写通道分离;

- 支持多次对数据操作的请求(multiple outstanding address),一般支持8、16、32个outstanding;

- 写地址和数据之间不是严格的先地址再数据,有些可能是先数据再地址;

- 支持不对齐的数据传输;

- 支持乱序访问;

- burst传输时不需要像AHB那样每笔传输都指定它的burst类型和地址,只需要指定首地址和对应的属性;

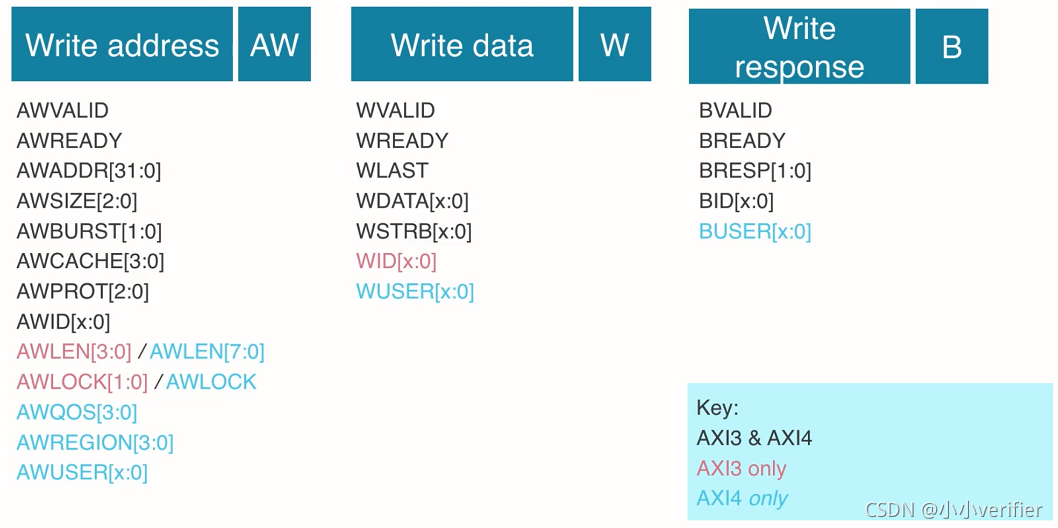

一、通道信号

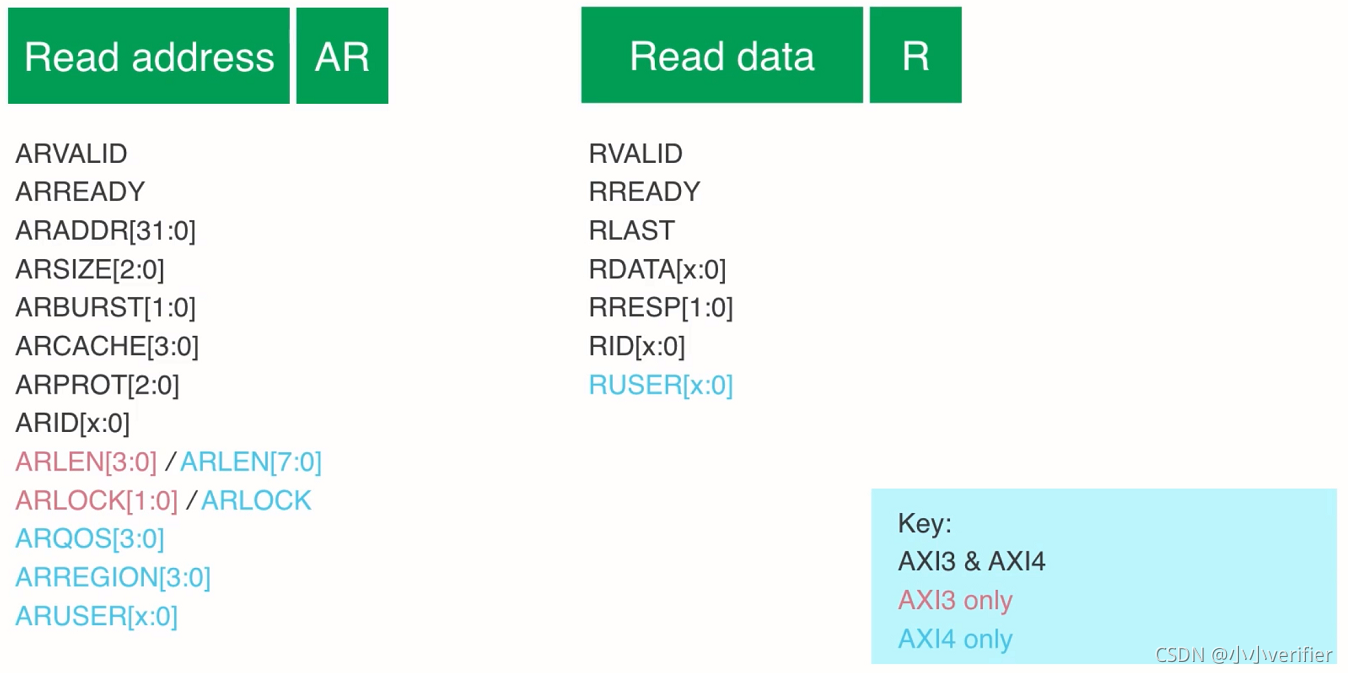

AXI 有5个单向事务通道,包括 Write Address Channel (AW)、Write Data Channel (W)、Write Response (B)、Read Address Channel (AR)和、Read Data ( R) 通道。每个通道的信号如下:

二、AXI 握手机制

AXI有5个channel,每个channel的传输都是基于valid 和ready信号来完成握手,这种握手方式在AMBA总线中被大量的使用。

握手的过程如下:

- 发送方将要发起传输的数据准备好,先发送 valid 信号给接收方;

- 如果接收方能够接收传输,就会发送 ready 信号给发送方;

- valid和ready都为高后,发送方发送 transfer;

注意:

- VALID 和 READY信号并不需要同时拉起,可以发送方想发数据,就先拉起 valid,也可以接收方有接受能力,就先准备好ready 。也就是说 VALID 可以早于READY,也可以晚于 READY,也可以同时拉起。

- 发送方不一定是master,接收方也不一定是salve。如,读数据通道(R)中,发送方就是slave,发送RVALID,master是接收方,发送RREADY。

握手信号间的约束关系:

- 为了避免死锁问题,协议规定:当 valid 信号被拉高后,不能随意地不经过 ready 信号握手,就将 valid 拉低。就是发送方可以根据自己的需求随时发起传输,不用判断接收方是否能够有能力接收,同时发送方一旦发起传输,就不能随意中止;

- 对于接收方,如果没有准备好接收就可以不拉高READY,这样就可以反压发送方的传输了,即便接收方在拉高READY后,只要发送方没拉高VALID,接收方还可以拉低READY信号;

- 发送端不能等ready拉高之后,才决定是否拉高valid。也就是说你想发数据就发,不用管ready是不是被置位了。否则如果你valid等ready,而接收端ready在等valid,这就形成了一个组合环,系统就被挂住了。

- 接收端可以等valid拉高,才拉高ready;

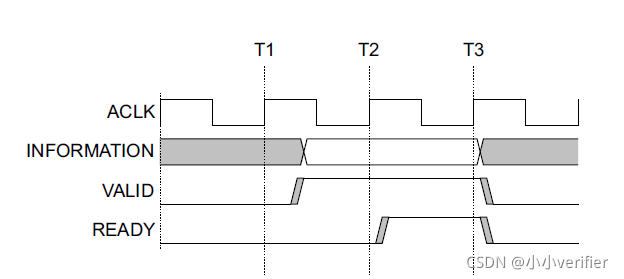

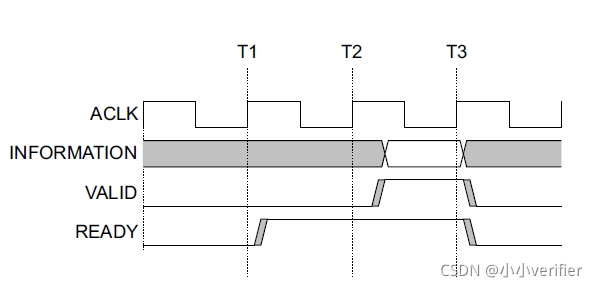

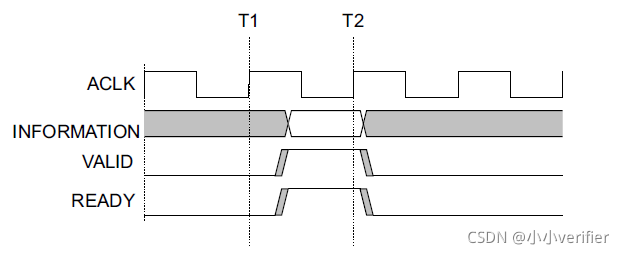

三种握手时序,如下:

- 第一种:valid先拉起,ready后拉起。传输等了一拍ready信号,两拍完成传输(T3完成)。

- 第二种:ready先拉起,valid后拉起。传输没有等待,一拍完成传输(T3完成)。

- 第三种:ready 和 valid 同时拉起。传输要在时钟上升沿,并且ready 和 valid 同时为高才开始,所以在T2时刻才发起传输。

三、读写Timing

3.1 写数据

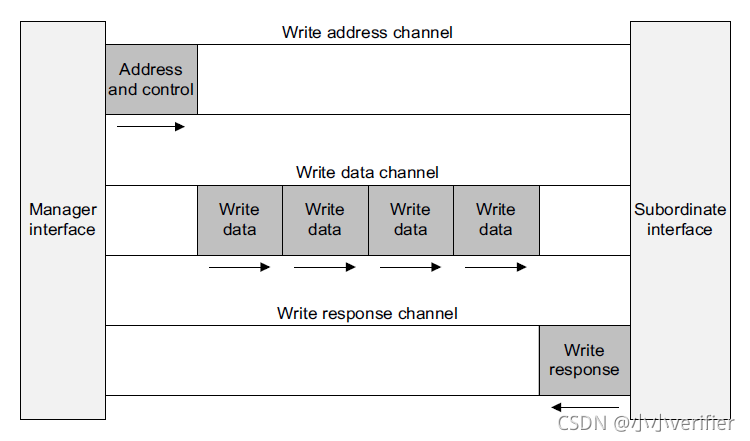

写操作的流程图如下,

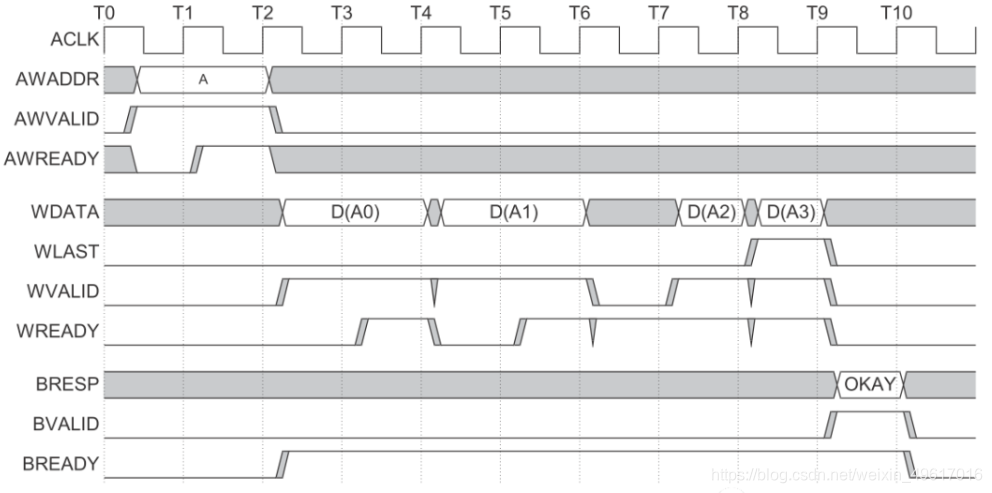

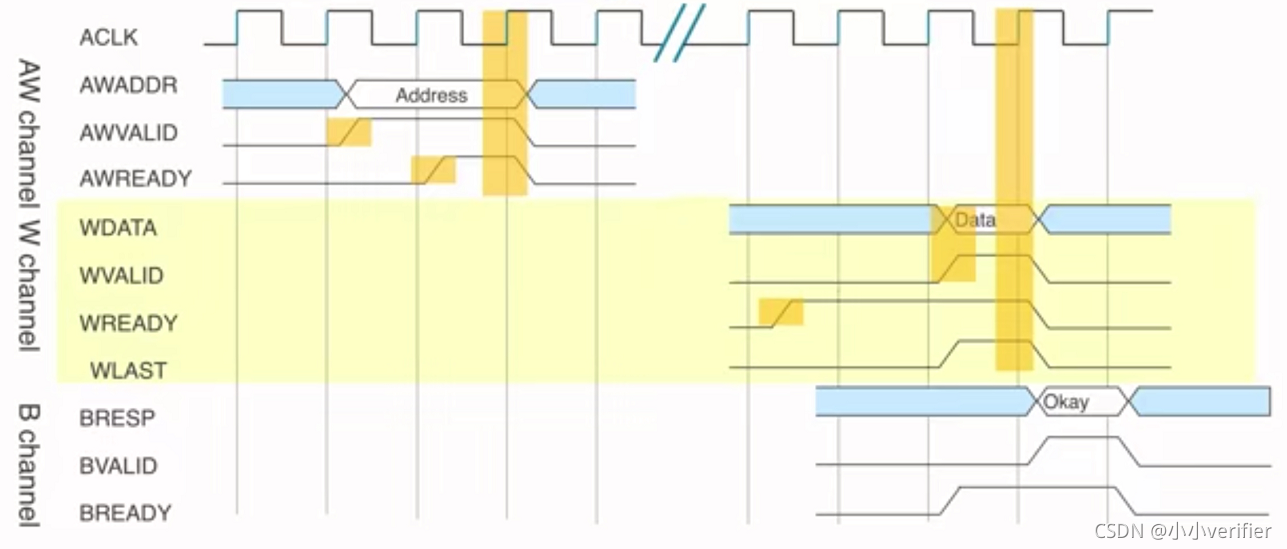

single传输时,有下面的时序图:

解释上图:

- 先是AW通道发送地址,当valid和ready同时为高时,完成地址传输

- W通道觉得可以发送数据时(后面会说通道间的依赖),通过握手信号的完成,将数据发送出去,同时WLAST信号拉高;

- B通道收到WLAST信号拉高,就返回一个response,并在握手完成时,完成发送response信号;

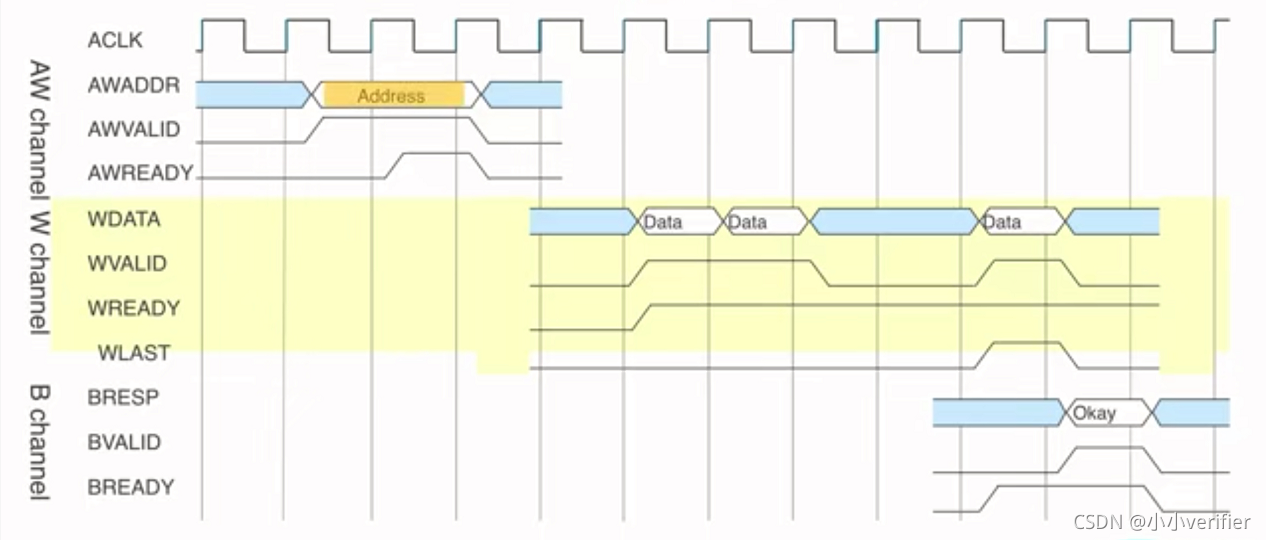

Burst传输时,有下面的时序:

解释上图:

- AXI在一次burst传输中,只需要在AW通道发送一次首地址;

- W通道相应的将数据写入,一个burst中的最后一个数据发出后,就将WLAST信号拉高;

- B通道收到WLAST信号拉高,即一个burst transaction完成时,才返回一个response,并在握手完成时,完成发送response信号。

3.2 读数据

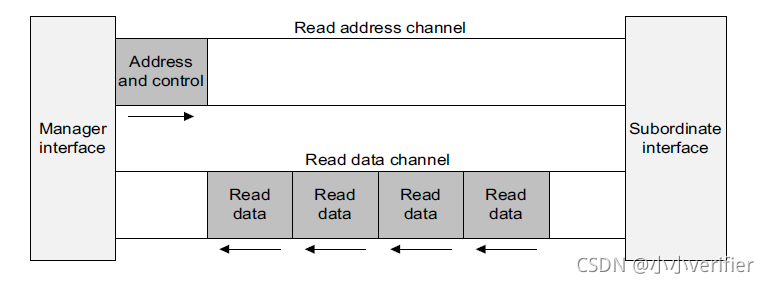

读操做的流程如下,

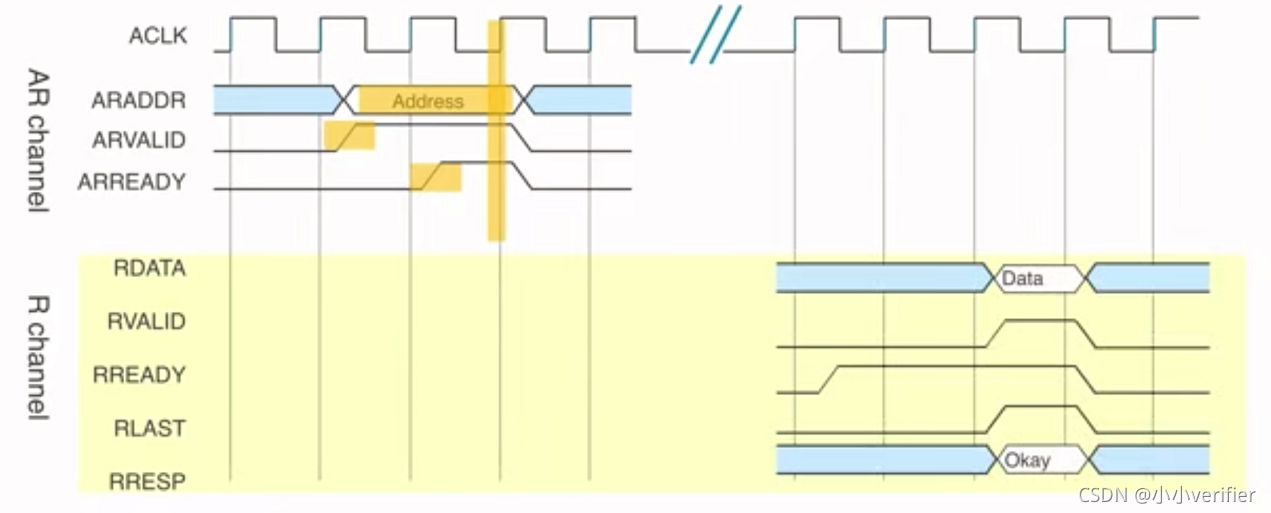

single传输时,有下面的时序图:

解释上图:

- 在valid和ready握手成功时,完成读数据的传输,并返回response

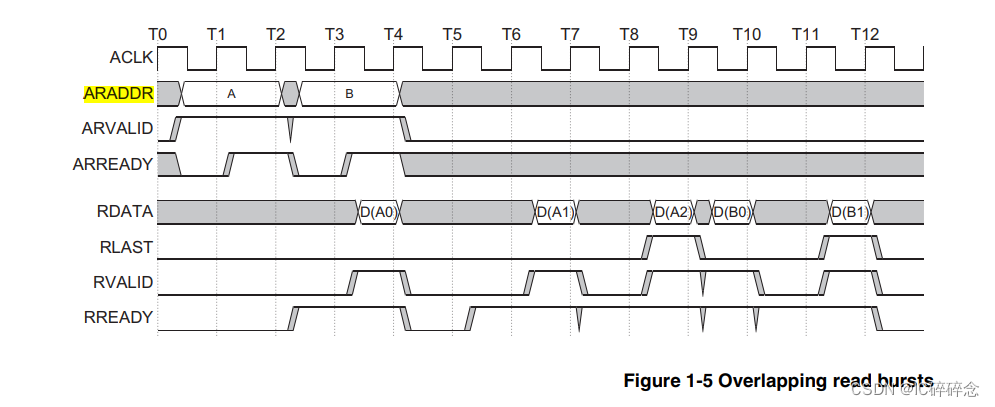

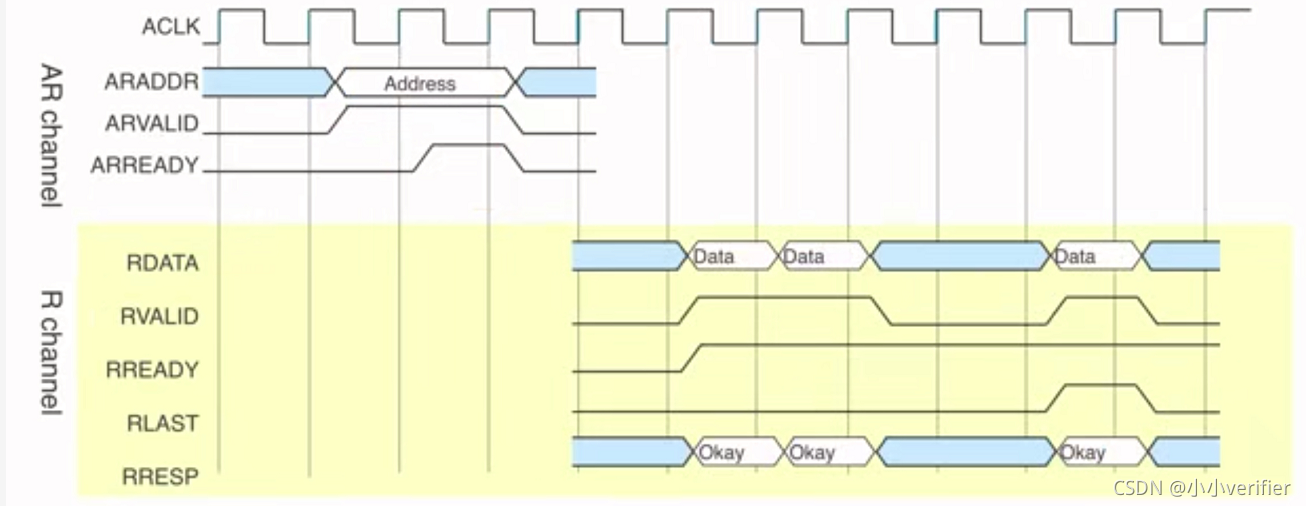

Burst传输时,有下面的时序:

解释上图:

- 读多个数据时,和写数据一样,只需要发送一次首地址;

- 最少一个时钟周期完成一个数据的读取,每次握手完成返回一个response;

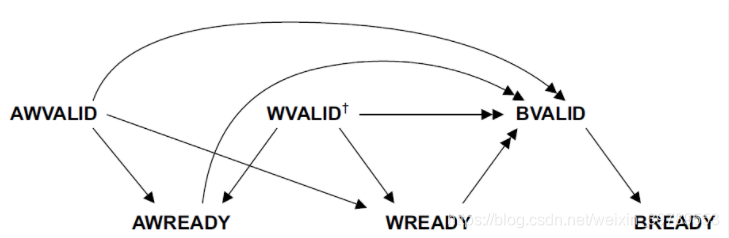

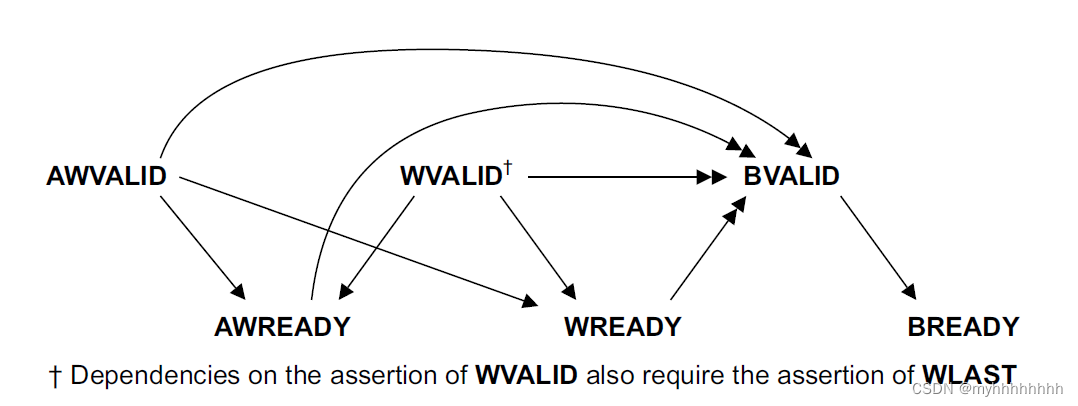

四、通道间的依赖关系

4.1 写地址通道( AW )

规定:

- 主端在驱动地址和控制信号时,就需要把 AWVALID 同时拉起;

- AWVALID信号一旦拉起,必须要保持到时钟上升沿,并且AWREADY拉高之后才可以释放;

注意:协议中建议不讲AWREADY的默认值设为低电平。因为这会迫使传输至少需要两拍才能完成,一拍拉起valid,一拍拉起ready。而默认值设为高电平,只要valid拉高就可以发,当然这需要从端始终支持一拍接收一个数据。

4.2 写数据通道( W )

规定:

- WVALID信号可以比AWVALID信号先置位。

也就是对于master而言,可以先发要写入到slave的数据,再发送地址。对于slave而言,要做好准备,很有可能是先收到数据,再收到地址命令。有这种需求是因为在一个大型的设计中,你不可避免的需要在总线通路上加一些buffer和寄存器来做时序上的收敛。如果你在AW通道上插入了寄存器,很有可能会先导致slave先收到数据,再收到地址,或者也有可能同时收到地址和数据。一般为了保证数据不要堵在总线上,可以设置slave先把这个数据存起来,不要放在总线上。

4.2 写响应通道( B )

规定:

- BVALID信号在拉高前,WLAST必须要已经发出去 。

协议规定,至少要收到最后一个transfer,salve才能去发送响应。但对于AXI3 和 AXI4 的区别在于:

- AXI3 要求 BVALID信号在拉高前,必须要收到WLAST的数据;

- AXI4 要求 BVALID信号在拉高前,不仅要要收到WLAST,还要收到对应的地址。

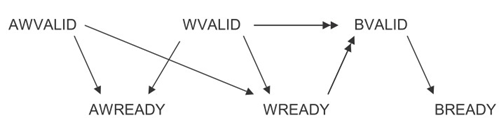

4.3 读数据( R )

规定:

- ARADDR再没发完之前,RVALID信号不可以被拉高 。

也就是说必须要先收到地址,才能读数据。只有收到了读地址通道的命令,才可以去读数据。

五、信号详细解释

5.1 ACLK和ARESETn

对于ACLK信号,要求:

- 所有的输入信号都在时钟上升沿采样;

- 所有的输出信号只能在时钟上升沿改变;

对于ARESETn信号,要求:

- 低有效复位;

- 异步复位、同步释放;

- 主端要驱动 ARVALID, AWVALID 和 WVALID 信号为低, 从端要驱动RVALID 和 BVALID 为低,其他信号可以是任意值。

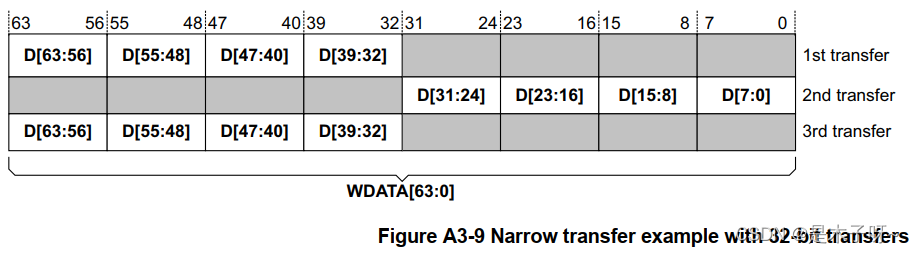

5.2 Burst传输

Burst传输中的相关信号有:

| 信号 | 描述 |

|---|---|

| AxLEN[3:0] | 指定每个burst中具有1~16个传输,AXI3 |

| AxLEN[7:0] | 指定每个burst1中具有1~256个传输,AXI4 |

| AxSIZE[2:0] | 每个传输中的有效数据位宽 |

| AxBURST[1:0] | 包括FIXED(00) 、INCR(01)、WRAP(10) 类型 |

注:AxLEN表示AWLEN或ARLEN,其他的也是类似。

AxBURST[1:0] 信号中,不同的bits位:

| AxBURST[1:0] | 类型 | 描述 |

|---|---|---|

| 'b00 | FIXED | 每个传输的地址都是相同的,用于对同一个地址的重复访问,比如访问FIFO |

| 'b01 | INCR | 地址递增 |

| 'b10 | WRAP | 地址递增回环,即地址递增到某个边界值会跳转到起始值,一般对cache做操作 |

| 'b11 | reserved | 保留域 |

协议中规定:

- WRAP 类型的burst的长度必须为2、4、8 或16;

- 一个burst的地址空间不能跨越 4KB,否则有可能访问到其他slave;

- burst只要发出,就不能提前终止;

5.3 Protection Level Support

| 信号 | 描述 |

|---|---|

| AxPROT[2:0] | 定义事务的保护属性,包括 privilege, security level, and access |

AxPROT[2:0] 信号中,不同的bits位:

| Bits | 类型 | 描述 |

|---|---|---|

| 0 | Privileged模式 | 指定访问模式 |

| 1 | 0:secure ; 1:Non-secure | 决定传输是 secure 还是 non-secure ,secure的transfer可以访问secure或non-secure的memory空间 |

| 2 | Instruction | 表明传输是指令还是数据 |

5.4 Cache Support

| 信号 | 描述 |

|---|---|

| AxCACHE[3:0] | 可以配置 bufferable、Cacheable / Modifiable、、 |

详细的定义如下:

| Bits | 类型 | 描述 |

|---|---|---|

| 0 | Bufferable/Non-bufferable | 可以选择是否先将这个transaction存到 buffer 中,可能这个 transaction 还没有到达接收方,buffer可以先返回response给发起端 ,提前结束这个transaction |

| 1 | Cacheable / Non-cacheable | 决定是否可以把多个transfer进行整合 |

| 2 | Read-Allocate/No Read-Allocate | |

| 3 | Write-Allocate/No Write-Allocate |

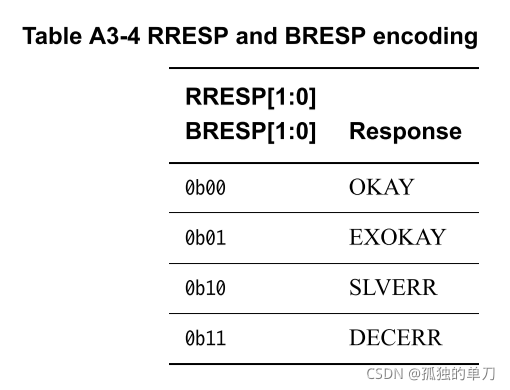

5.5 Response响应

| 信号 | 描述 |

|---|---|

| RRESP[1:0] | 对read burst中的每个transfer返回response |

| BRESP[1:0] | 对write burst整个transaction 返回response |

response的类型包括:

| Bits | 类型 | 描述 |

|---|---|---|

| 00 | OKAY | 正常访问成功 , 也可以指示 Exclusive 访问失败 |

| 01 | EXOKAY | Exclusive 访问成功,在后面 Atomic操作中会详细介绍 |

| 10 | SLVERR | slave返回给master的错误信息,可以自定义哪些情况需要返回 error |

| 11 | DECERR | 返回译码错误,比如burst访问地址空间超过4KB |

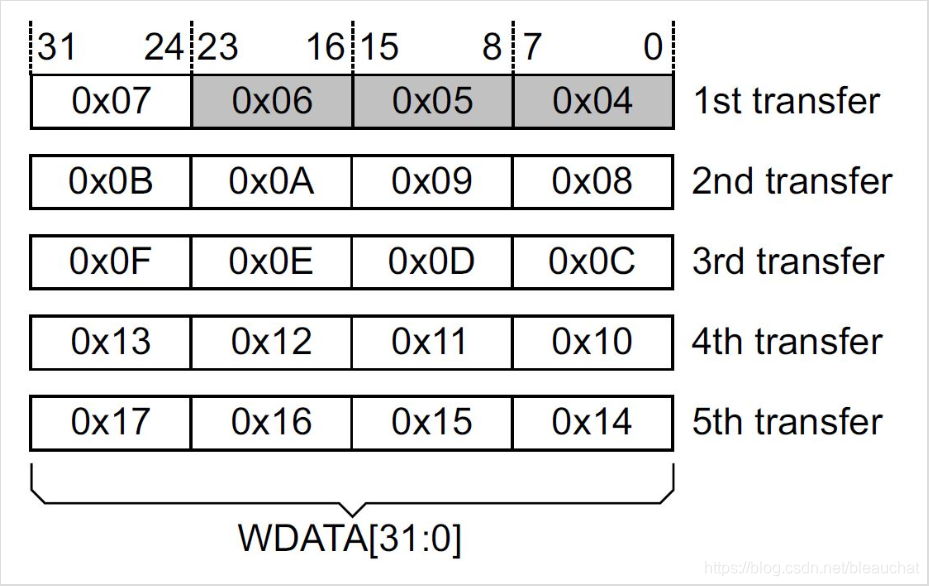

5.6 Write Data Strobe

WSTRB[x:0] 来指定数据每个byte(8 bit)是否有效。

比如,64 bit 的数据,即 8 Byte,当

- 假如最低位 Byte 数据 有效,则WSTRB为0x01;

- 假如最低两 个 Byte 数据 有效,则WSTRB为0x02;

- 其他以此类推

5.7 Atomic 访问

假如有两个 transaction 准备往同一个地址写数据 ,为了保证写入的数据要么是第一个transaction 或者第二个 transaction 的,肯定不希望在某个时刻,有一半数据是第一个transaction 的数据,一半数据是另一个transaction的数据。所以这个时候就需要使用到 Atomic 访问,有两种实现Atomic 的方式,下面分AXI4和AXI3支持的特性展开。

在AXI4中,如下:

| AXLOCK | 类型 | 描述 |

|---|---|---|

| 0 | Normal | 正常访问 |

| 1 | Exclusive |

在AXI3中,如下:

| AXLOCK[1:0] | 类型 | 描述 |

|---|---|---|

| 00 | Normal | 正常访问 |

| 01 | Exclusive | 同AXI4 |

| 10 | Locked | 一个master 访问 某个slave的总线通道就会被 locked 住 ,当别的master也想访问这个slave时就无法访问 |

| 11 | Reserved | 保留域 |

Locked 和 Exclusive的区别?

- Locked 会对总线性能影响很大,因为当一个 master 想访问这个 slave 时,这个通道会被 locked 住。如果其他master 也都想访问这个 slave,请求也都发出来了,大家都访问不到,相当于对总线层面上锁住了,那对性能的影响就会很大。所以现在的处理器很少采用,AXI4 中也不支持 locked 操作。

- Exclusive区别于 Locked 的一点是它不会把master访问某个slave的通道锁住,Exclusive访问机制可以提供信号类型的操作而不需要总线专供特定master使用。 这意味着信号量类型的操作不会影响总线访问延迟或最大可实现带宽。