AXI总线学习连载(2)

鲁迅曾经说过:

学硬件,不是学哪里查哪里,有一些东西是必须系统的学的,不管是嵌入式还是FPGA,硬件学习的积累一定要是系统的。

我也曾经说过:

英文手册非常重要,这是学习硬件标准的不二法门,没有捷径,我们这一行可以不说英语,英语也可以像我和我某些同事一样口语富有乡土气息,但是一定要能熟练看,内心看,做阅读理解一样看

跟着这篇博客,慢慢学习,对着官方文档,不仅可以学会这个协议,更能够学会硬件学习的方法,所谓举一反三。(我说的比鲁迅还多)

好了既然是axi,那么这么说,只要你使用arm架构的芯片,arm和fpga(pl 可编程逻辑)部分通信,或者外部设备通信,你都会用上这个协议。所以一起来学习,打工人!就该把自己的时间全部放在上面

好了不废话了,一起来探索吧!

不要厌烦枯燥,理论学习是在实践之前的必经过程,当学习完axi原型后,我也会专门贴出来一个axi协议使用开发的详细详细详细的n次方的接口解析。请学习过程中不要放弃,不要觉得枯燥!! (其实说给自己听的)

qq:2198187857 这里放出来一下,就是希望朋友们指导,有不足的地方批评教育一下,作为新手,还是很认真在学习

--------------------------------------------------------------分割线-----------------------------------------笨蛋看不见-----------------------------------------

在我每次学习新东西前,我首先会复习上次的内容,那么我把一些关键信息放在这里。如果想要复习,请回到连载(1)

上一次我们学到五个通道

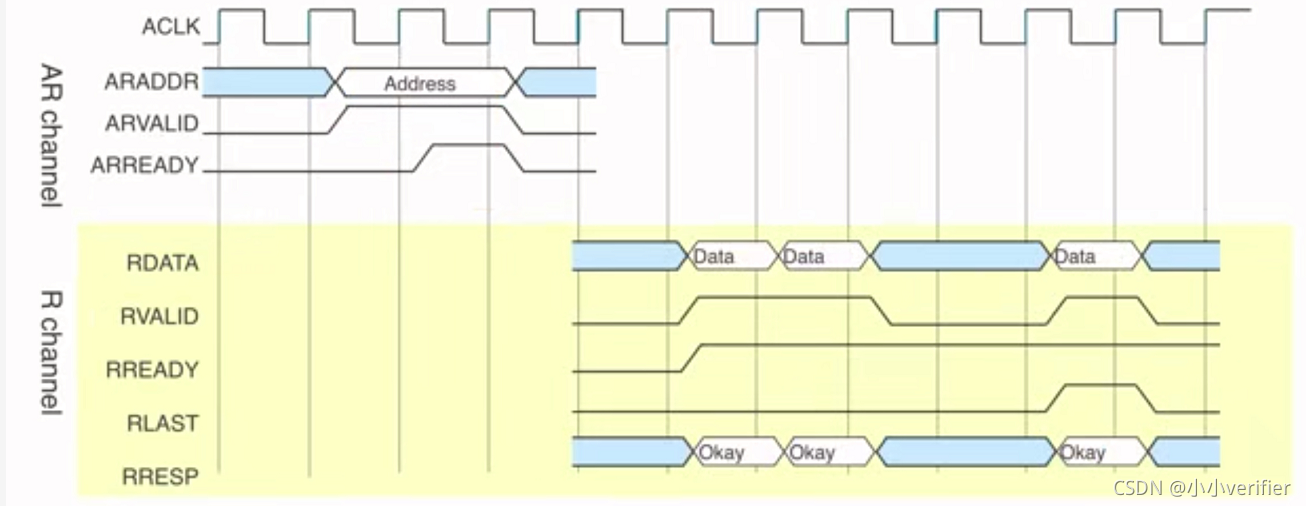

读地址通道(read address channel) AR

读数据通道(read data address channel)R

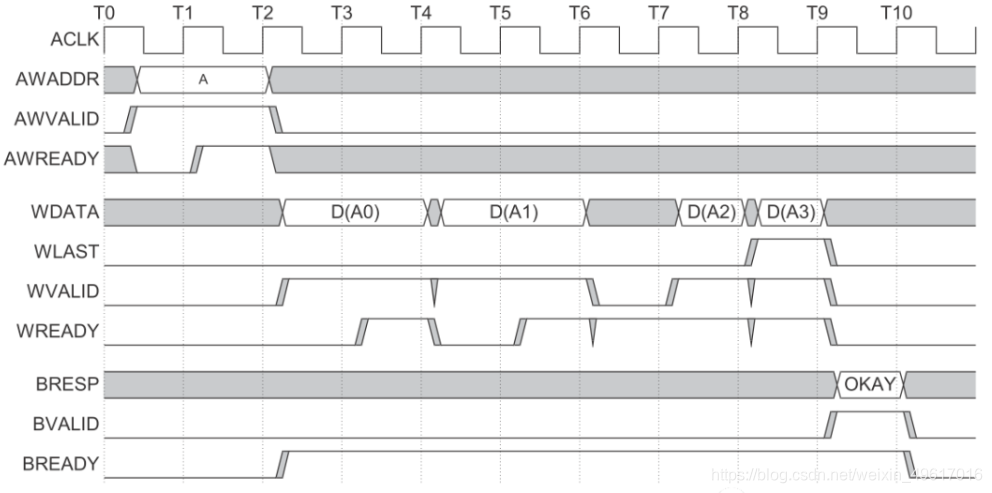

写地址通道(write address channel )AW

写数据通道(write data channel )W

写响应通道(write response channel ) B

那么请自己默念一下这个几个通道的含义。

--------------------------------------------------------------分割线-----------------------------------------笨蛋看不见-----------------------------------------

这次我们来进一步学习一下这个五个通道有什么特征

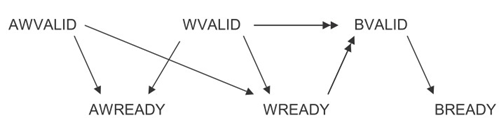

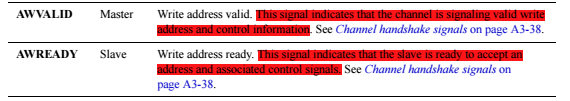

1. 第一个特征就是他们都有各自的VALID和READY(比如AWREADY和AWVALID,你可以理解为五对腐臭的异性恋,他们都非常辣眼睛!!!)

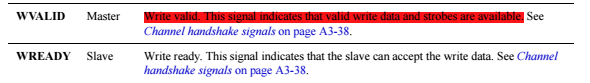

首先我们知道每一个通道都包含了一些信号线,这些信号线位宽可以自定义(先学习,实际应用后续会有),其中我们会率先认识每个通道都有的VALID和READY信号

这是一个双路信号握手机制,不懂握手机制没问题也会讲到,但我们要先清楚知道,握手机制其实是master和slave之间达成共识的一个标志,请在这里注意,并不是VALID信号就来自于master

READY信号就来自于SLAVE,其实是VALID来自于source即源设备,READY来自于destination即目标设备。(主从设备,源,目标设备概念在连载(1)).

所有的信息源设备(请注意是源)都会发送一个VALID信号,去展示出自己通道内此时的东西是否是有效的,比如AWVALID表示此时AW通道内的地址和控制信息是有效的。

当然目标设备(请注意是目标设备)都会发送一个READY信号,去展示自己是否准备好,当VALID和READY都是高电平的时候(当然有规则哈,后续会讲解),我们可以说这时候,各自通道内的东西开始

发挥作用,至于怎么发生作用,这个各自通道之间会有一定关联性,比如地址通道会给数据通道中的数据标识存放位置。但我们目前能够知道,所谓握手其实就是通过源发送VALID,目标设备发送READY.

重要事情说两遍:握手信号其实就是通过源发送VALID,目标设备发送READY

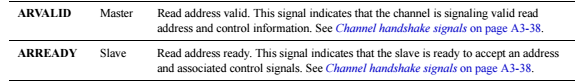

2,读地址和写地址通道(AR AW)

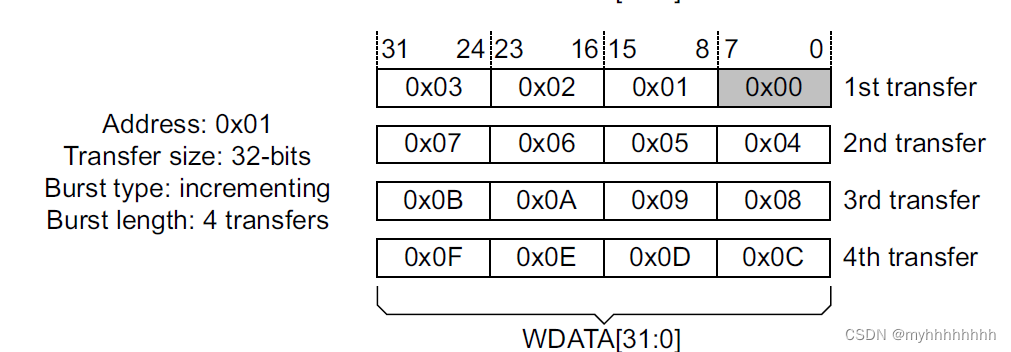

这两个通道其实都是传送的各自在读和写处理时候,需要把读或者写的数据放的地址和控制信息,这里强调下,其实只传递了第一个字节数据的地址,后续地址根据控制信息改变。

(请注意一点,在arm体系内,都是字节编址,所谓字节编址其实是每8bit即一个byte占据一个地址,和传统FPGA不同,当然,xilinx的ip核也可以配置为这样的一种方式,比如ram模块打开32bits模式,此时就是按照字节编址,不得不感叹官方

ip核的通用性有多么强大)

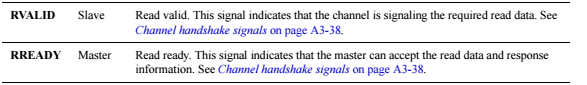

3 读数据通道

读数据通道携带的是我们要去读出来的数据,这里再一次说明对于读来说,从设备是源设备,主设备是目标设备,所以在这个通道内部,VALID其实是从设备发出,READY是主设备发出,这里在FPGA的编程界面需要注意,

比如我们使用axi外围ip核和axi bram controller等从设备时需要注意的。(这里涉及底层,后续会贴出接口代码,并讲解)

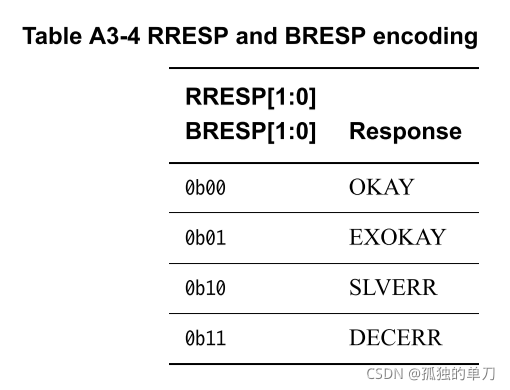

其中我们的数据总线可以是8,16,32,64,128,256,512,1024bits,还需要注意读响应信号是包含在读书据通道中,和写响应通道不同。

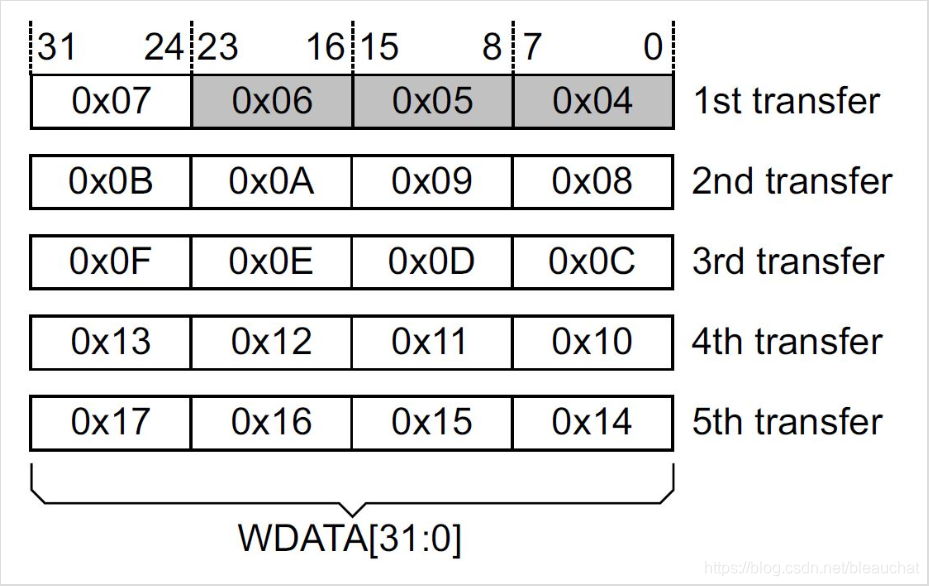

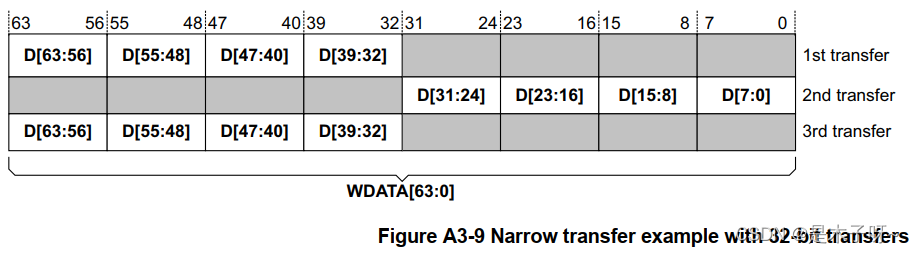

4 写数据通道W

写数据通道携带的是我们把主设备需要写给从设备上的数据,同样的我们可以使用8,16,32,64,128,256,512,1024bits的总线位宽

这里引入一个术语(a byte lane stobe)来字面解释,一个字节通路闸门,其实我们可以说是对于一个字节的开关,这个其实就是对于每八位一个辨别或者是识别,看看这当前数据总线中的每八位即每个字节

是否用上。

有人会担心了,写数据会不会有丢失,因为各种原因,其实不用担心,在写数据通路的硬件电路上,始终都是具有缓冲输入的,所以我们可以不需要从设备发送上一次写处理信息而继续写入(当然这是有限制的后续也会有),现在就记住

写就对了,对于ZYNQ开发 我们其实就直接用库函数的寄存器写入直接写就行了,满足后面讲的边界规则即可。现在只需要记住缓冲输入,所以你可以看见eda工具自动生成部分会有buffer部分。

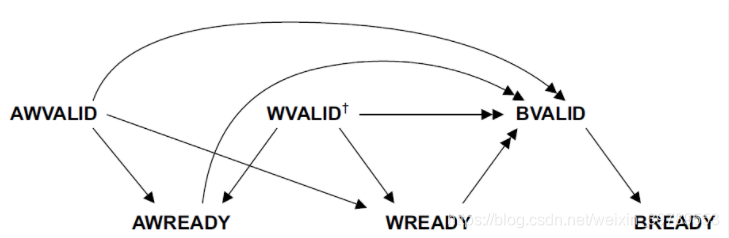

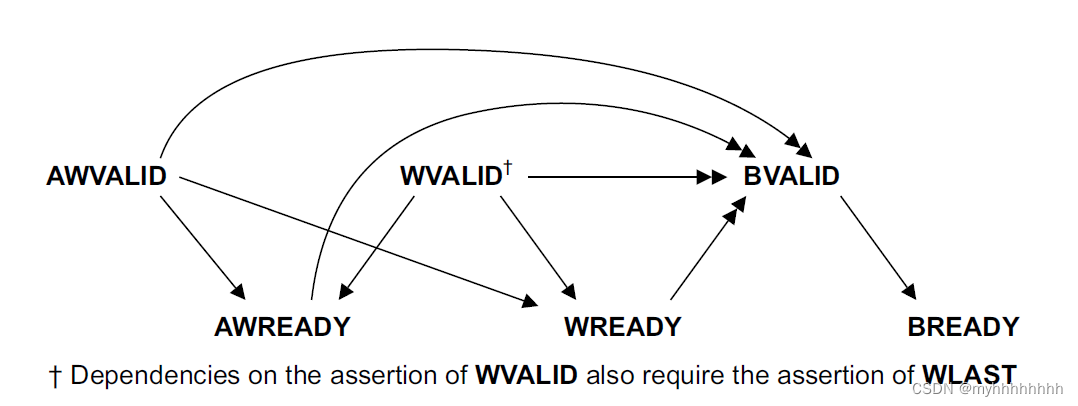

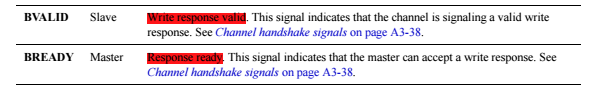

5写响应通道B

顾名思义其实就是一个响应当前写处理过程的一个通道,值得注意的是,要求所有写处理都需要把返还响应。

--------------------------------------------------------------分割线-----------------------------------------笨蛋看不见---------------------------------------------------------------------

接口和互联

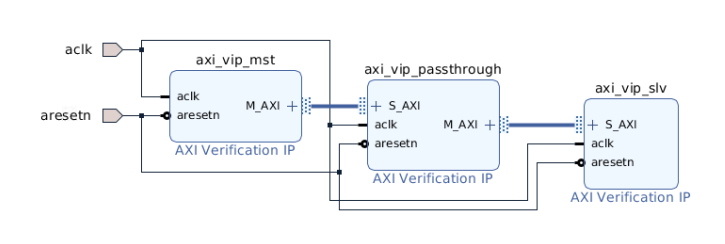

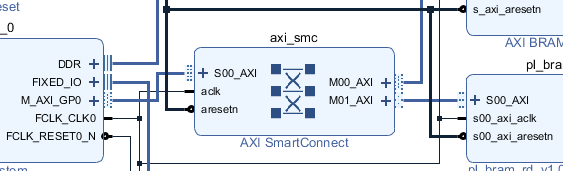

这里放一张图就可以了,说的太负责比较绕口,反正就看到从处理器出来的m接后面互联的s ,对称互联会有一个m接后面pl ip核的s,这样连接下去。

总的来说其实就是,这个就是arm处理器要和别人连一起必须要遵守的。这也就反应,一个哲理问题:

鲁迅说过的:

协议是协议,协议不仅仅是协议。

总线是总线,总线不仅仅是总线。

总线实现协议,协议标明总线。

都是设备,都是外设,只是手牵手时要用正确姿势。

--------------------------------------------------------------分割线-----------------------------------------笨蛋看不见---------------------------------------------------------------------

可能这里有朋友会说,为什么我们搞了这么一大堆操作,怎么说写读,读写巴拉巴拉,到底是主从设备哪里在搞这些。其实不要心急,如果你问我可以说时主从设备各自有一个寄存器

不信你看图

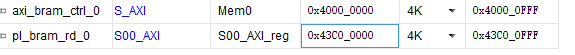

这是笔者最近在用的,你可以看见这两个模块都是从设备,他们都有各自的寄存器空间。当然对这个寄存器具体的位置进行什么操作这个是需要继续学习的,但我们要理清楚一个关系。其实我们在sdk中做的所有操作,

其实都是主设备(处理器)处理外面的从设备,往这个从设备寄存器写信息。

这就是今天的重点,以往来说我们会接触寄存器版和库函数版本,但是这一次学习,不会这么简单,我们两个版本都会讲明白。

看到这里,需要知道一个基本点,就是每一个通道他们在传东西传信息都是仅仅按照一个方向即单向,这样做的好处是,各通道之间可以减少更多的依赖性,虽然通道之间有关系,但是还是最好减少,

就像是五个家庭,虽然是亲戚,但是不必要的关系少一点,大家族才能更和谐。

--------------------------------------------------------------分割线-----------------------------------------笨蛋看不见---------------------------------------------------------------------

好了 关于axi原型导论部分就结束了,明日我们将学习五个通道内部的信号特征,当然是概念性,我们去研究首先的得知道大家族内部各自信号名字,然后在深入学习

今天我先把我们学习的两个握手信号拿出来,机理部分后续讲,现在我们先认识他

写地址通道

写数据通道

写响应通道

读地址通道

读数据通道

--------------------------------------------------------------分割线-----------------------------------------笨蛋看不见---------------------------------------------------------------------

好了依旧勉励大家,每天一小时学习,笔者也是每天一小时把学习过的东西拿出来好好总结,在自己总结学习的路上结合工程,真的是受益匪浅,

硬件学习很漫长,但是每一次成就感都很深,希望各位加油,年轻的时候多学习,少玩了

好了笔者要去玩战地5了 明天见!!!