由于DDRx总线对时序的要求非常严格,随着速率的提升,时序的要求会更高。要使用DDRx批处理仿真器,需要创建控制器和DRAM颗粒的时序模型,时序模型文件后缀为“*.V”。

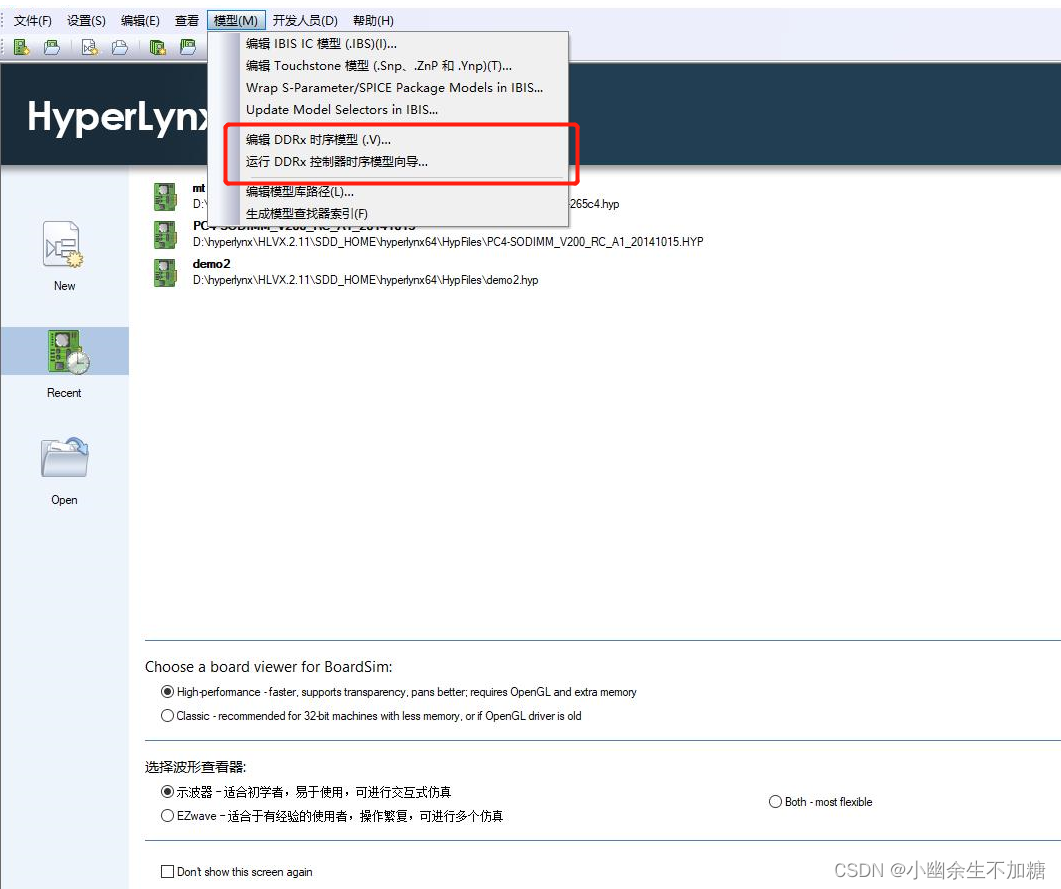

HyperLynx 提供两种方式进行时序模型的创建和编辑:

一种是在语言编辑界面下进行编辑,这种方式可以编辑DRAM的时序模型,也可以编辑控制器的时序模型;

另一种是向导流程编辑模式,这是一种控制器时序模型编辑模式。HyperLynx软件提供了市场主流的 DDRx总线速率的时序模型,一般仿真都可以直接使用软件自带的时序模型文件,所以接下来主要介绍控制器时序模型向导编辑模式。

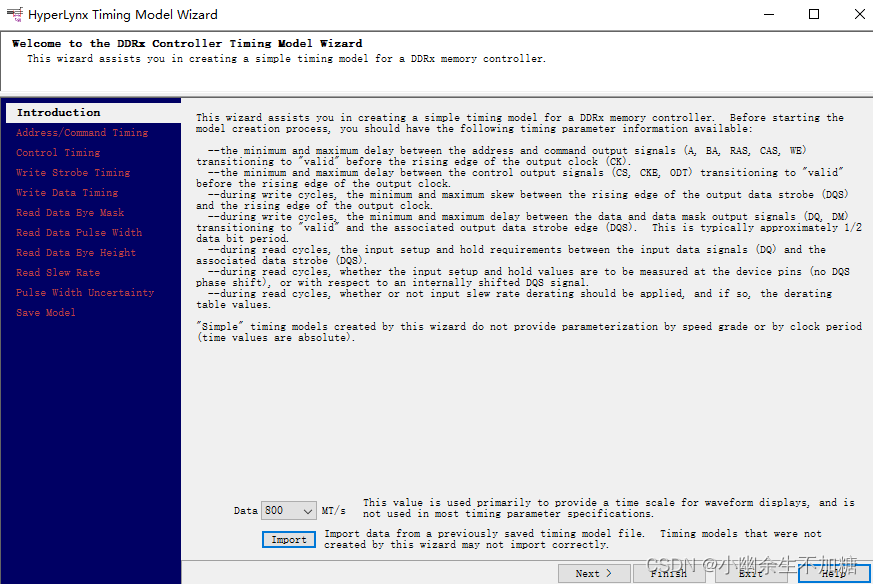

只要打开HyperLynx的主界面就可以在菜单栏上选择模型(Models)→运行DDRx控制器时序模型向导(Run DDRx Controller Timing Models Wizard),打开时序向导编辑界面,如图所示。

该界面中显示了所有需要编辑的参数,包括地址/命令信号的时序、控制信号的时序、读和写操作的数据选通和数据信号时序、写操作的数据选通和数据掩码信号时序,以及建立和保持时间的降额参数。

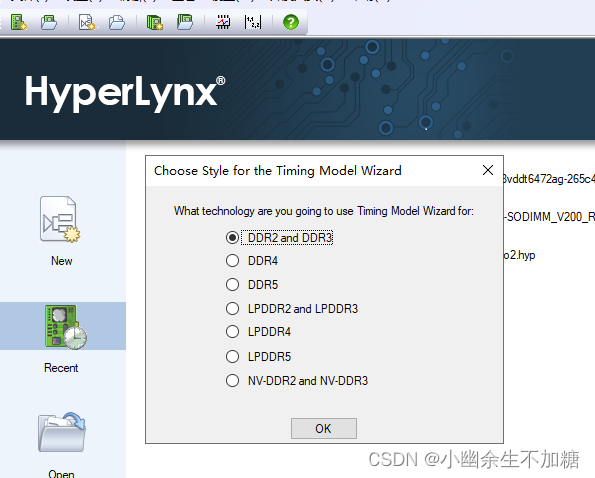

(1)设置速率

以该DDR3的控制器为例,具体按界面中的流程进行编辑。在时序向导界面中,首先根据实际项目的DDRx速率进行设置,即选择控制器(CPU)的DDRx总线速率,在数据速率(Data Rate)下拉菜单中包含了几乎所有的DDRx的速率类型,也可以单击Import按钮,导入之前编辑好的时序模型文件,如图所示:

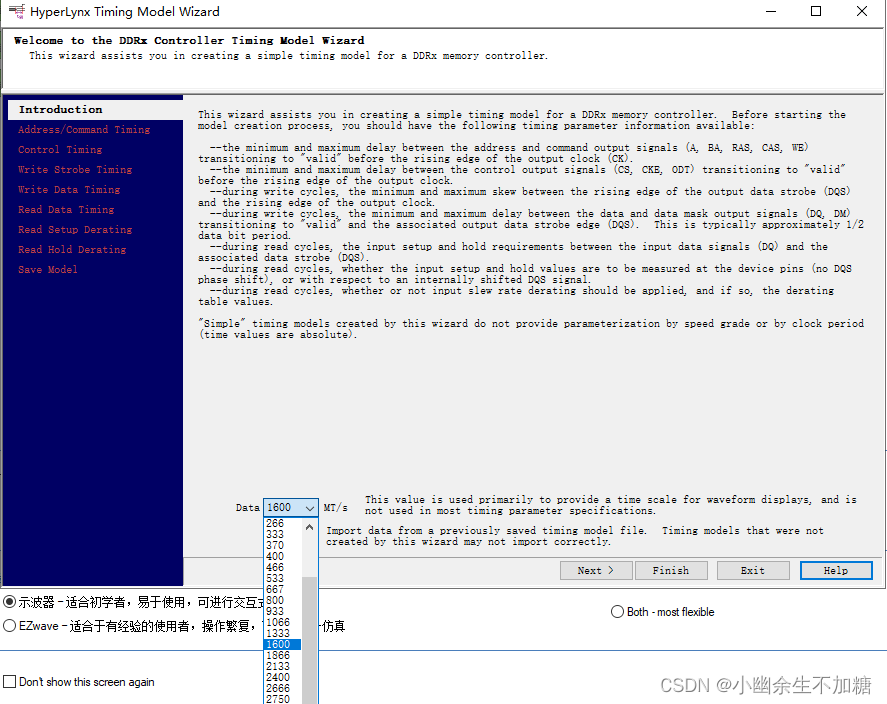

数据速率选择1600Mb/s。

选择速率后,单击Next按钮。在开始下面的设置之前,工程师要计算获得时钟周期,例如,1600Mb/s的信号速率,那么其时钟周期即tCK=1.25ns。

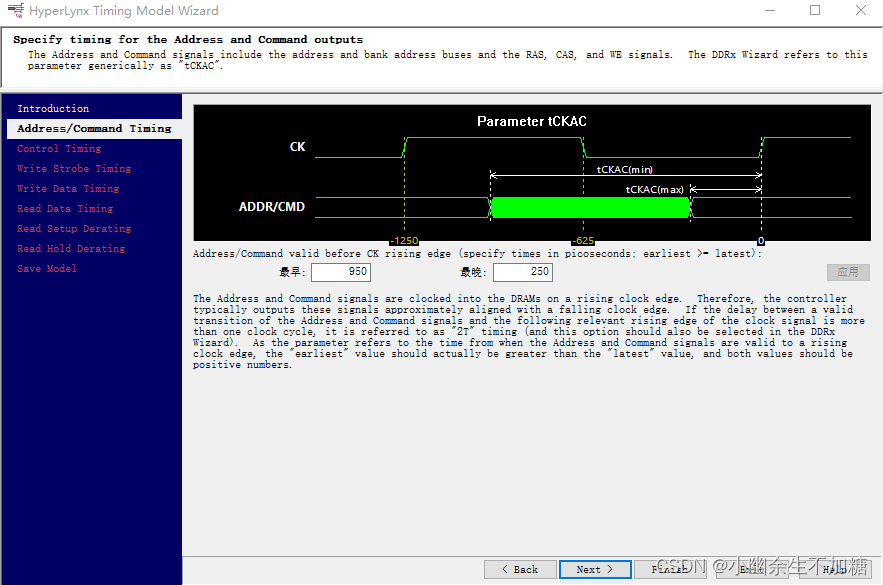

(2)设置地址/命令网络信号的时序参数

包含 Address、CAS、RAS 及WE信号,如图所示:

这里需要设置两个参数,分别是最小延时(Earliest)和最大延时(Latest),它们表示在地址和命令输出信号与输出时钟上升沿转变为有效采样电平之前的延时。此例子中地址/命令信号的延时分别为950ps和250ps,输入参数之后,单击 Apply 按钮,否则设置参数无效。

地址和命令信号是电平采样,在达到采样电平,并在时钟上升沿变化为有效时,地址和命令信号被锁存到 DRAM 中。在设置时要注意,最大延时要小于最小延时。如果传输时间超过1个时钟周期,那么在DDRx仿真时,选择2个时钟周期。

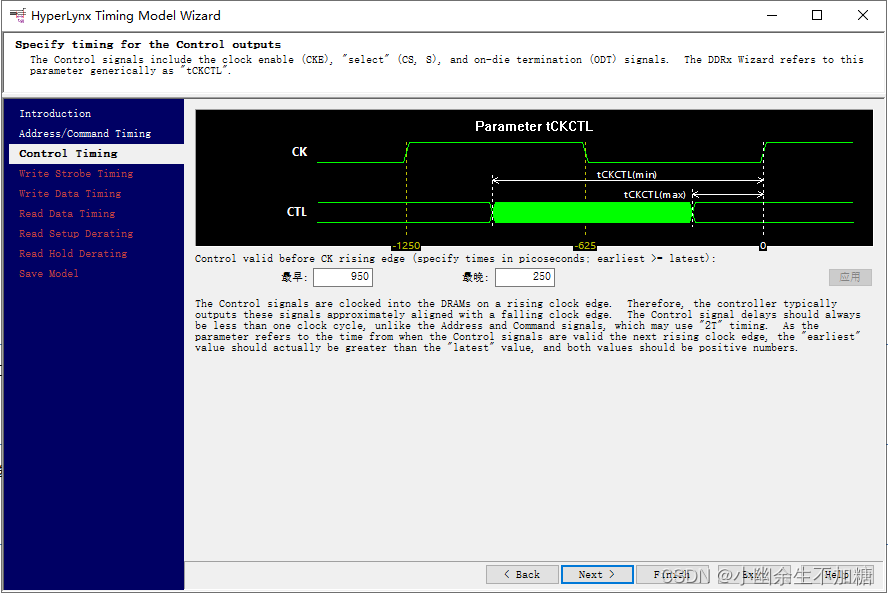

(3)设置控制网络信号的时序参数

设置完地址命令时序参数之后单击Next按钮,设置控制网络信号的时序参数,包括 CKE、CS和ODT 控制信号,控制信号也是电平采样,采样的方式与命令信号一样。所以也需要设置最大延时和最小延时值,最大延时为250ps,最小延时为 950ps,这里一定要注意,延时不能超过2个时钟周期。同样,在输入相应参数之后,单击 Apply按钮,如图所示:

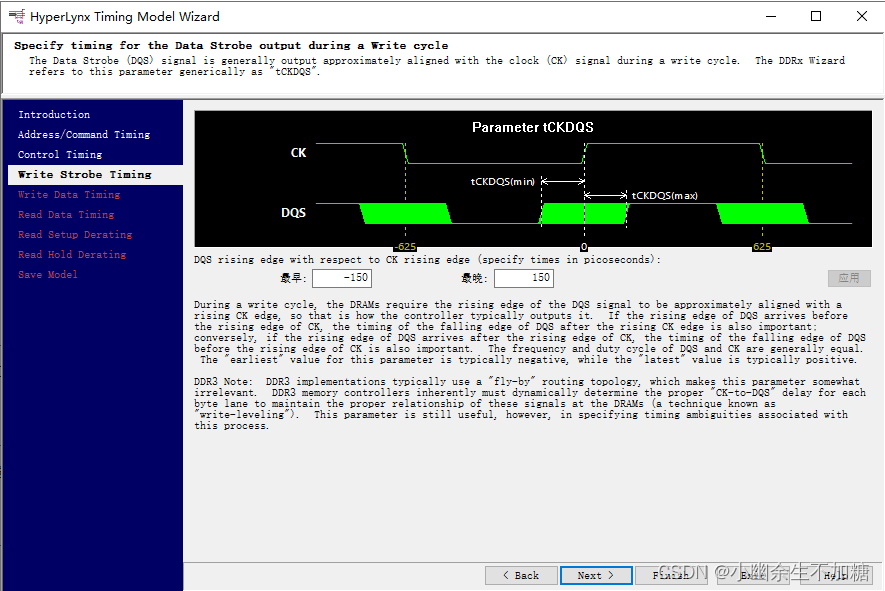

(4)设置DDR3控制器写操作时数据选通信号与时钟信号的时序关系

设置完控制信号参数后单击Next按钮,设置DDR3控制器写操作时数据选通信号与时钟信号的时序关系。在DDR3设计上,虽然在一定程度上弱化了数据选通信号与时钟信号之间的关系,但在操作时序上,依然非常紧密。DDR3 的数据选通信号与时钟信号的频率是一样的,在数据选通信号写操作时,控制器典型的输出方式是数据选通信号边沿与时钟近似对齐。如果数据选通信号的上升沿在时钟信号上升沿的前面到达 DRAM,那么数据选通信号的下降沿就会在时钟信号的后面到达。

反之也是一样的,如果数据选通信号的上升沿在时钟信号上升沿的后面到达 DRAM,那么数据选通信号的下降沿就会在时钟信号的前面到达。

通常,最小值(Earliest)为负数,最大值(Latest)为正数,这两个参数值表示数据选通信号与时钟信号的偏移。此例子中,最小值和最大值分别为-150ps和150ps,输入后单击应用按钮。

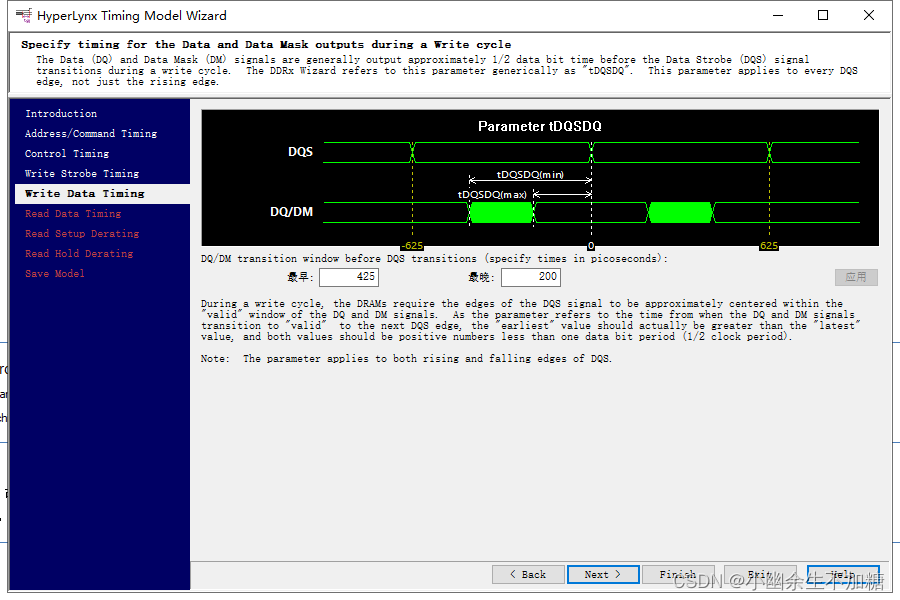

(5)设置DDR3 控制器写操作时的 DDR3数据和数据掩码时序参数

设置完写操作数据选通信号时序参数后单击Next,设置DDR3 控制器写操作时的 DDR3数据和数据掩码时序参数。

数据和数据掩码信号的参考时钟信号是数据选通信号,在写操作周期中,通常在输出数据和数据掩码与数据选通信号转变为有效采样之前,数据和数据掩码信号输出大约为一半位宽。这两个信号都是在数据选通信号的上升沿和下降边沿采样的,而不仅是上升沿。在此需要设置最小延时(Earliest)和和最大延时(Latest),最小延时的参数值要大于最大延时的参数值,并且都为正值、都小子于数据信号的一个位宽(1/2个时钟周期),所以设置参数值为425ps 和200ps,如图所示:

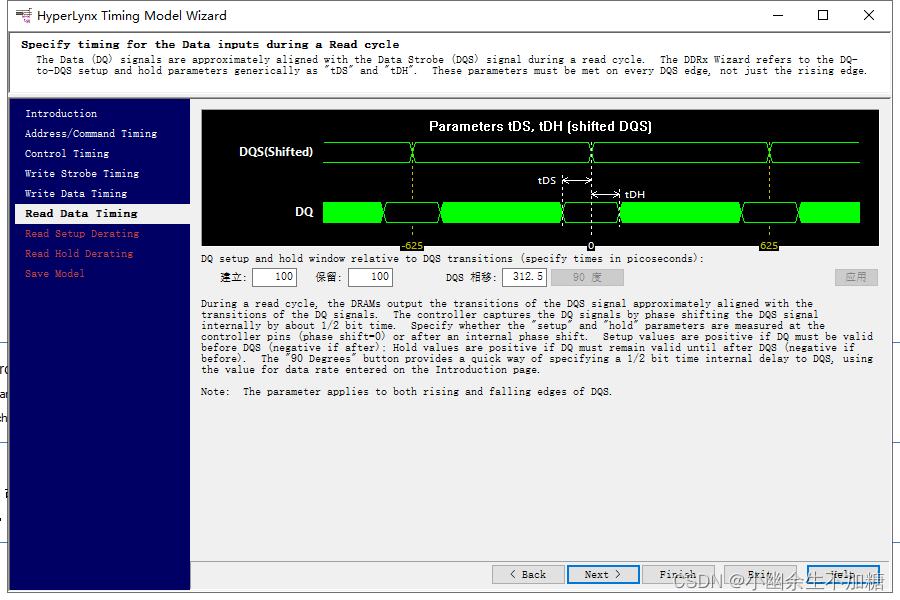

(6)建立和保持时间参数

设置完写操作数据和数据掩码时序参数后单击Next按钮,设置DDR3控制器读作时的数据时序参数,即建立和保持时间参数。

在读操作时,DRAM输出数据选通信号和数据信号近似对齐。控制器通过数据选通信号内部相移大约1/4的时钟周期(1/2信号位宽)捕获数据信号。在这一步中需要指定数据相对数据选通信号的建立和保持时间,此例中建立和保持时间分别设置为 100ps 和 100ps,同时相移 90°,单击 Apply按钮,如图所示:

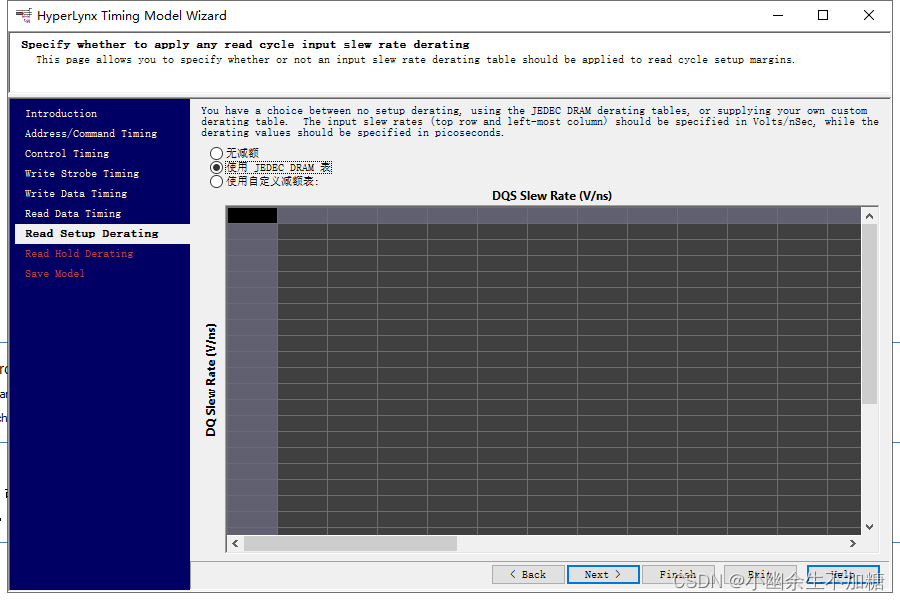

(7)设置读操作的建立时间的降额参数

设置完读操作的数据时序参数后单击 Next 按钮,设置读操作的建立时间的降额参数值如图所示:

这一步有3个选项,分别为不需要降额(No Derating)、使用 JEDEC DRAM 降额参数表(Use JEDEC DRAM Table)和使用自定义的降额参数表(Use Custom Derating Table)。

一般建议使用JEDEC DRAM 降额参数表。

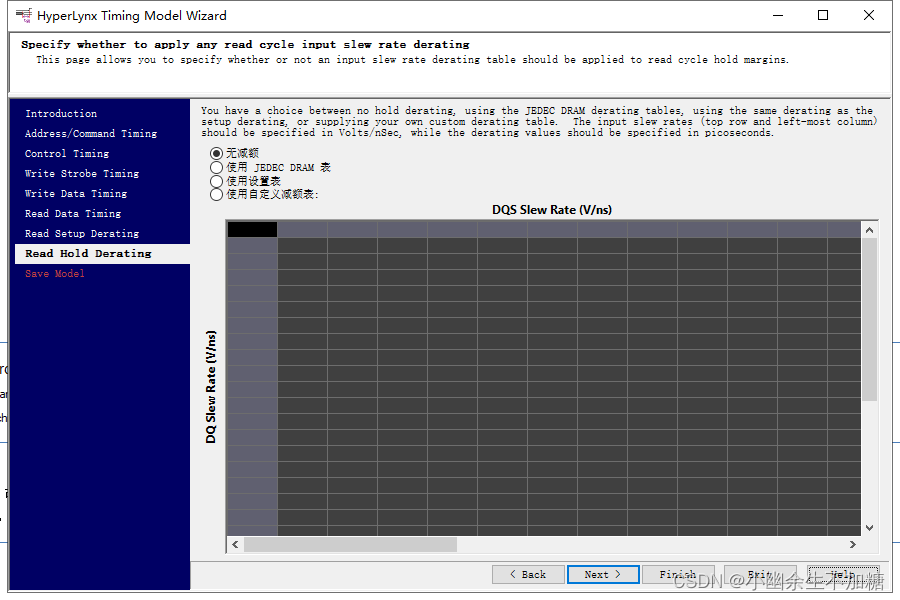

(8)设置保持时间降额参数值

选择后单击 Next 按钮,设置保持时间降额参数值,如图所示:

该选型比建立保持时间多一项选择,就是用建立时间降额参数表(Use Setup Table),如果选择这一项,就和上一步使用的参数一样。建议使用JEDEC DRAM降额参数表。

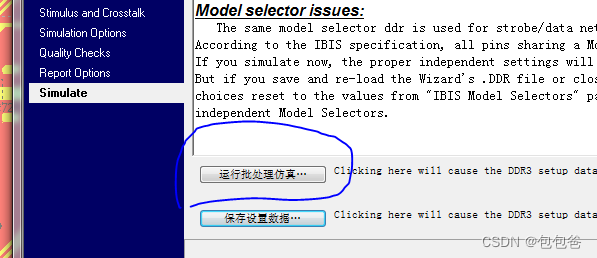

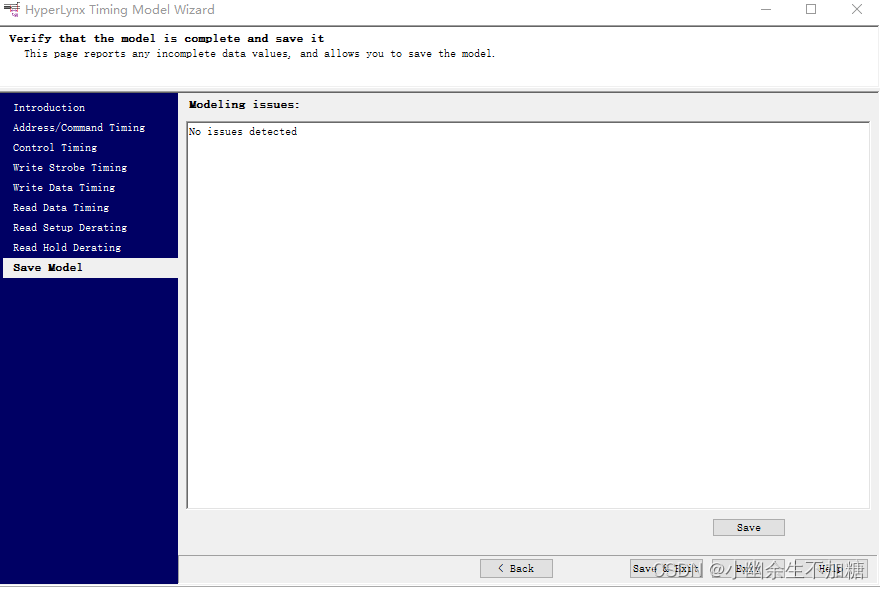

(9)保存时序模型

如图所示:

在保存模型页面中,如果设置的模型没有任何问题,则会显示:“No issues detected”。如果有错误,则会显示哪一项或者哪几项设置有问题。模型没有问题,选择保存模型(save)选型,保存在仿真目录下,以备后续使用。