HyperLynx(二十三)DDR(六)DDRx总线批量仿真

- 1.DDR仿真流程

- 2.仿真前参数设置

- 3.批处理仿真前验证

- 4.DDR2总线批处理仿真(实例)

- 4.1 收集设计信息并为DDRx向导准备设计电路

- 4.2 设置DDRx向导

- 5.仿真结果分析解读

- 6.DDR3/DDR4设计要点

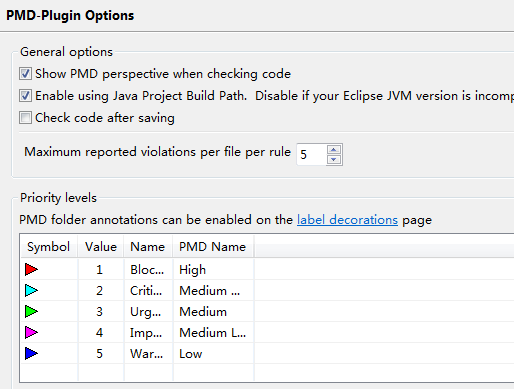

DDRx批处理仿真器是HyperLynx专门为DDRx总线设计的仿真工具,不管是前仿真还是 后仿真都有。DDRx批处理仿真器,不仅能仿真信号质量,还能仿真信号的时序,仿真完成后,软件自动生成仿真报告,从报告中能一目了然地看出结果是否满足设计要求,或者存在哪些需要改善的信号网络。

总体来看,DDRx批处理仿真器具有如下特点。

仿真向导化,仿真参数设置都是流程类的向导,按步骤设置并仿真。

能分析时钟与所有的地址/控制命令信号的时序关系。

能分析所有数据信号的时序。

能分析测量时钟信号与数据选通信号之间的偏移量。

能分析各信号网络的信号质量。

能自动生成各个信号网络的信号质量和时序的报告。

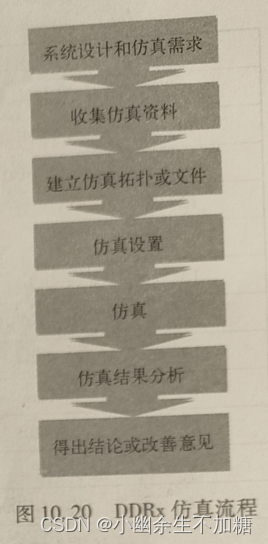

1.DDR仿真流程

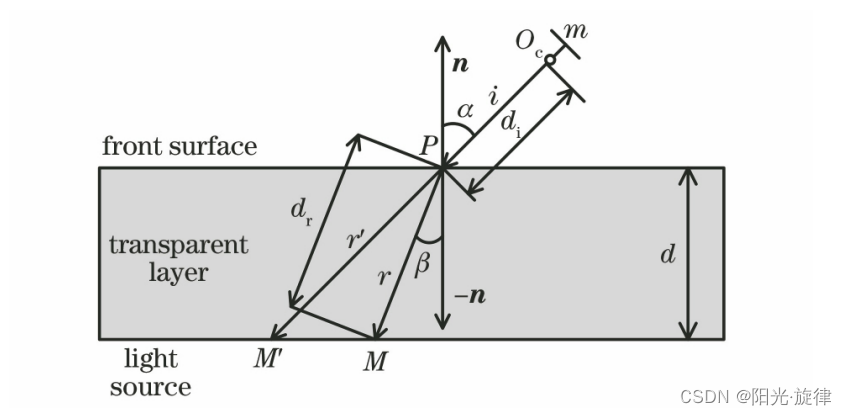

DDRx批是一DDRx总线仿真向导工具,仿真设置和过程比较简便,其大致仿真流程如图所示:

系统设计和仿真需求是仿真的指导方针,工程师在仿真之前必须仔细分解每一个需求细节;

仿真资料包含原理图、PCB设计文件、仿真模型、元器件数据手册、层叠和材料资料等;如果是前仿真就需要建立仿真拓扑结构,后仿真则需要转换为仿真PCB文件;

仿真设置包含电源设置、层叠设置、模型设置、仿真速率设置等;

仿真结果分析主要是对所有的仿真获得的文档、数据和波形进行分析;

最后获得仿真的结论或改善意见,反馈给相关的工程师。

当然,每一工程师的工作方式不一样,所以流程也不尽相同,但最终的目的一样。

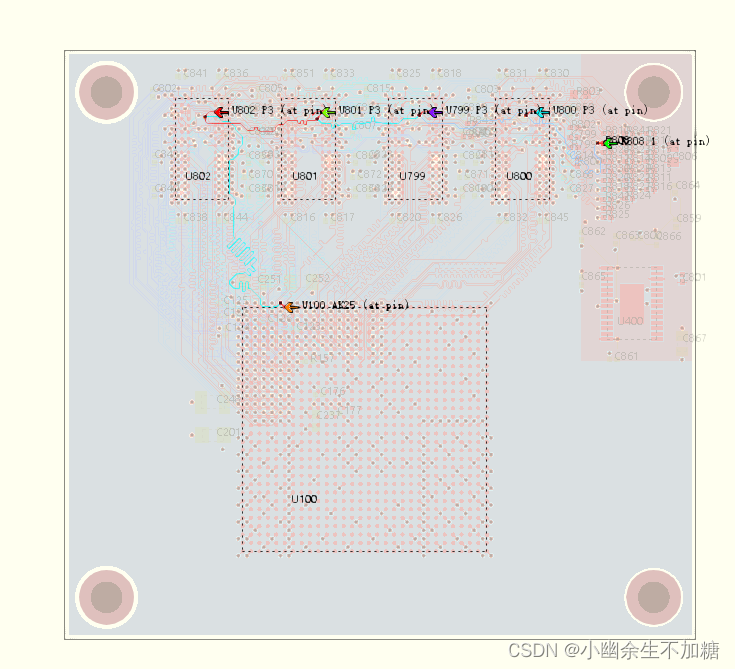

2.仿真前参数设置

由于前仿真和后仿真都可以对DDRx总线进行批量仿真,在本节中,主要以后仿真为例介绍DDRx总线批量仿真向导工具。后仿真就需要准备备好仿真PCB文件,把PCB文件转换为*.Hyp文件,可以按照之前介绍的步骤进行转换。如图所示:

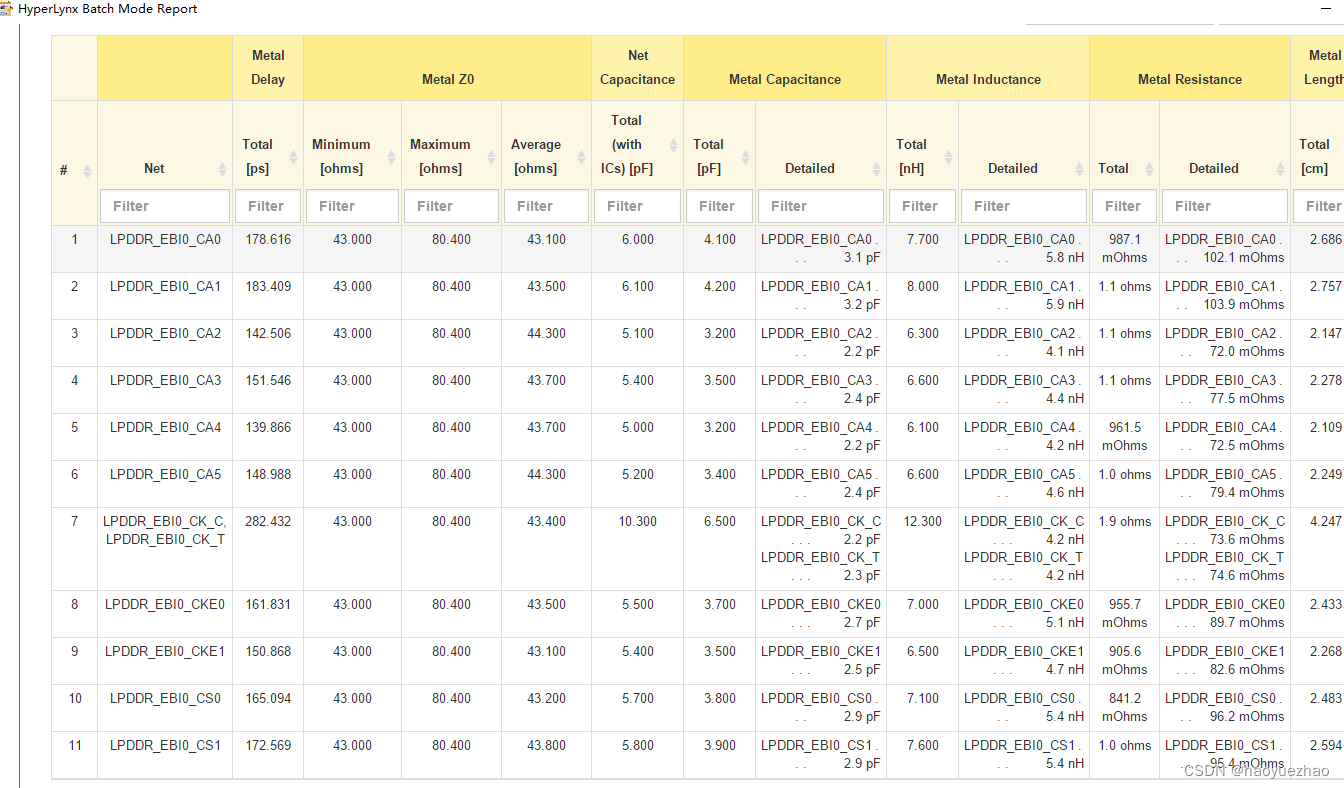

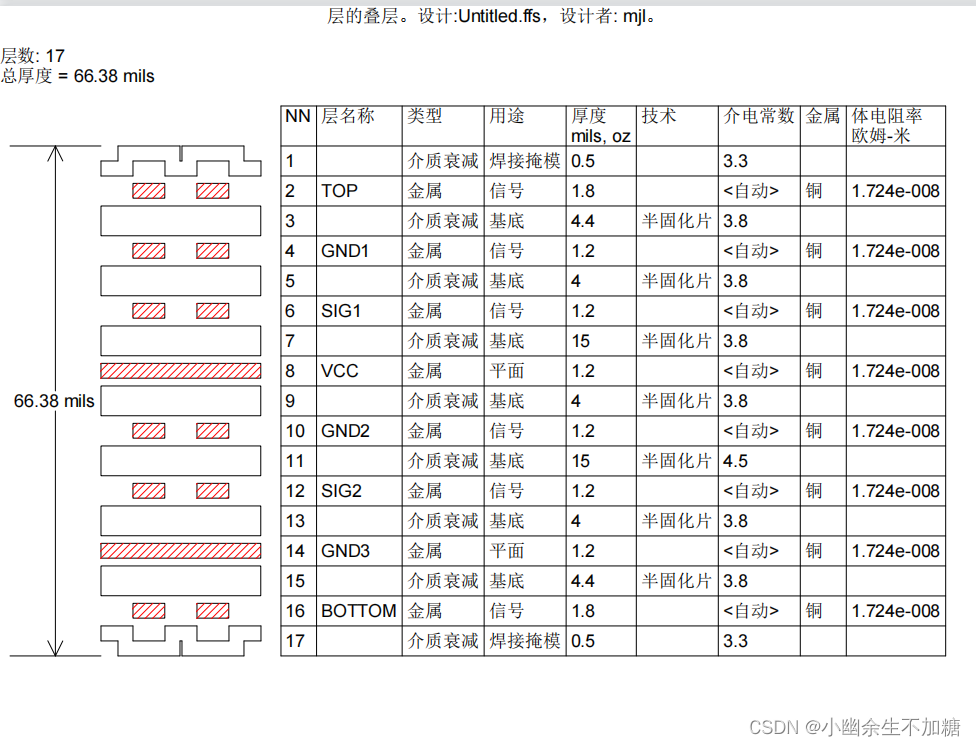

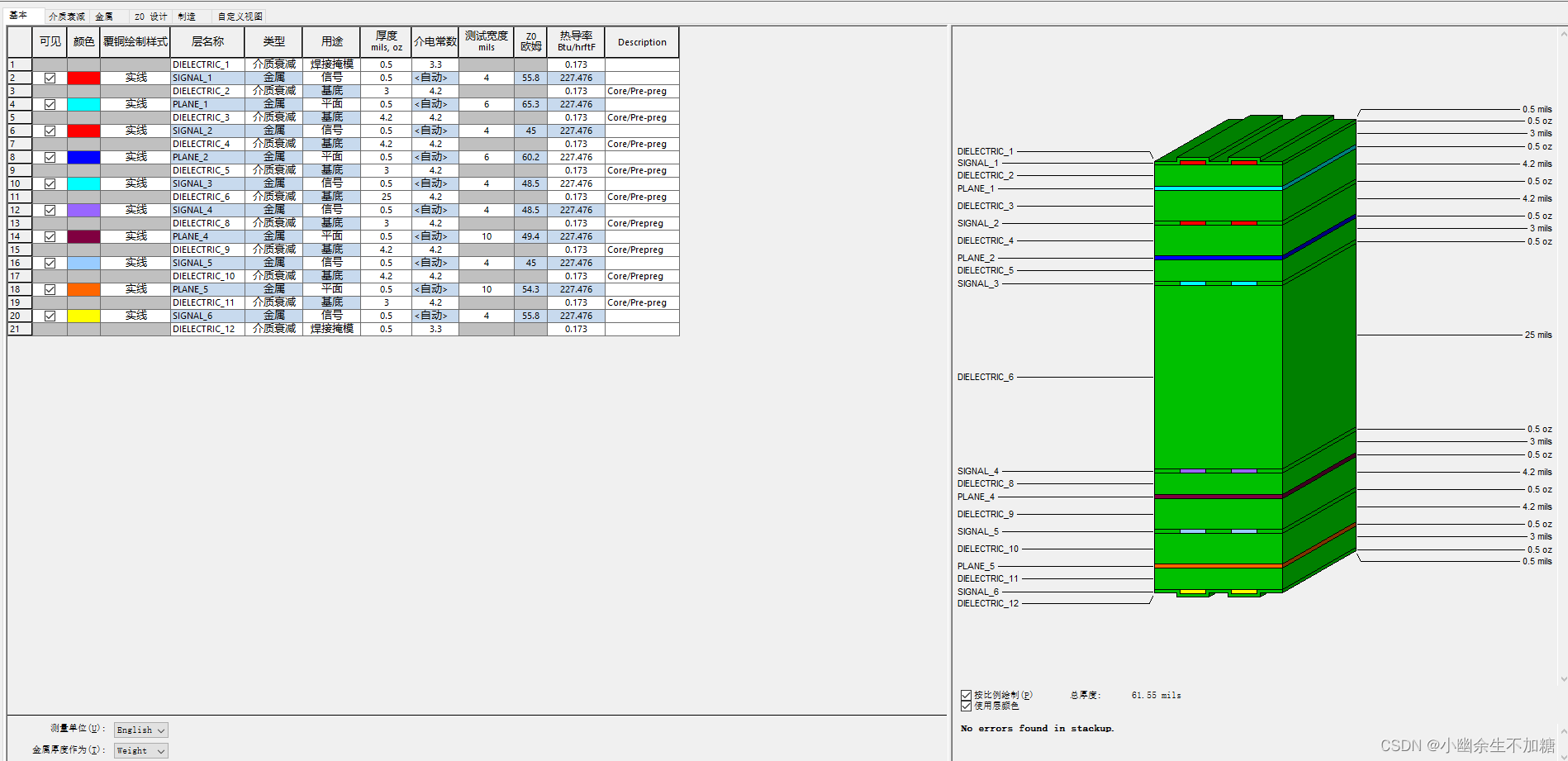

转换好文件后,需要对仿真文件进行层叠和电源原设置。本例的层叠结构如表所示,

共6层,使用的材料为高 TG 值的 FR4 材料,总厚度为50mil。

层叠设置好并确定没有错误提示之后,接着设置仍方真文件的电源网络电压。一般每个项目都会有比较多的电源,如12V、3.3V、1.5V、1.2V、0.75V等,仿真文件中如果电源网络很多,并不需要把所有的电源网络都设置(如果原理图设计比较规范,仿真文件中的电

源就不需要重新设置了,软件会自动分配好),只把与 DDRx仿真有关的电源网络设置好即可,如与DDR3有关的电源网络包含DDR3的工作电派原、VTT上拉电源和参考电源以及参考地网络,本例中只需要设置1.5V、0.75V_VTT和G ND_POWER。1.5V 为1.5V、0.75V_VTT为0.75V,GND_POWER为0V。

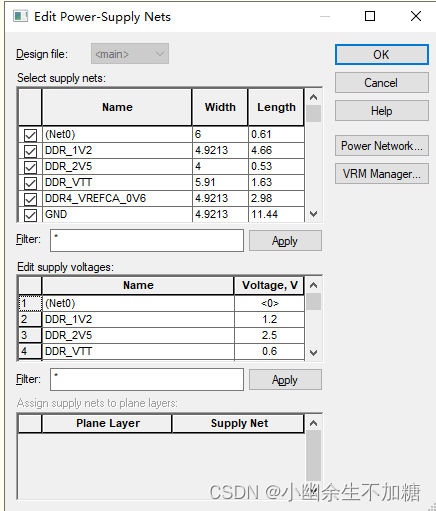

在菜单栏上选择设置(Setup)→电源供应(Power Supplies),在弹出的窗口中编辑有关的电源网络,如图所示:

层叠和电源设置完毕后,如果有需要,可以在工具栏上勾选串扰和损耗因子使能选项。一般建议开启这些功能。

接下来设置仿真模型。仿真模型可以在开始仿真之前设置,也可以在仿真向导中设置,但建议工程师在仿真之前设置。首先需要把相关模型放在模型库路径下或者与仿真文件一起放在根目录下。本例中以 IBIS模型为主。

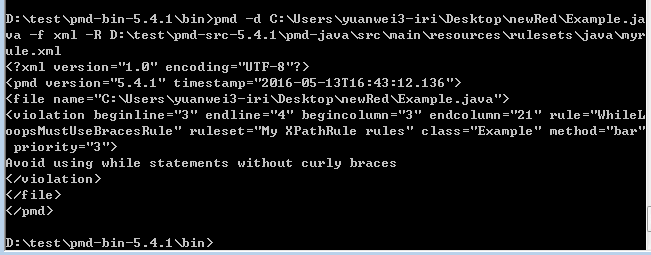

建议工程师在设置模型之前先对模型进行验证。看模型是否正确。这主要是验证模型的语法、模型的 pin 对应、I/V曲线等

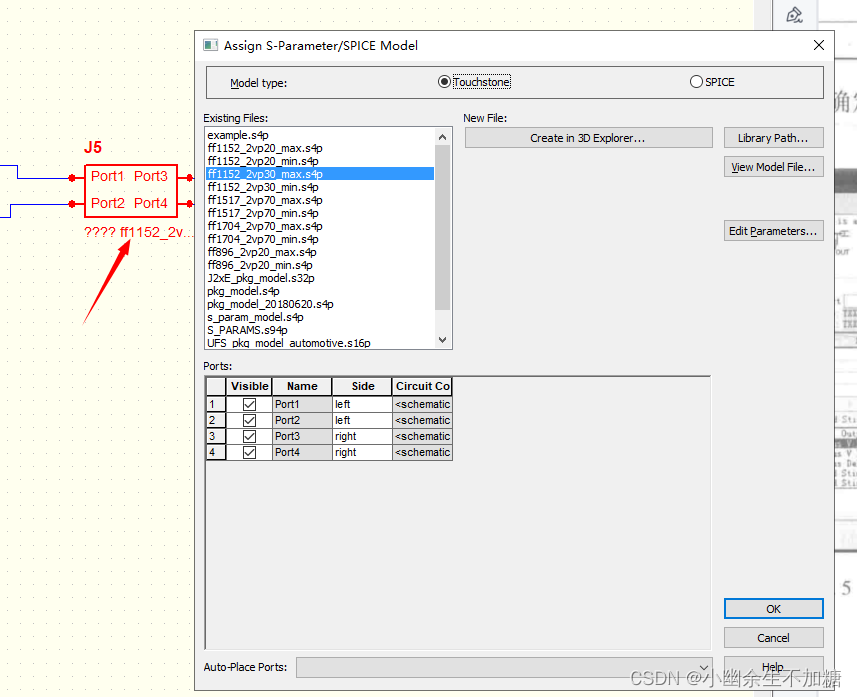

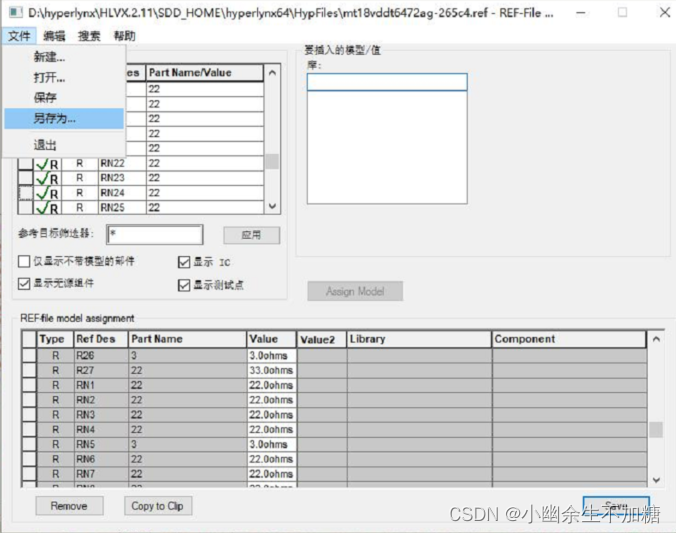

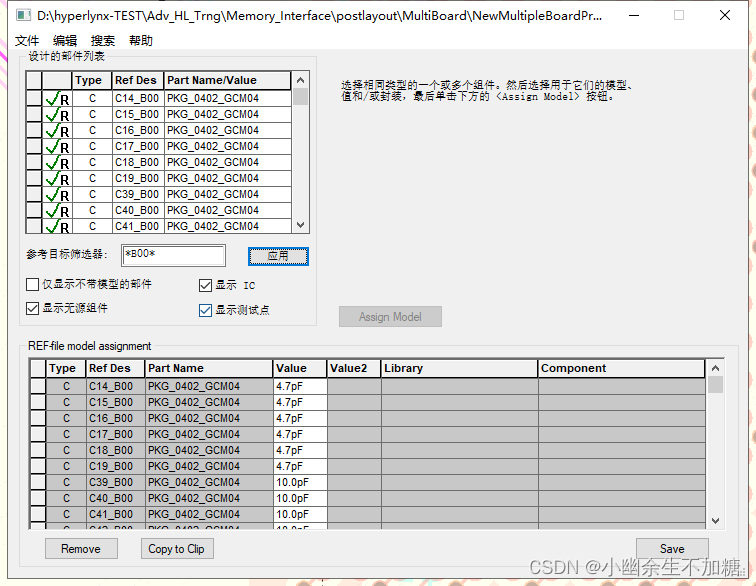

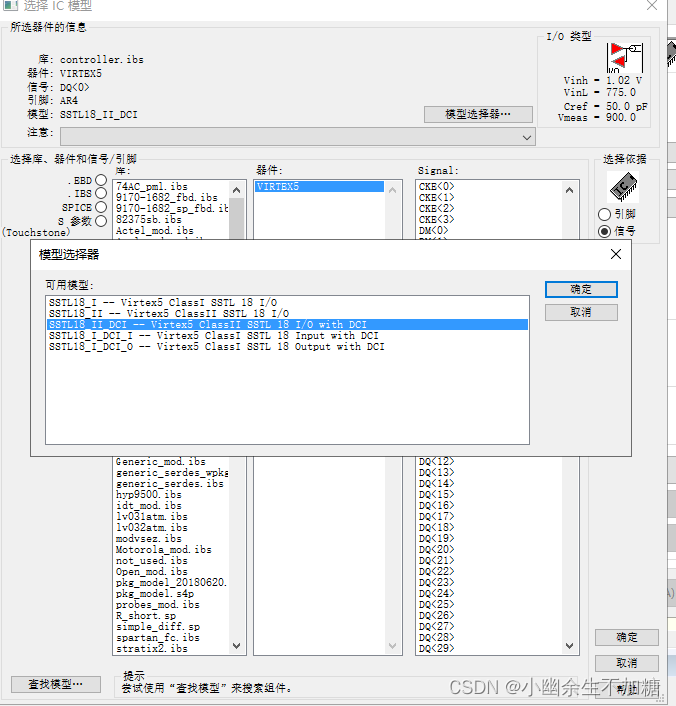

两个模型都没有任何问题时,在菜单栏上选择模型(Models)→通过参考位号分配模型/参数值(Assign Models/Values By Reference designa ator(.REF File)),弹出赋模型/参数值窗口如图所示:

在这个窗口中可以对CPU、DRAM 以及各分立元器件赋予模型和值。对芯片赋模型时,

首先要选择芯片对应的位号,由于元器件比较多, 通过过滤器选择芯片,然后选择位号 U1,

选中后,所在的列会变为黑色,然后在模型库中选择模型类型,在元器件/模型一栏中选择

具体的模型的名称,最后单击 Assign Model 按钮, 即完成芯片赋模型,如上图所示

分配好模型后,在位号前会出现还标记。使用同样的方法,给DRAM 颗粒分配模型。

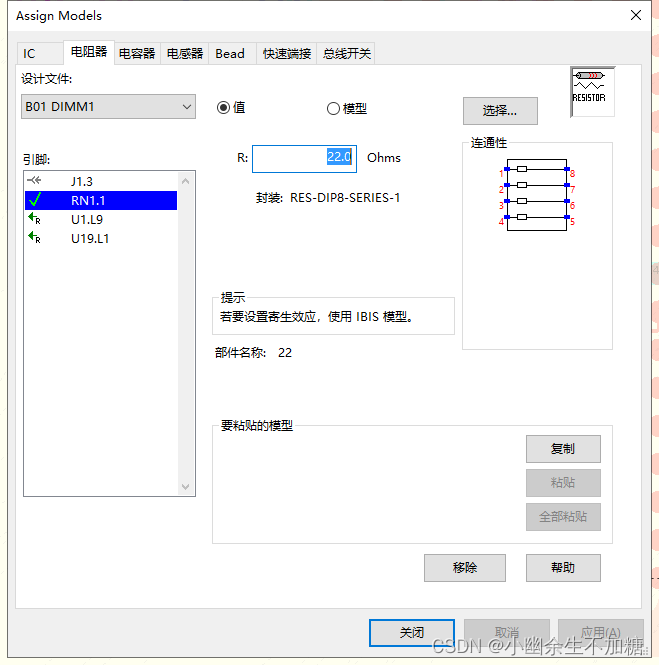

控制器和DRAM 分配完模型后,还需要对相应的的分立元器件赋值,可以使用相同的方法,但在赋值时,直接赋给相应的参数值,以电阻方为例,如上图所示为对电阻器件赋值,本例中,控制信号、命令信号、地址信号和时钟信号的端接电阻都为22Ω。

同理,可以对对应的电容赋参数值。在对所有与 DDR3网络相关的元器件赋模型或参数

值后,需要保存,即在分配模型窗口的菜单栏上选择文件(File)→保存(Save)或另存为(Save As…),如图所示:

保存后,关闭模型分配窗口,完成芯片模型的分配和分立器件参数赋值。

3.批处理仿真前验证

所有工作都已经准备完成并开始向导仿真前,可以选择某一个网络进行仿真实验,确定设置是否正确,如选择一个地址信号DDR_A00,如图所示:

4.DDR2总线批处理仿真(实例)

在这个实验中运行DDRx向导仿真。

4.1 收集设计信息并为DDRx向导准备设计电路

(1)从以下路径打开多板工程MBD_2R-2Rpjh;C:\Adv_HL_Trng\Memory_Interface\ postlayout \MultiBoard。

①选择“File”→“Open Multiboard Project”。

② 指定到以上路径。

③ 单击“Open”按钮。

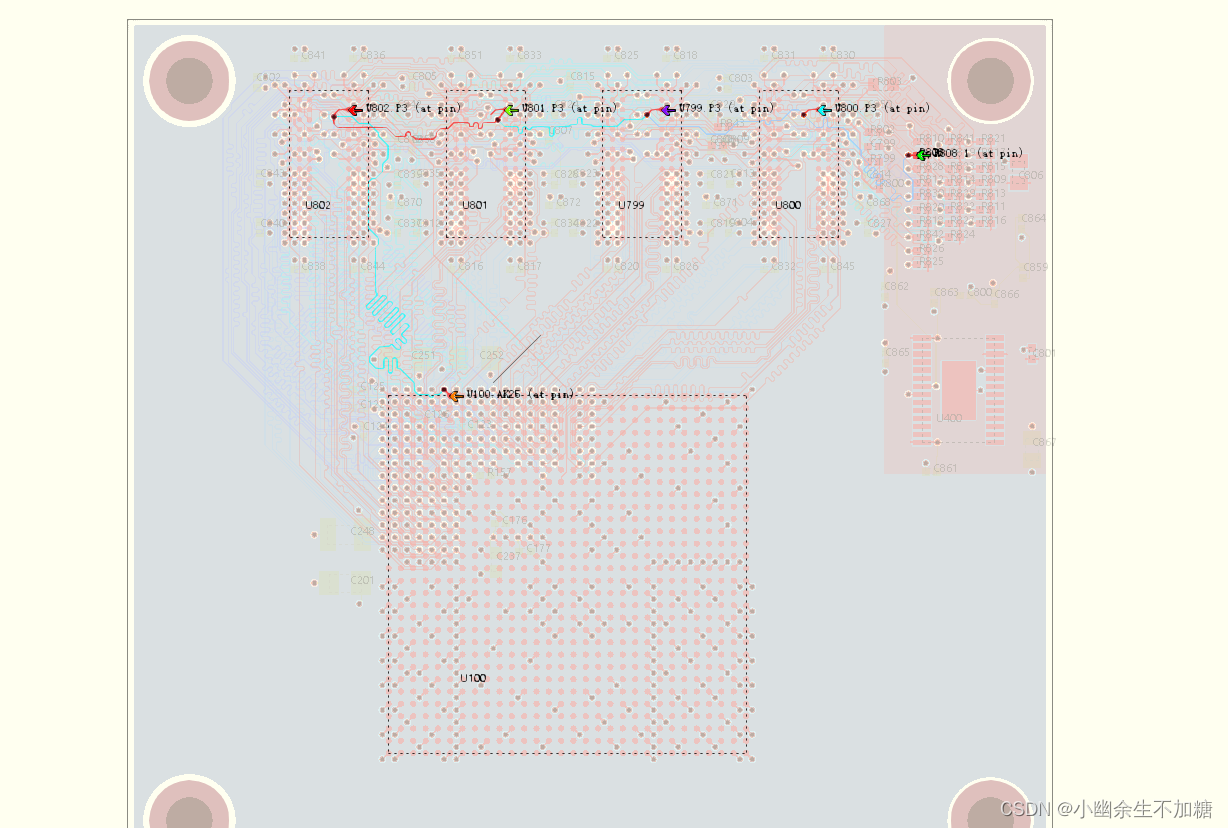

下面将集中精力验证数据字节通道的连续性,如图所示:

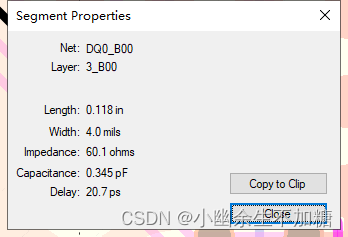

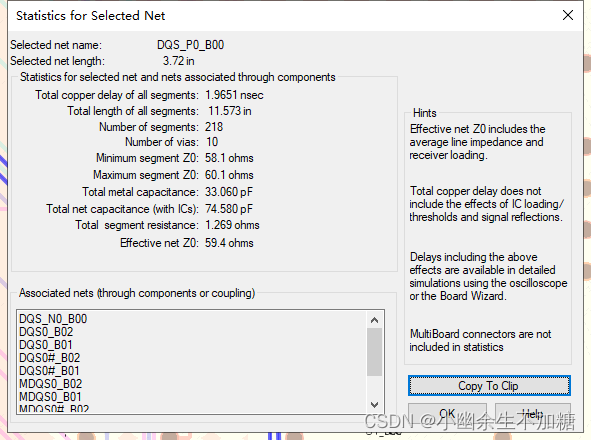

(2)选择网络“DQ0”,如图所示:

(3)从图中信息可以看出:

①在控制板上,DQ0网络的总长度是3.85in;

②可以看到这个网络在3_B00层;

③这个网络的线宽是4.0mil;

④阻抗是60.1ohm。

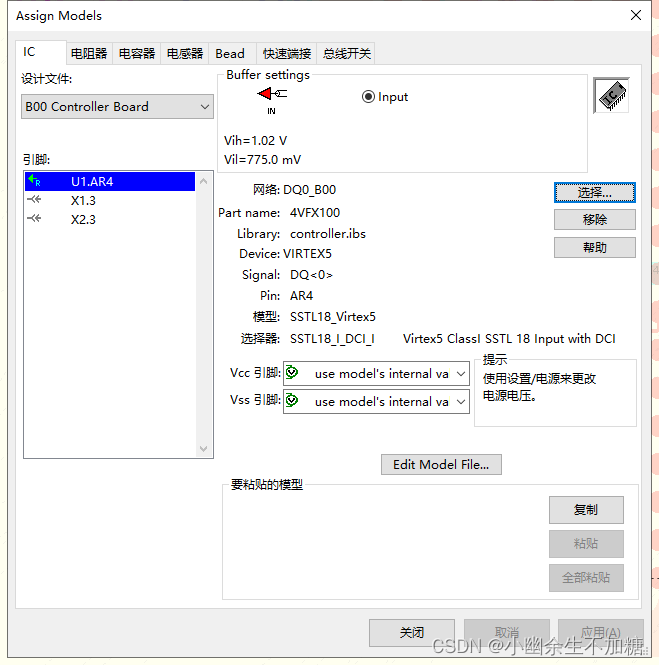

(4)使用COMP按钮打开分配模型对话框,从设计文件下拉列表中选择“BOO Con troller Board”,如图所示:

【注意】U1还没有分配模型,将使用REF文件为其分配模型。对于DDRx向导仿真没有任何问题,相关部分必须用.ref文件分配IBS模型。

(5)关闭“Assign Models”对话框。

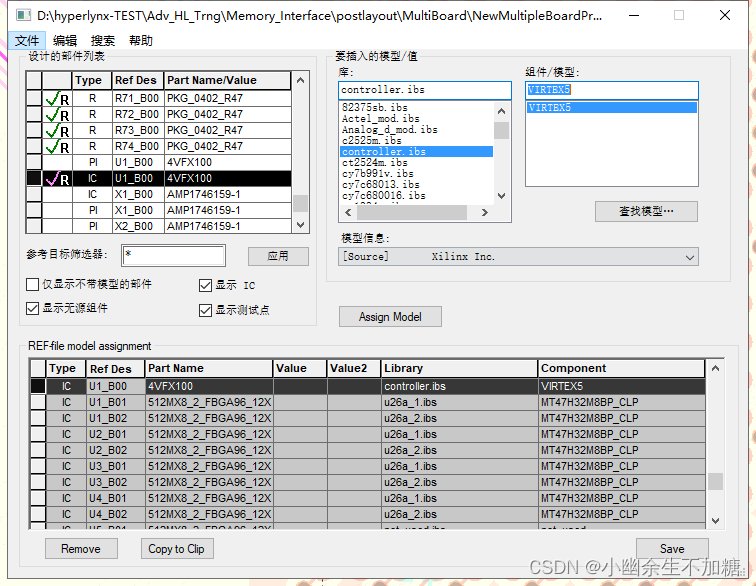

(6)为U1B00分配模型controller.ibs

①选择“Models”→“Assign Models/Value byReference Designator”

②在Refdes中输入“B00",如图所示,单击“Apply”按钮。

③取消选中“show passive components”

④从列表中选择“U1_B00行”。

⑤在库选择中使能“IBS/EBD”选项。

⑥从下拉列表中选择“controlleribs”,如图所示:

⑦上单击“Assign Model”按钮。

⑧选择“file”->“save”;

⑨选择“file”->“exit”。

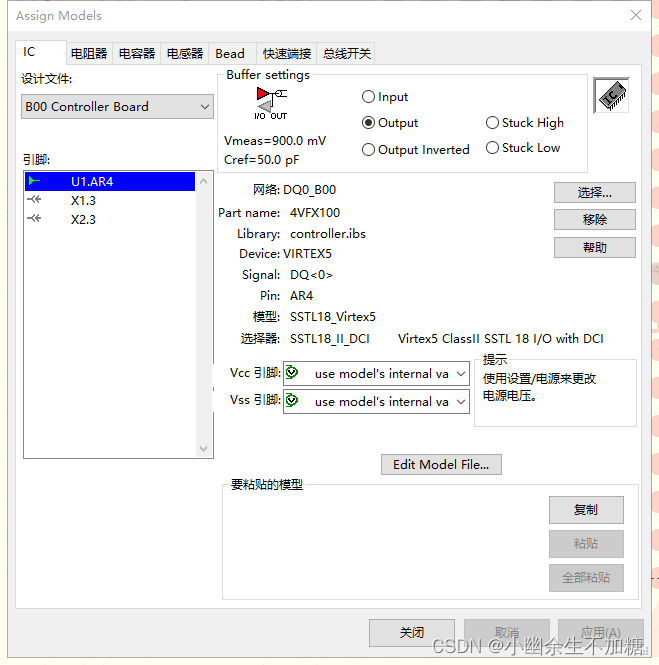

(7)再次打开DQ0网络的分配模型对话框,可以发现U1.AR4已经有了一个模型,如图所示:

(8)设置缓冲类型为“Output”,如图所示:

(9)从“Design”下拉列表中选择“B01 DIMM1”,在"Pins"栏选择"RN1,1",单击“Resistor”选项卡,确保DIP8-Series package被分配,如图所示:

【提示】如果电阻没有被分配到一个正确的封装类型,那么DDR向导连接将会被中断,也就无法输出正确的仿真结果。

(10)观察所有的已经使用REF文件分配模型的缓冲器,前面都有标号R;

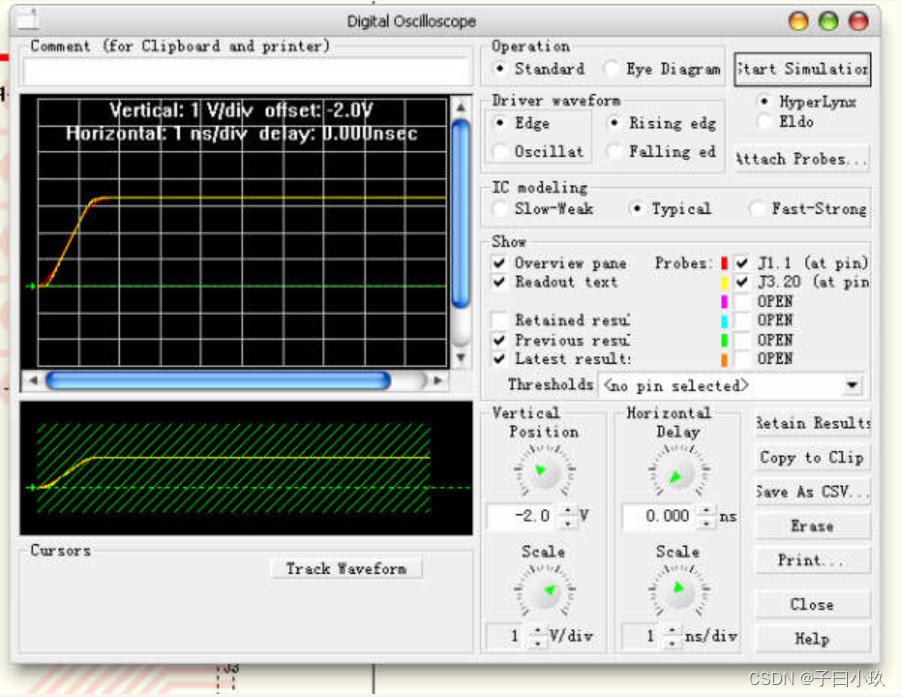

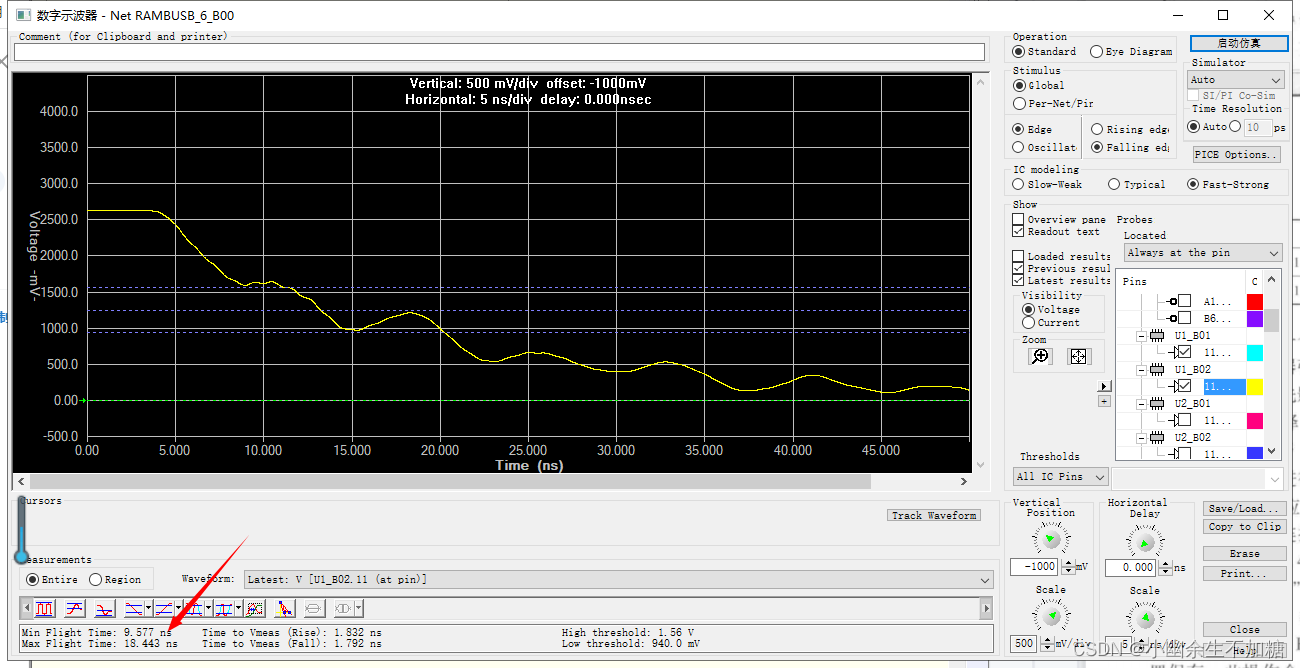

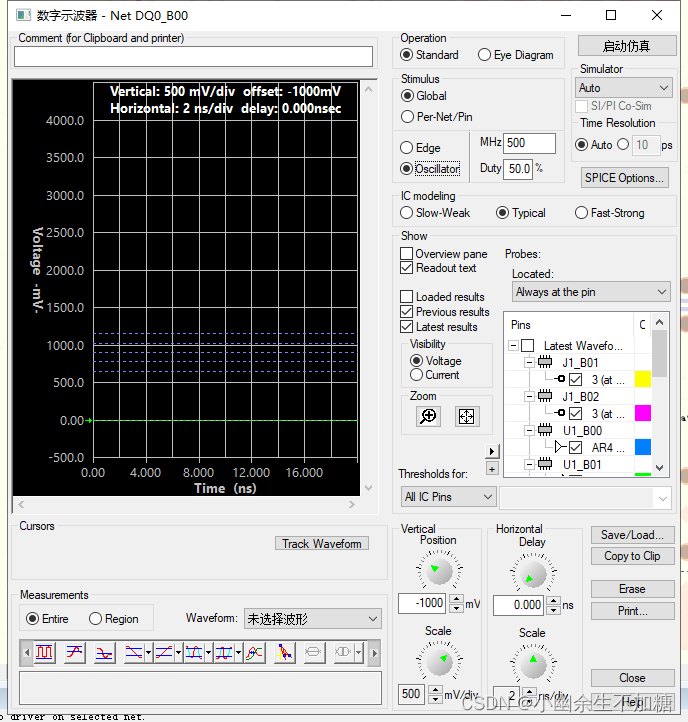

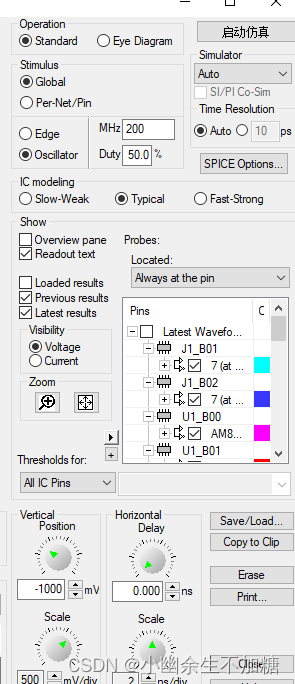

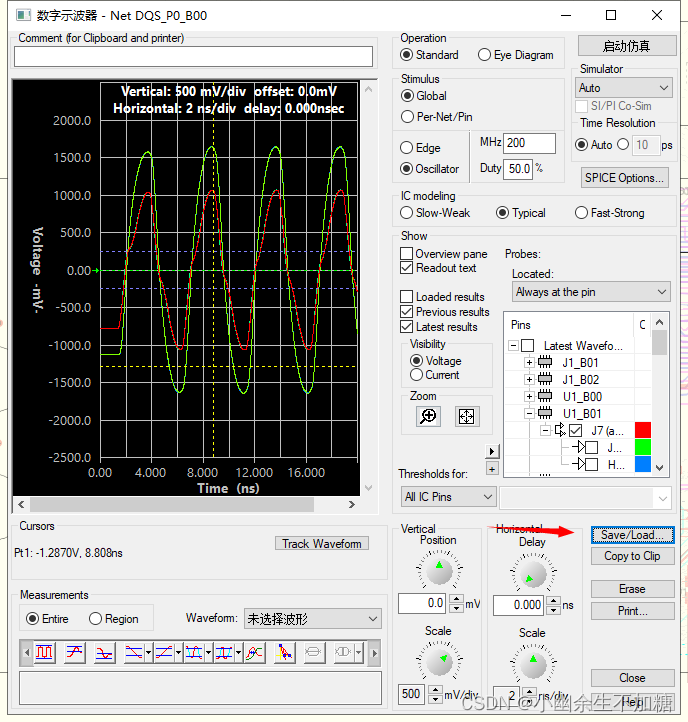

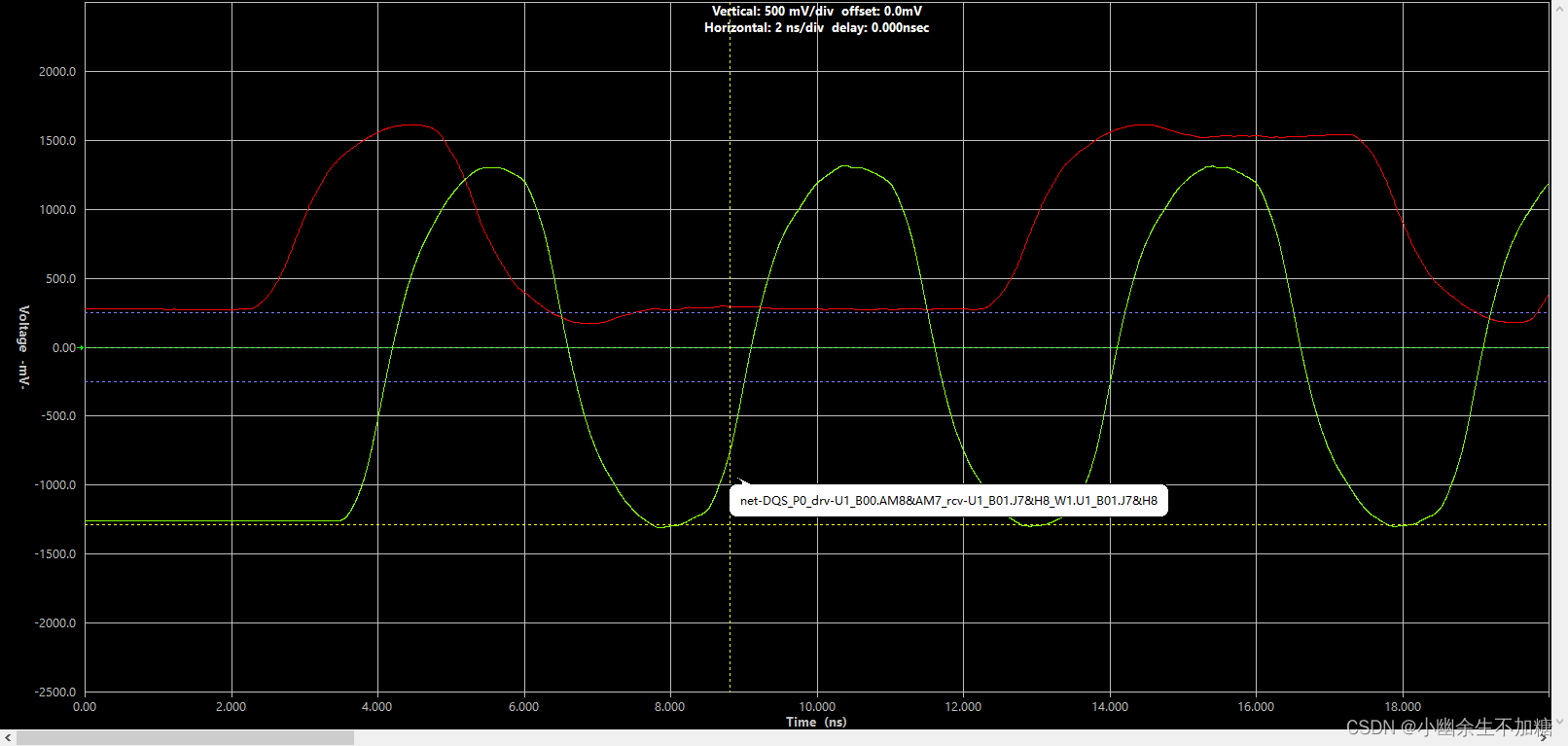

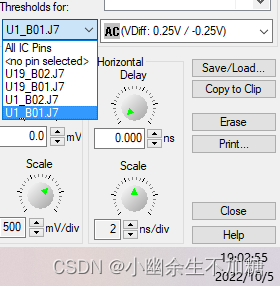

(11)打开示波器,设置以下参数,如图所示:

激励:Oscillator200MHz

垂直刻度:500mV/diy

水平刻度:2ns/div

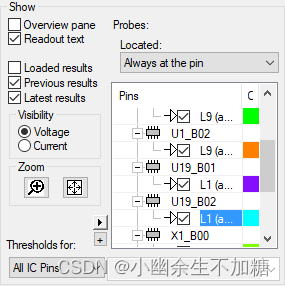

(12)单击按钮,选择“Disable all probes”,然后只选中接收端探针“U1_B01L9”“U19 BO1L1”“U1 B02L9”和“U19B02L1” 如图所示:

(13)单击“Start Simulation”按钮。

(14)单击Waveform查看仿真运行的结果,如图所示。

①确认波形越过了阈值。

②确保电压如预期的一样。

接下来,将通过检查DQS信号来查看信号连接的正确性。

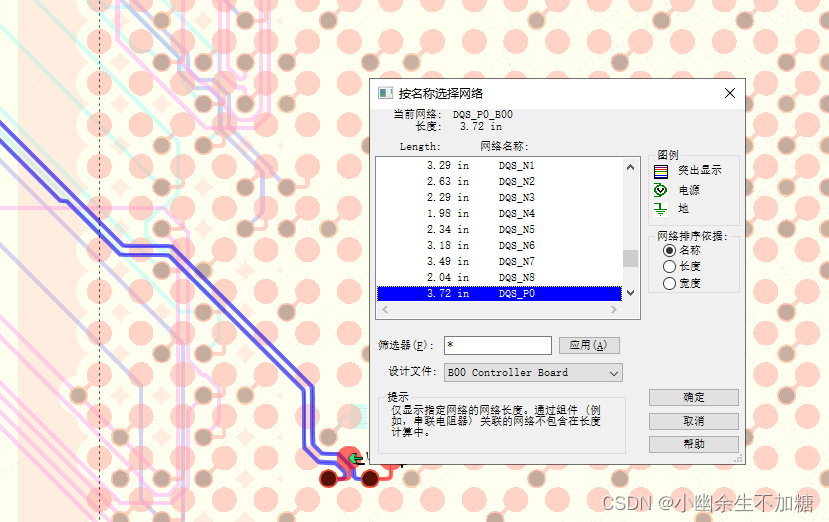

(15)选择“DOS_PO”网络,如图所示:

(16)确保DOS_NO也同时自动被选中,这表示该引脚在在IBIS模型中是被定义在[Diff Pin] 关键字下的。

(17)查看关于这个网络的以下信息:

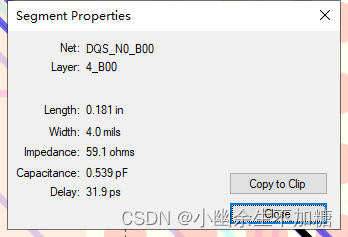

①选中一条线,单击鼠标右键选择“View”,查看控制器板上网络的差分阻抗是60.147ohms,如图所示:

②选中一条线,单击鼠标右键选择“View Segment Properties”,查看网络所在的层是“4_B00”,如图所示:

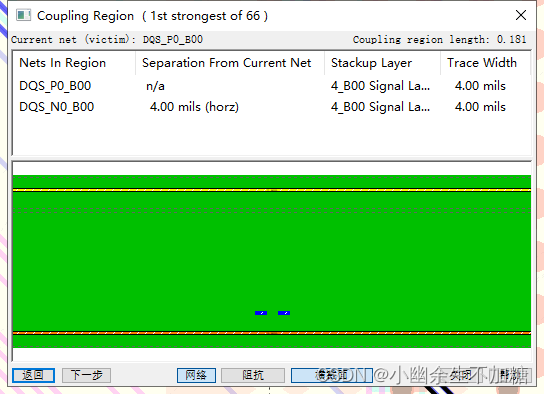

选择“View”“Coupling regions”,打开如图所示对话框:

③差分对两个网络的间距是4mil。

④网络的线宽是4mil。

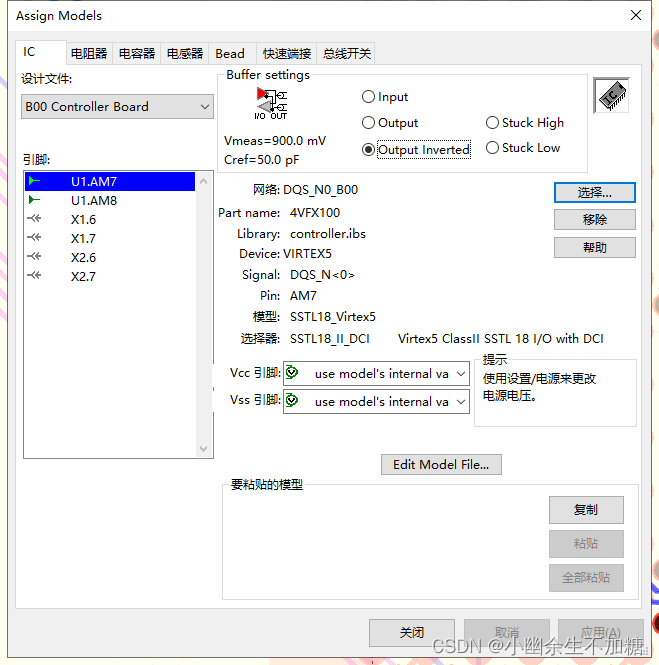

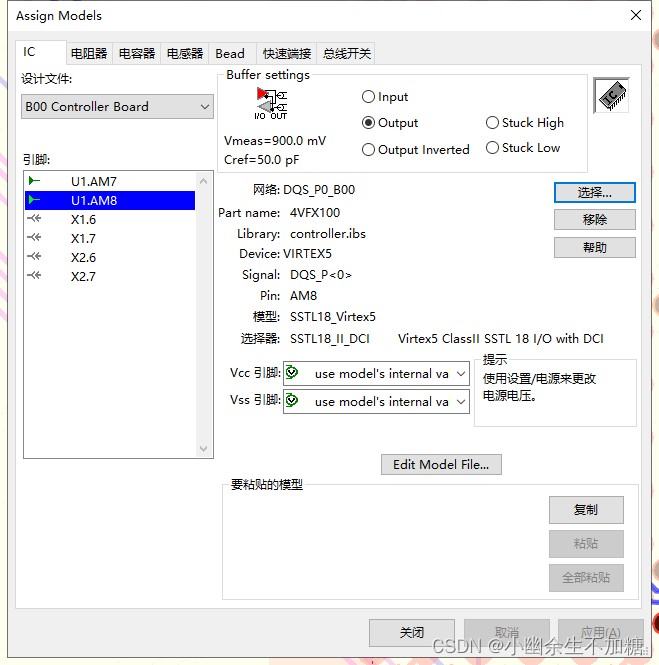

(18)确保在B00 Controller板上,U1.AM7缓冲类型设置为“Output Inverted”,U1.AM8缓冲类型设置为“Output”,如图所示:

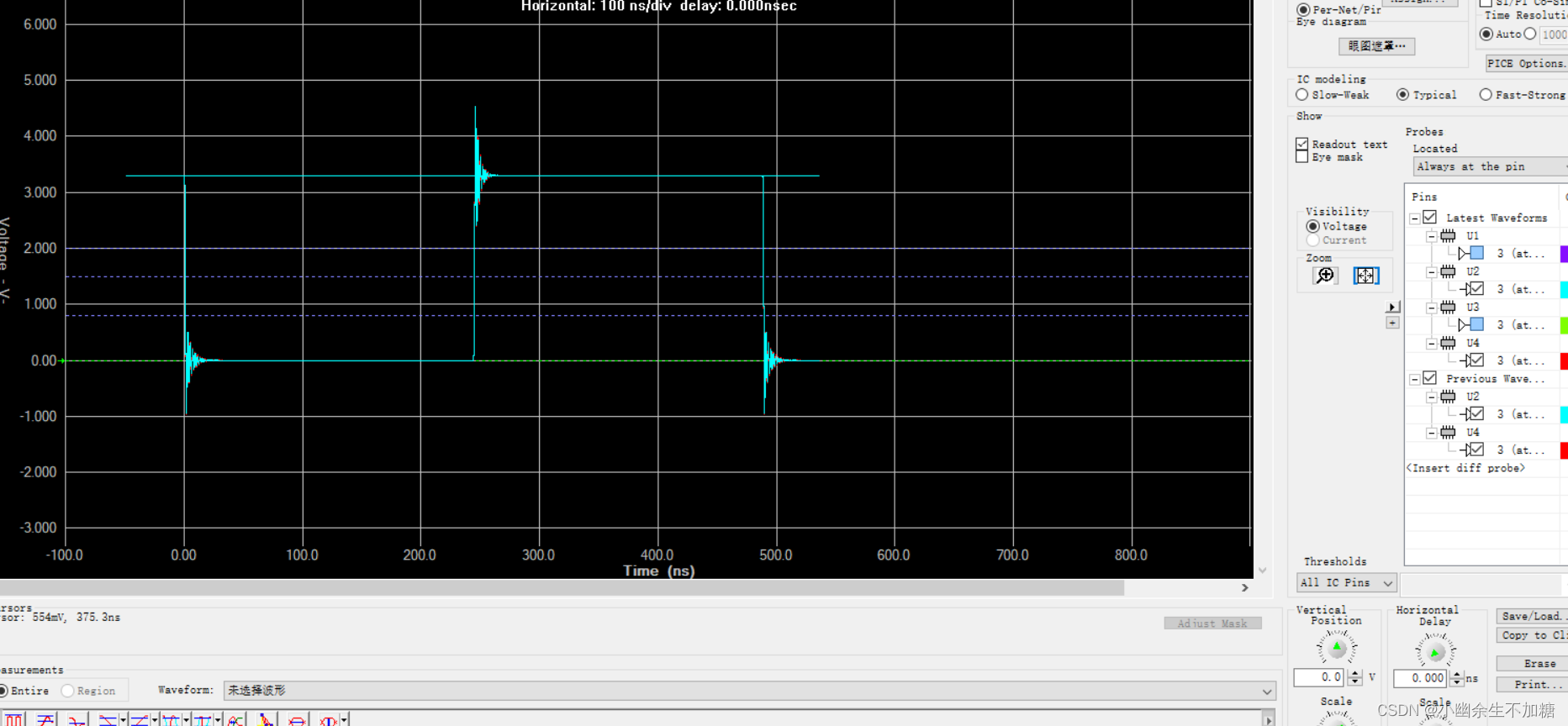

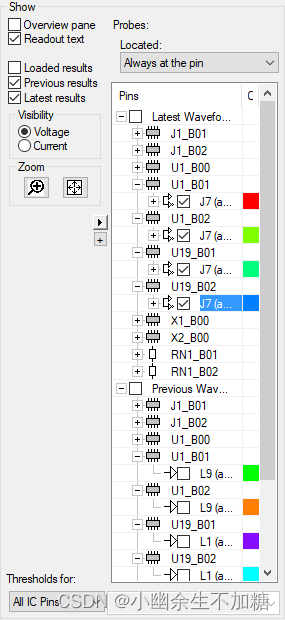

(19)打开示波器,设置以下参数。

激励:Oscillator,200MHz

垂直标尺:500mV/div

水平标尺:2ns/div

(20)在示波器中单击口按钮,选择“Disable all probes”。

(21)使能接收端的差分探针“U1_ B01J7/J8”、“U19_B01J7/J8”、“U1_B02 J7/J8”和“U19_B02J7/J8”。

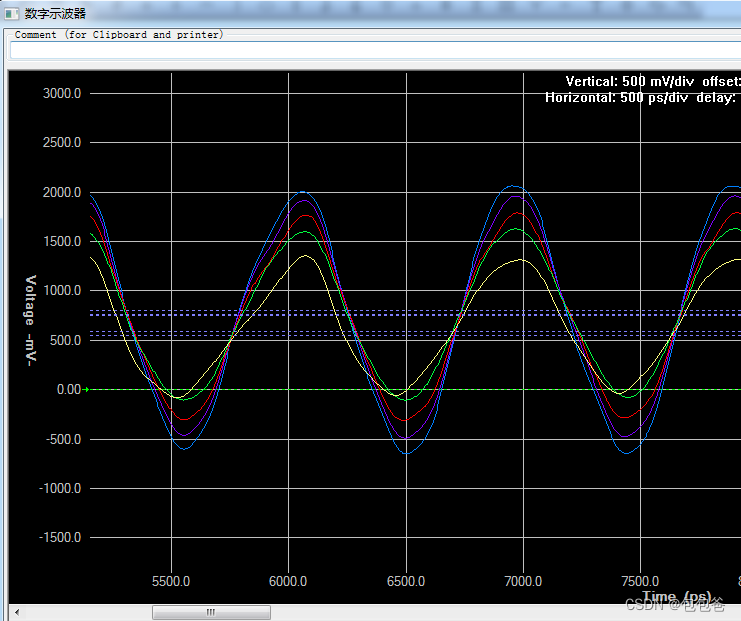

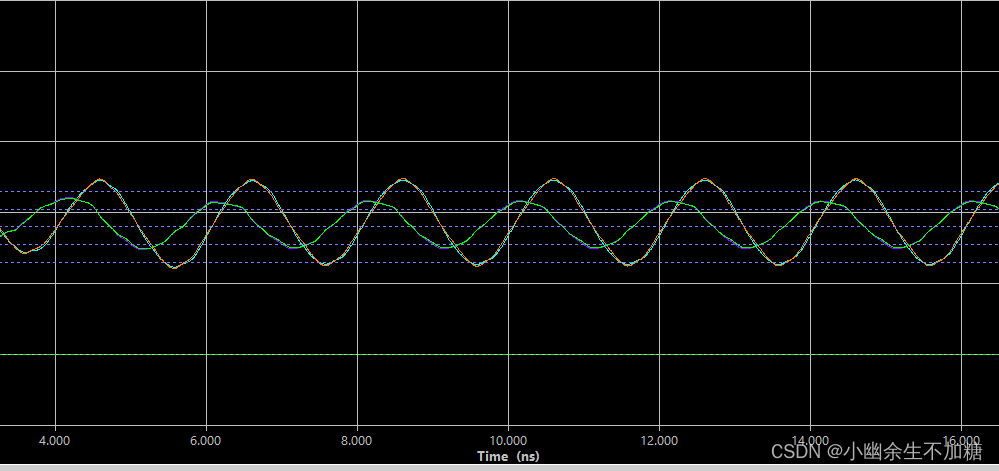

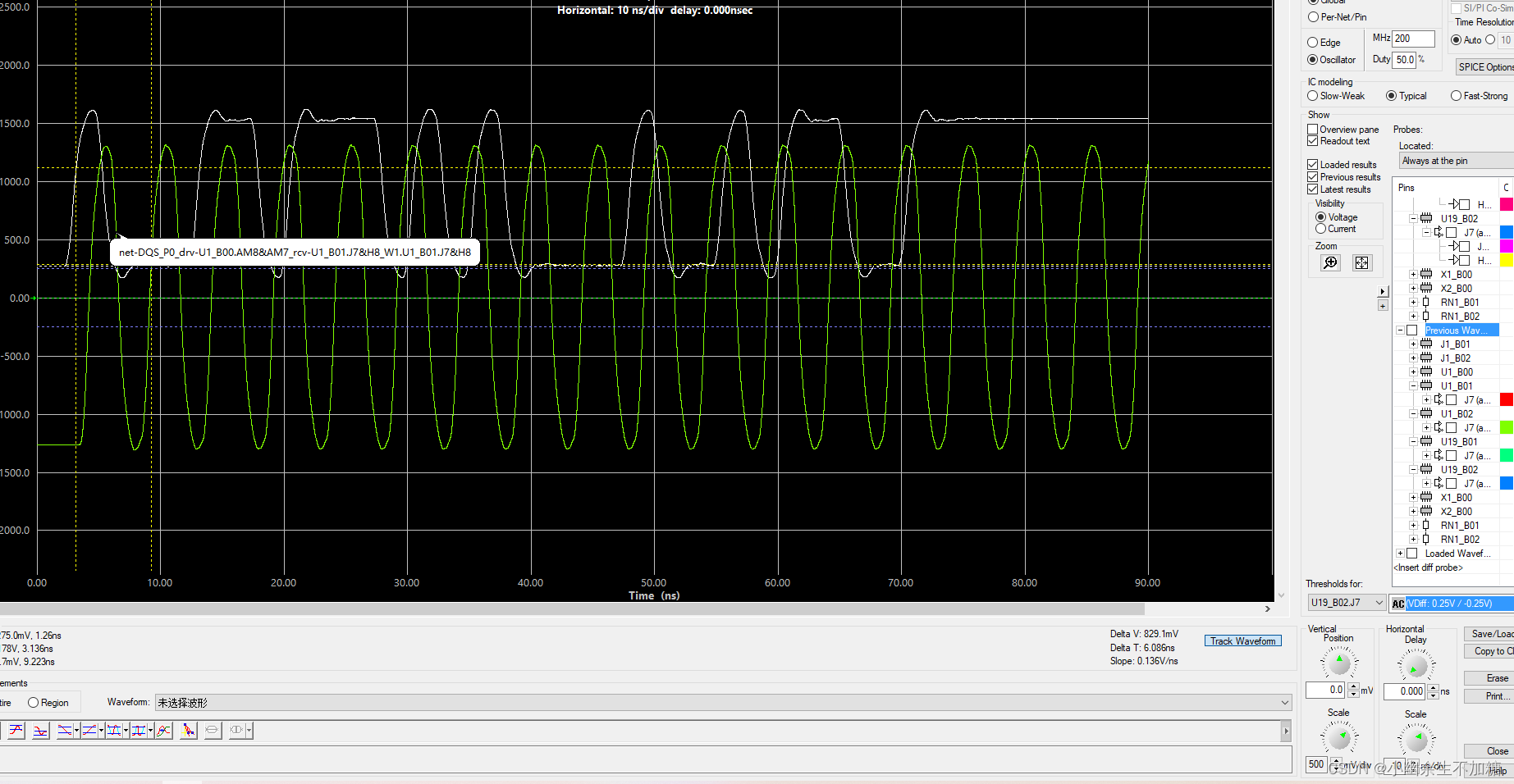

(22)通过波形查看仿真运行情况,如图所示:

①确保差分波形集中在0V;

②确保电压和预期的一样。

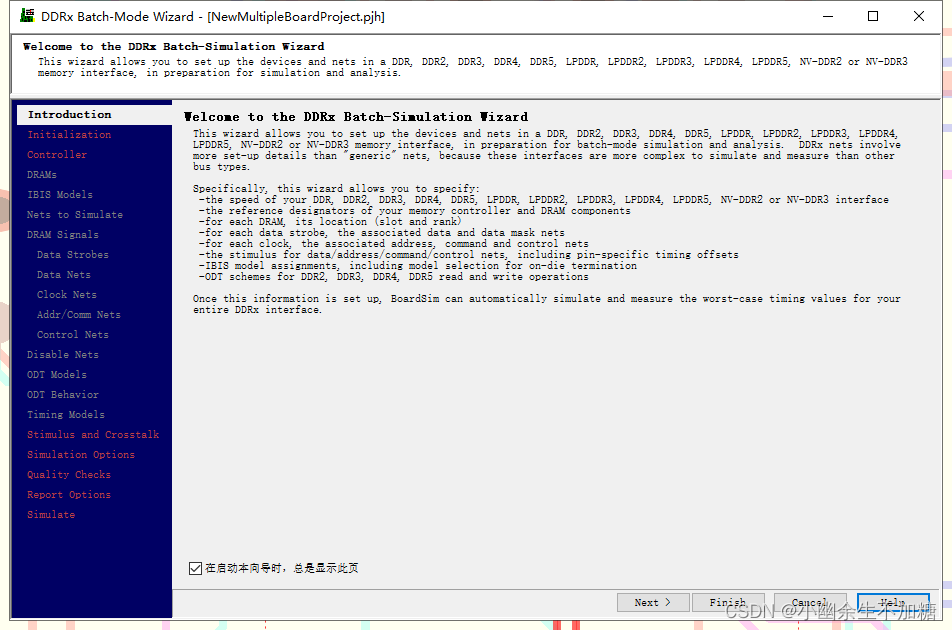

4.2 设置DDRx向导

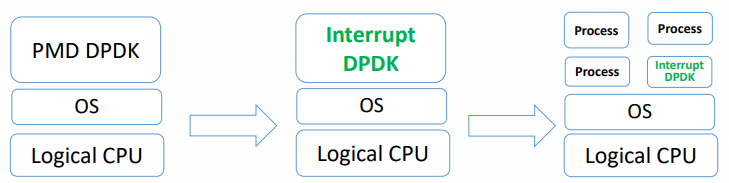

在本节练习中,将设置DDRx向导,对没有缓冲的DDR2接口数据字节通道进行仿真。

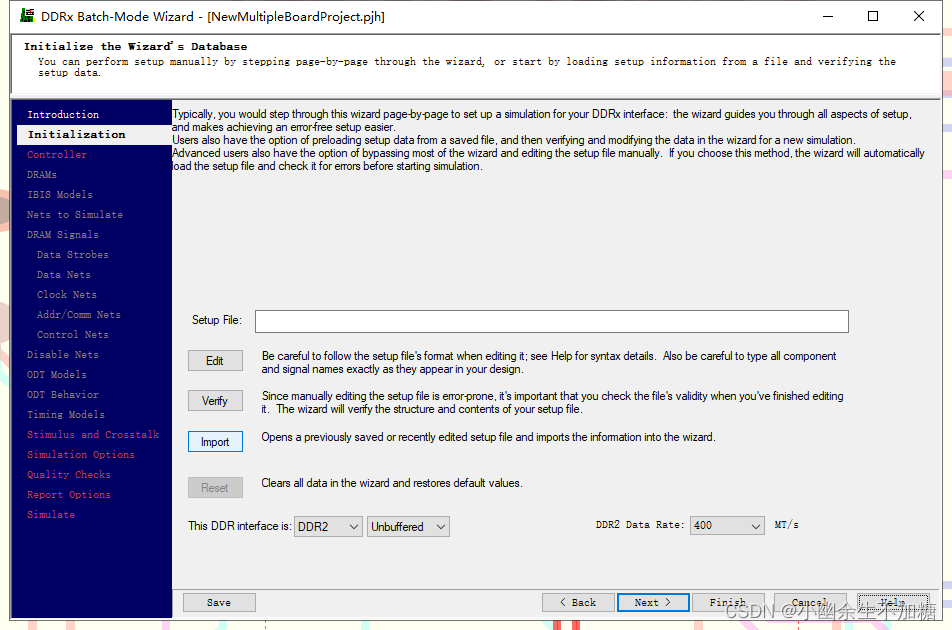

(1)选择“Simulate SI”“Run DDRx Batch Simulation”在这个页面,需要选择DDR的接口类型。

(2)在介绍页面,如图所示,单击“Next”按钮。

(3)确保“DDR2”和“Unbuffered”被选中(默认设置),如图所示:

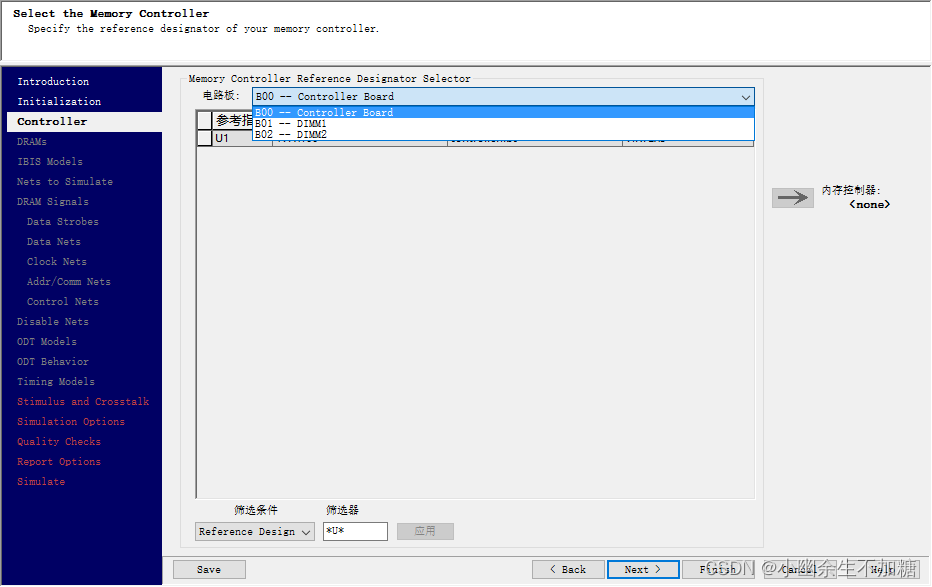

(4)选择“DDR2DataRate”为“400MT/s”,单击“Next”按钮,从板子的下拉列表中选择“B00-Controller Board”如图所示:

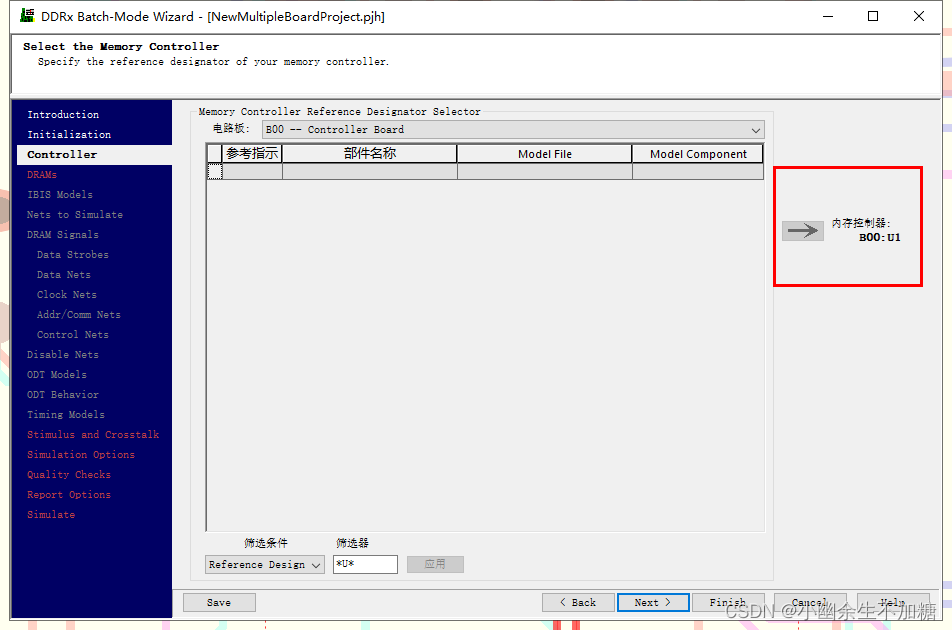

(5)选择Ref Des U1行,单击->按钮,分配它作为存储控制器,如图所示,单击“Next”按钮:

【注意】可以通过“RefDes”或者“Partname”来过滤元器件。默认的设置为“Ref Des”,“Filter”设置为“U”。为了列出板子上的所有元器件,在“Filter”区域输入“*”,单击“Applyv”。

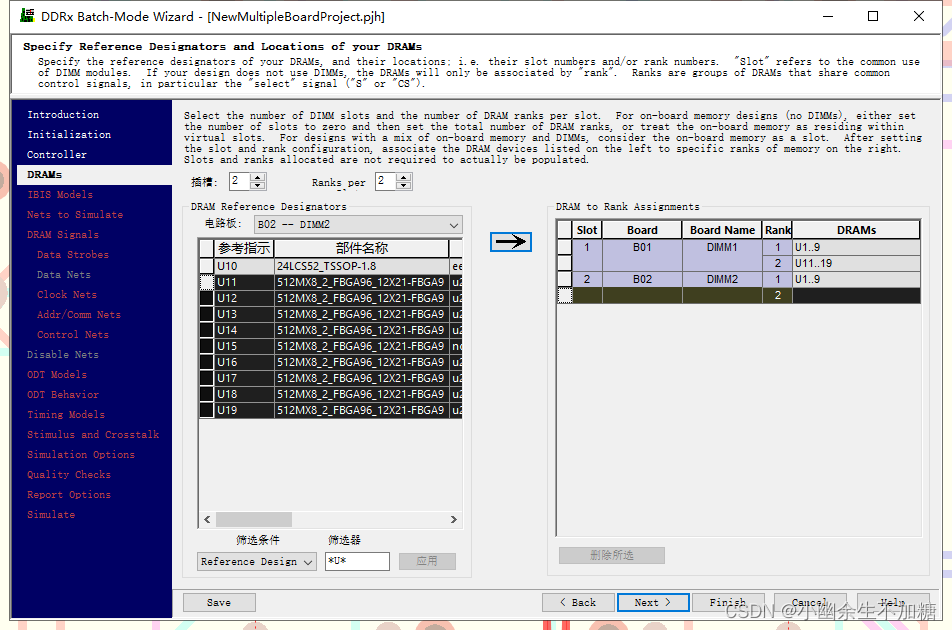

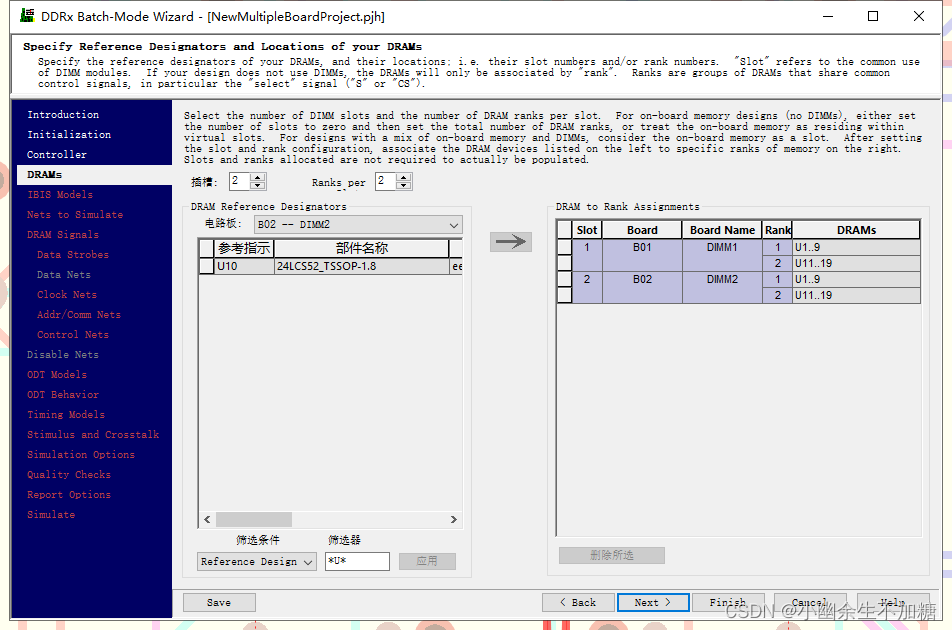

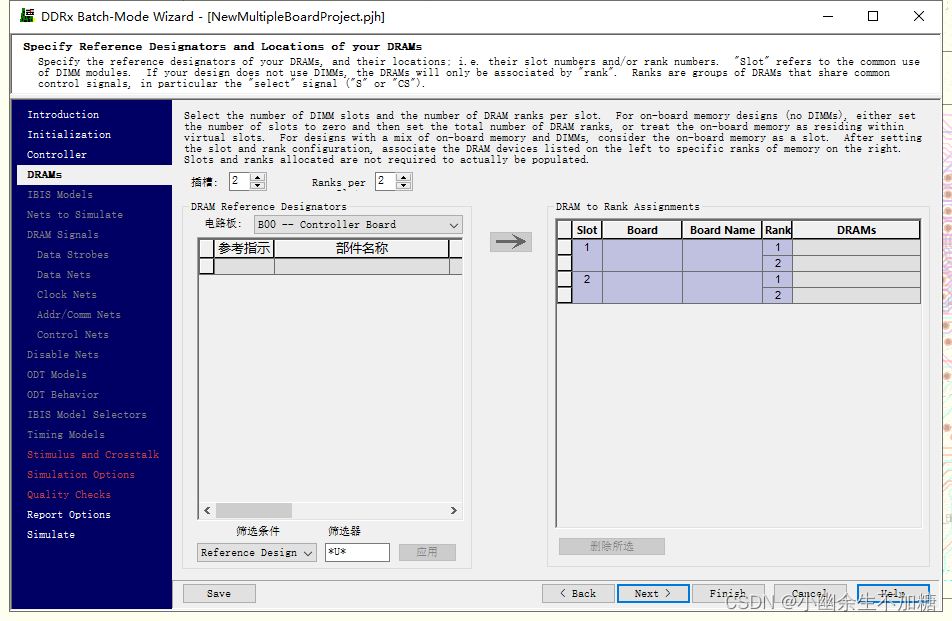

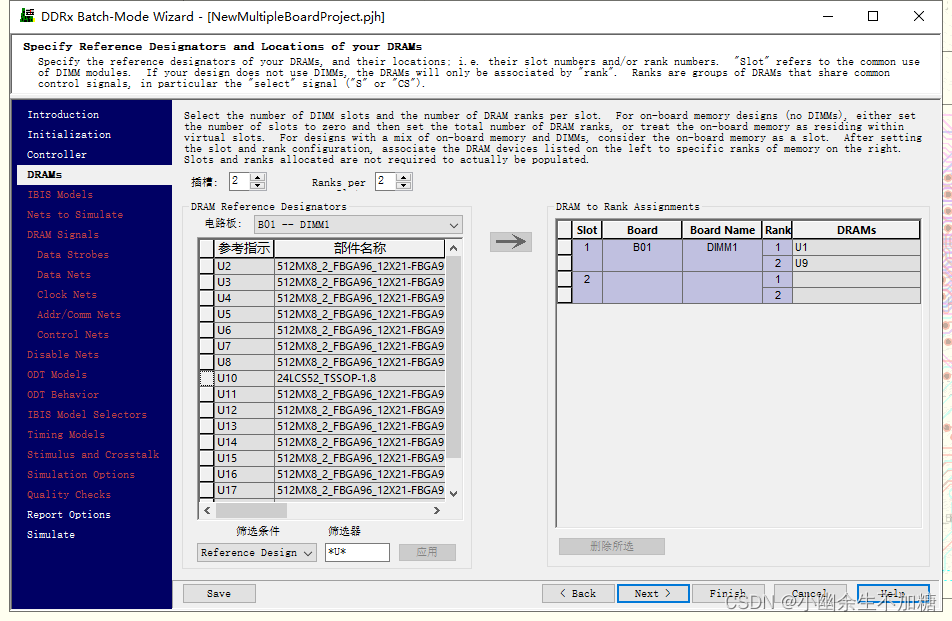

(6)从“Board”下拉列表中选择“B01–DIMM1”,选择“U1”~“U9”,单击 Slotl和Rank1,单击->按钮,如图所示:

(7)选择“U11”~“U19”全部器件,设置Slotl和Rank2,如图所示,然后单击→按钮。

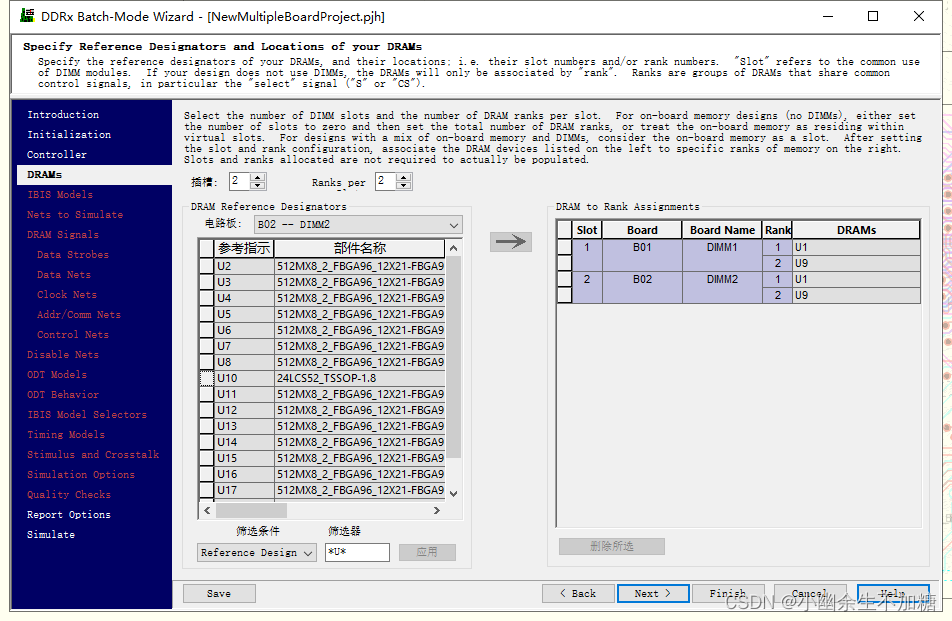

(8)从“Board”下拉列表中选择“B02–DIMM2”,选择“U1”~“U9”全部器件,设置Slot2和Rank1,如图所示,然后单击→按钮。

(9)选择“U11”~“U19”全部器件,设置Slot2和Rank2,如图所示,然后单击→按钮。

这样,就为整个DDR2接口填充了所有的DRAM

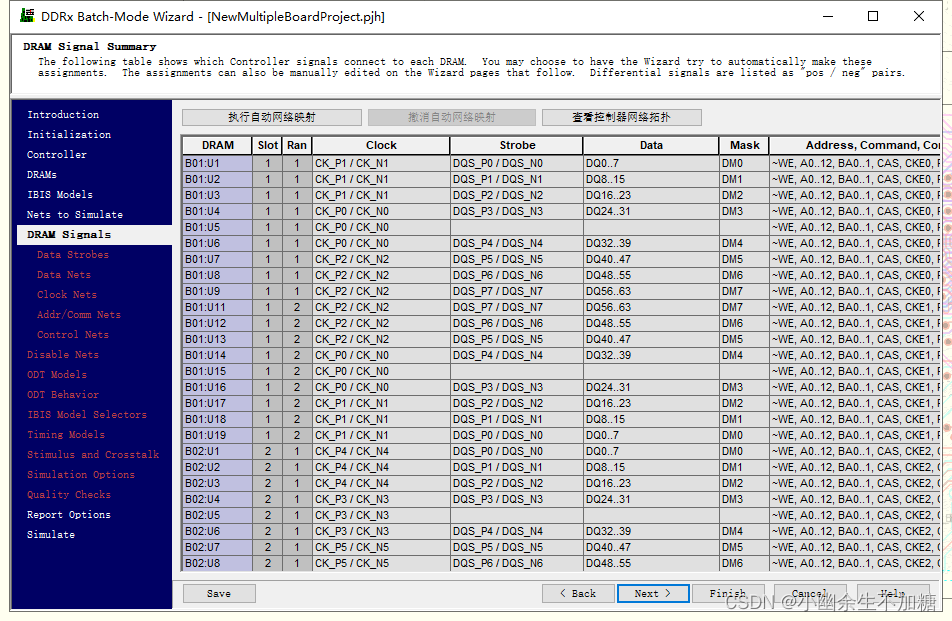

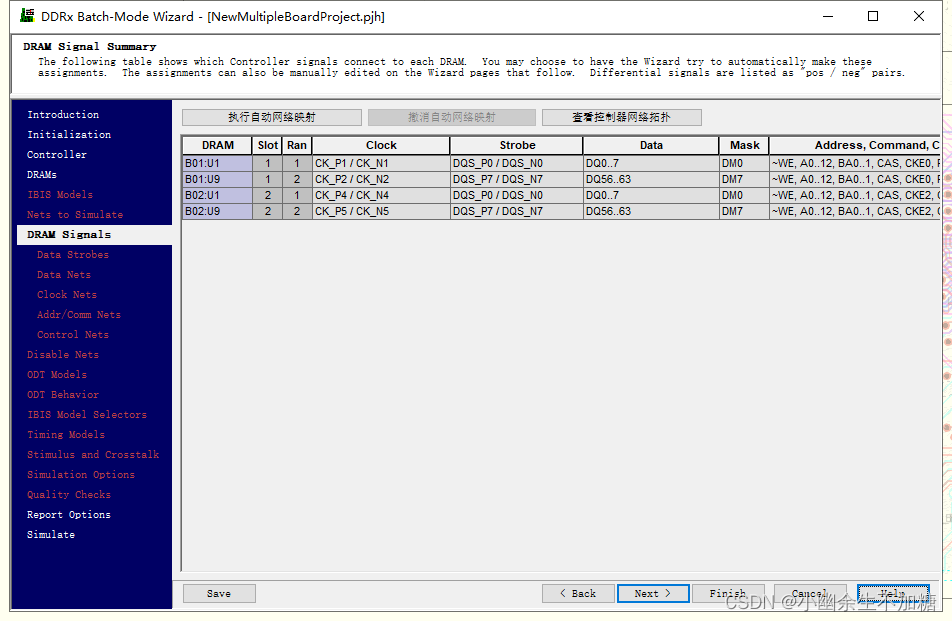

(10)单击“next”按钮,结果如图所示:

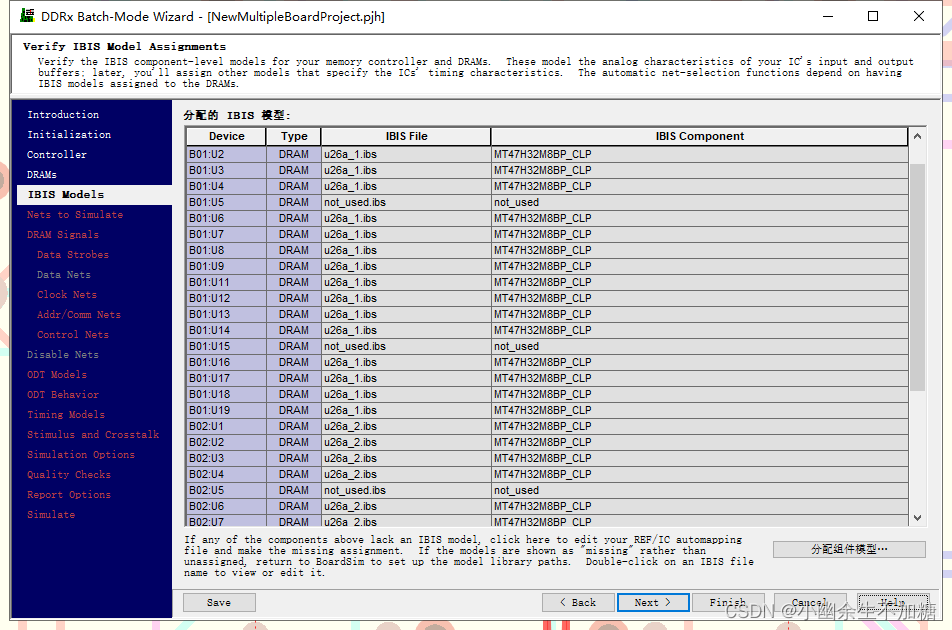

在IBIS 页面,确保所有器件都已经分配IBIS模型。如果IBIS 列的值显示的是红色,则说明模型库路径还没有被定义。

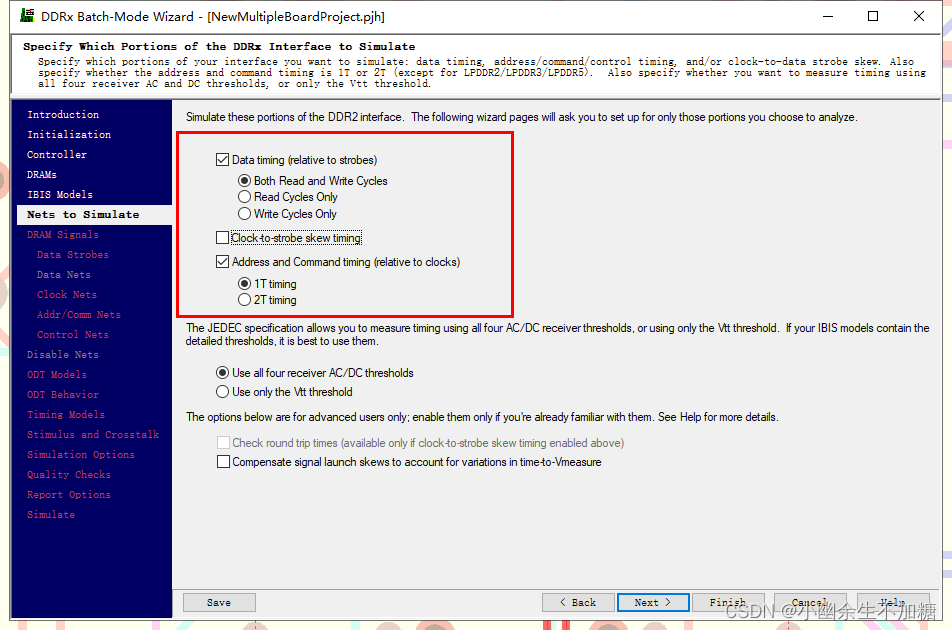

(11)单击“Next”按钮,在“Nets to Simulate”页面,取消选中“Clock-to-strobe skew timing”,如图所示,单击“Next”按钮。

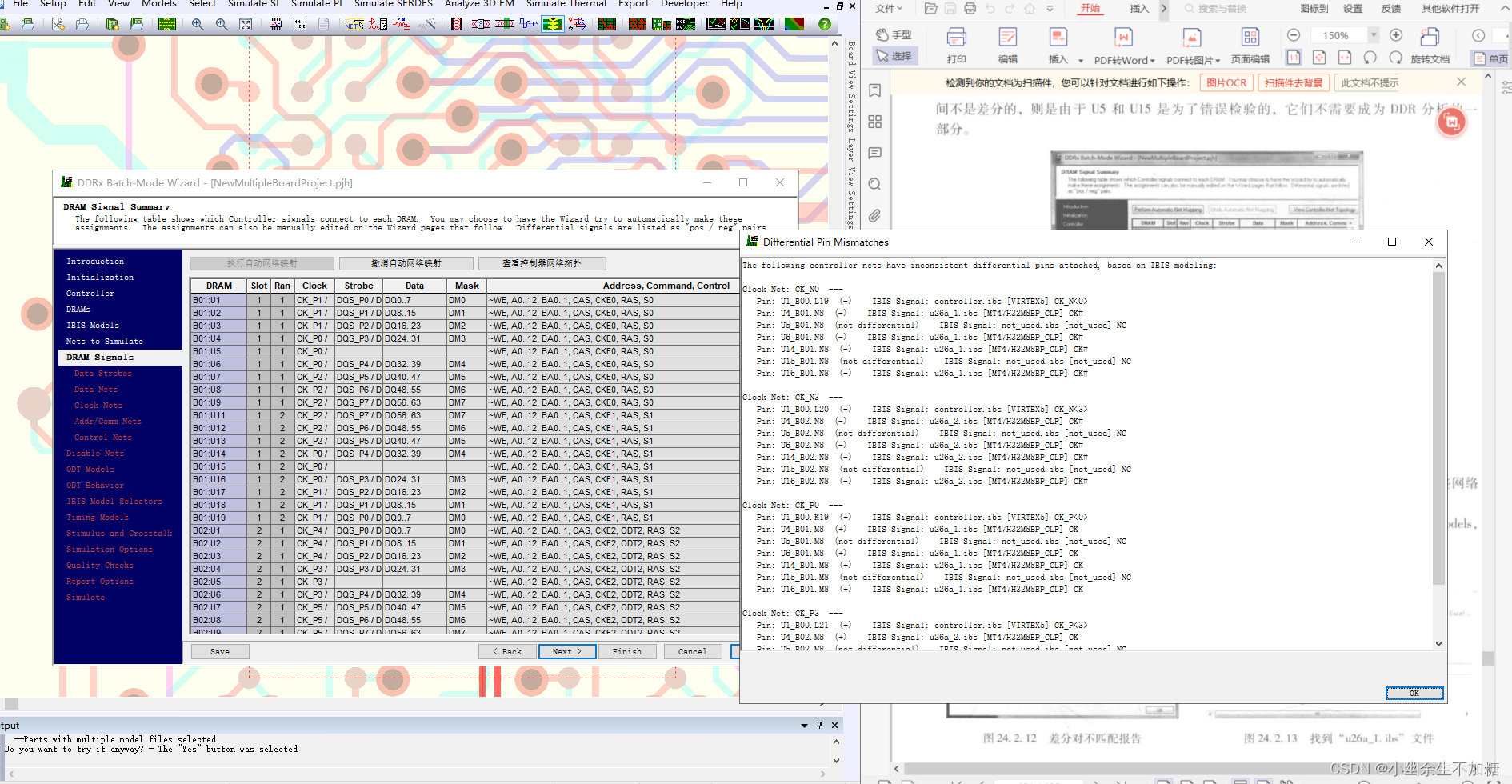

(12)在“DRAM Signals”页面,单击“Perform Automatic Net Mapping”按钮,如图所示:

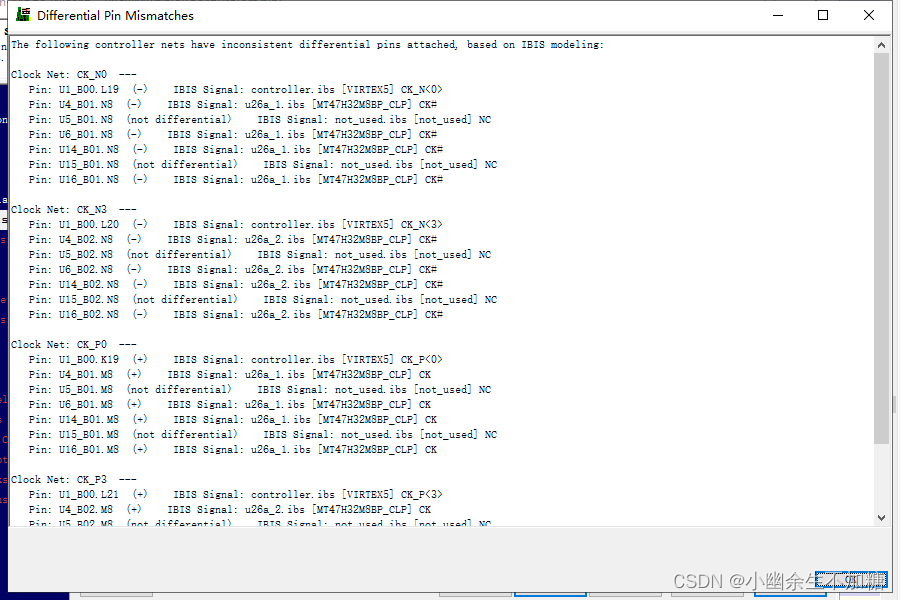

(13)浏览差分对不匹配报告,如图所示:

这个算法能够检查控制器和DRAMS之间的差分引脚的连接性。如果发现U5和U15 之间不是差分的,则是由于U5和U15是为了错误检验的,他们不需要称为DDR分析的一部分。

(14)关闭差分对不匹配报告。

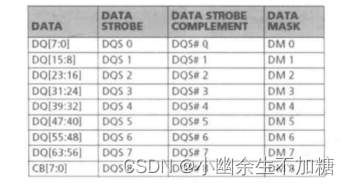

在报告中可以看到Strobe Data和Mask列是空的,下面查找故障,找出为什么这些网络没有映射。

(15)在“我的电脑”中定位到以下路径:C:\Adv HLTrng\Memory Interface\models.如图所示:

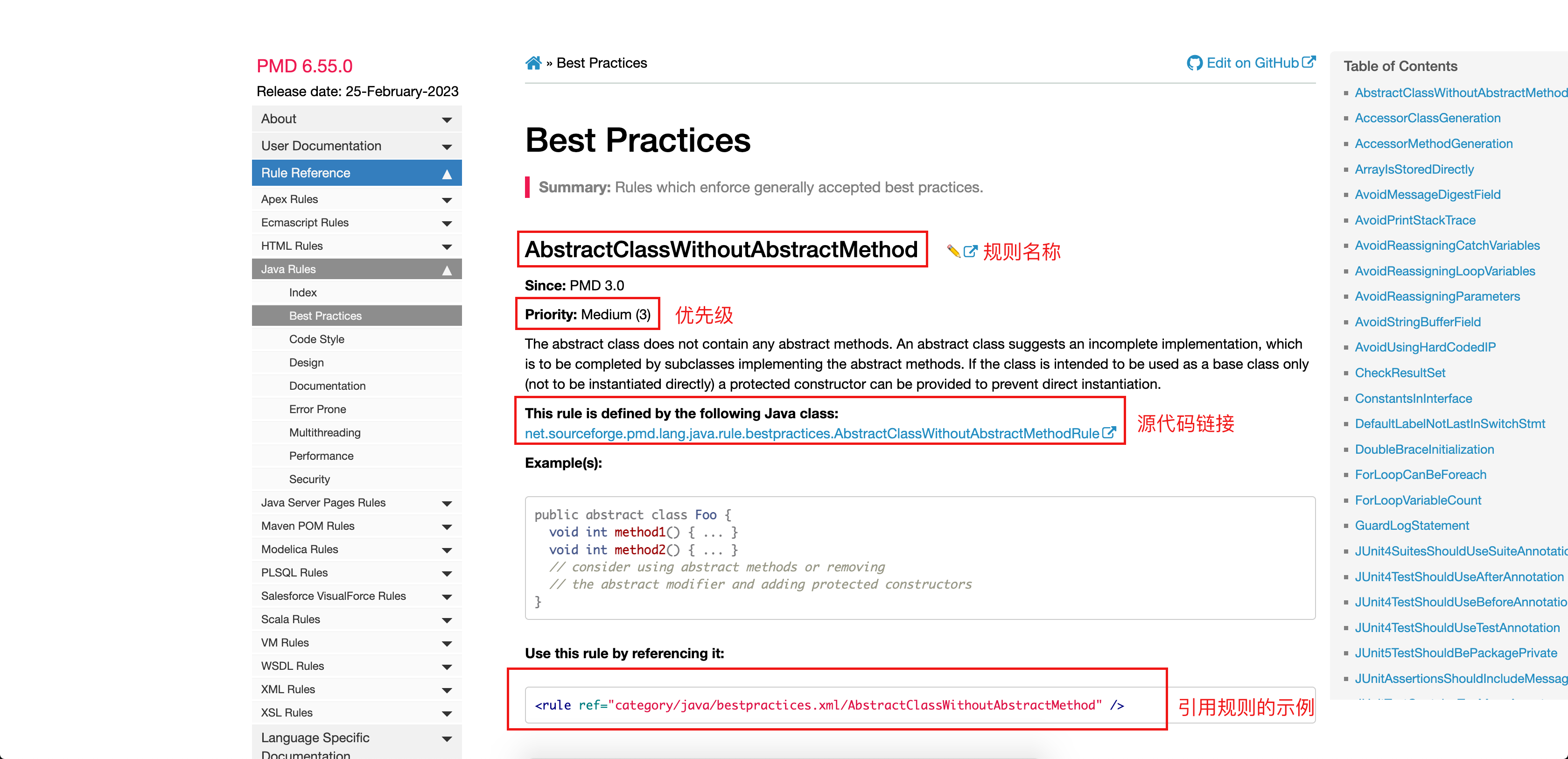

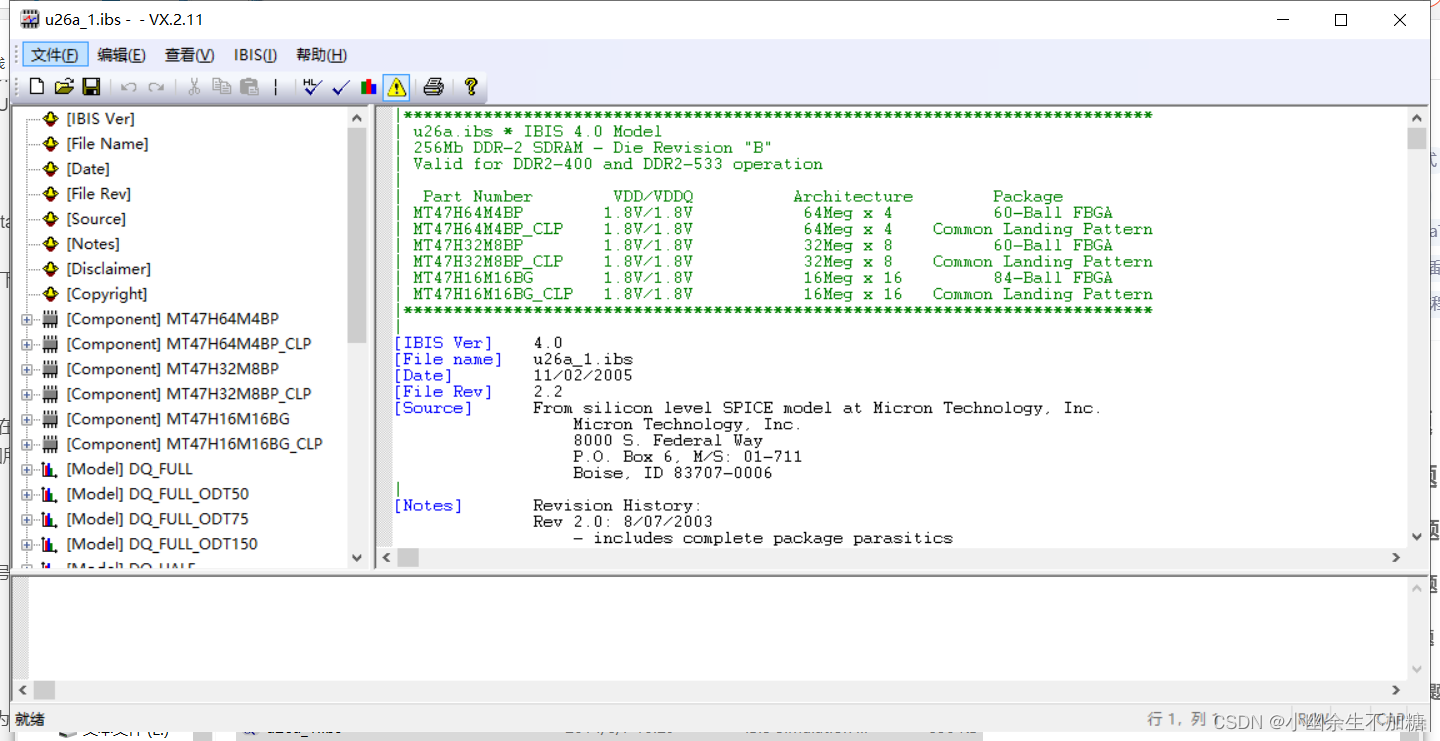

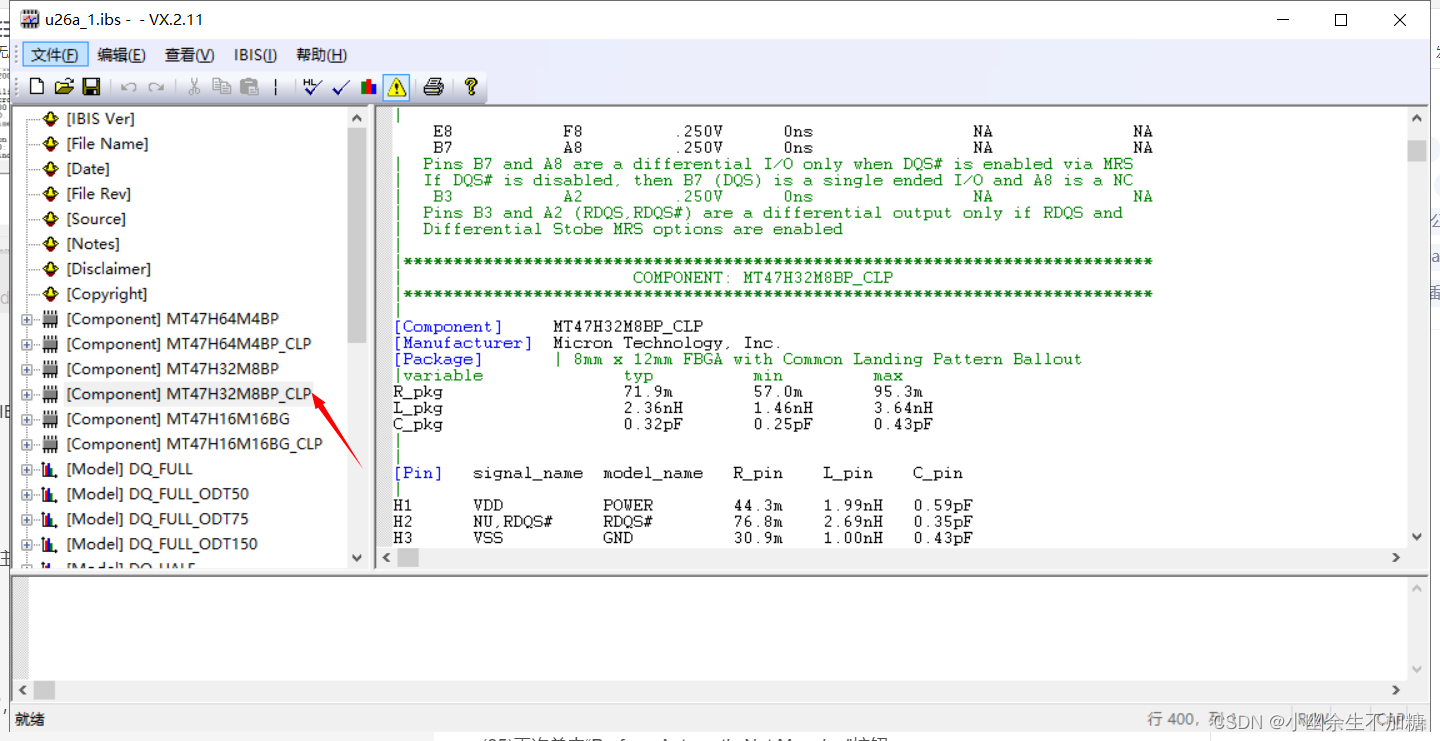

(16)双击“u26a_1.ibs”文件,在Visual IBIS Editor的左窗格中双击“[Component] MT47H32M8BP CLP”,如图所示:

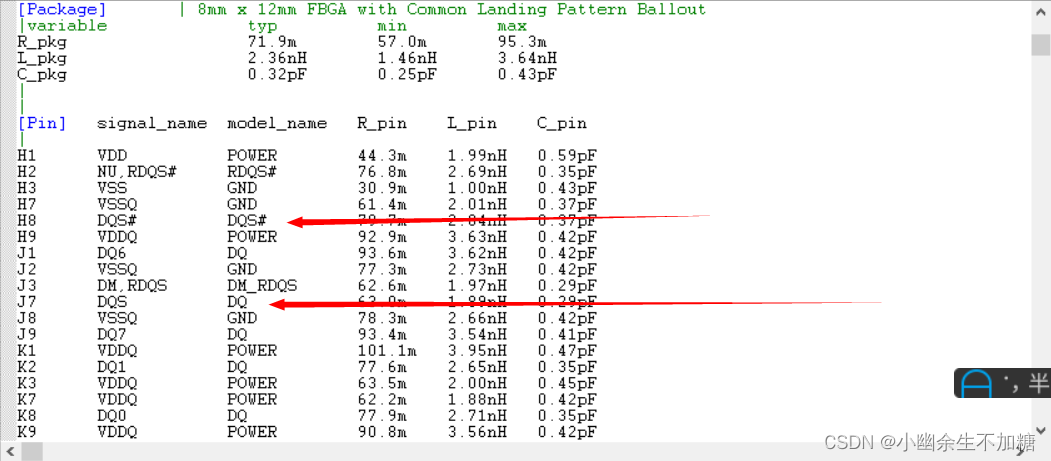

(17)观察引脚为H8和J7的信号名称,注意到它们的名称分别为“STB#”和“STB”.如图所示:

(18)改变引脚H8的信号名称为“DQS#”,引脚J7的信号名称变为“DQS”,如图所示:

(19)保存IBIS文件。

返回多层板工程,为了重新下载IBIS模型,暂时先退出向导。

(20)在HyperLynx中单击“Cancel按钮。

(21)当被问到是否保存时单击“No”按钮。

(22)再次通过“Simulate SI”→“Run DDRx Batch Simulation”调用向导。

(23)如图所示,单击“OK”按钮接受差分引脚的不匹配。

(24)在DDRx向导的左窗格中,单击“DRAM Signals”按钮。

(25)再次单击“Perform Automatic Net Mapping”按钮。

(26)单击“Yes”按钮继续。

(27)关闭差分对不匹配报告,打开如图所示对话框。

从图中看到,除了DIMMS的U5和U15以外,“Strobe”、“Data”和“Mask”列已经填满数据。正如所看到的,向导已经自动省略了没有连接的信号。在这种情况下,U5和U15不是我们分析的部分,因为本次仿真只是想要仿真数据信号的第一个字节通道,只需要仿真 DRAMs,就是说不需要DDRx接口的所有DRAMs,也能运行成功。这个设置的优势就是简化了最初的设置,再运行整个接口进行仿真。

(28)在左边窗格中单击“DRAMs”。

(29)在Slot1Rank1区域选择U1…9

(30)单击“ClearSelection”按钮。

(31)对于其他剩余的Rank Slot区域重复以上两步,如图所示:

(32)从“Board”的下拉列表中选择“B01–DIMM1”,选择U1,设置Slot1和 Rank1,单击→按钮,如图所示:

(33)选择U19,设置Slotl和Rank2,单击→按钮,如图所示:

当然,Rank1和Rank2是由哪个DRAMs组成的也很重要,找到它最好的方式就是通过在层板工程中选择网络,打开分配模型对话框。

(34)从“Board”的下拉列表中选择“B02–DIMM2”,选择U1,设置Slot2 和 Rank1,单击按钮,如图所示:

(35)选择U19,设置Slot2和Rank2单击按钮,如图所示。

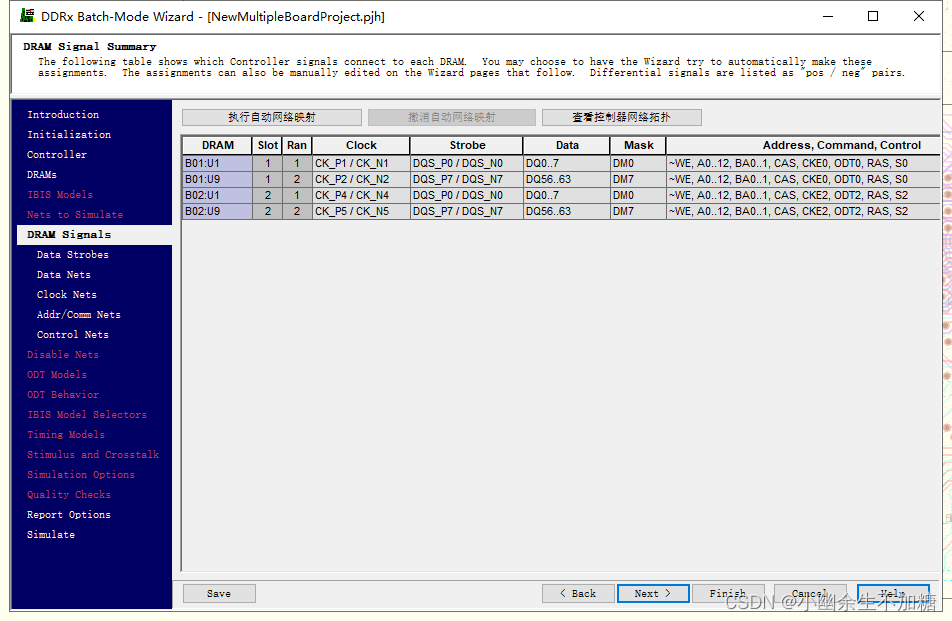

(36)在左边窗格中选择“DRAM Signals” 如图所示:

【注意】行数减少了,因为设置中定位到以DRAMs为中心。同时注意到“Address. Command.Control”列的信号,对于B01DRAMsODT信号丢失了。原因是ODT信号在 u26a1ibs模型中被命名为TERM。接下来,将在向导中手动分配这些ODT信号。

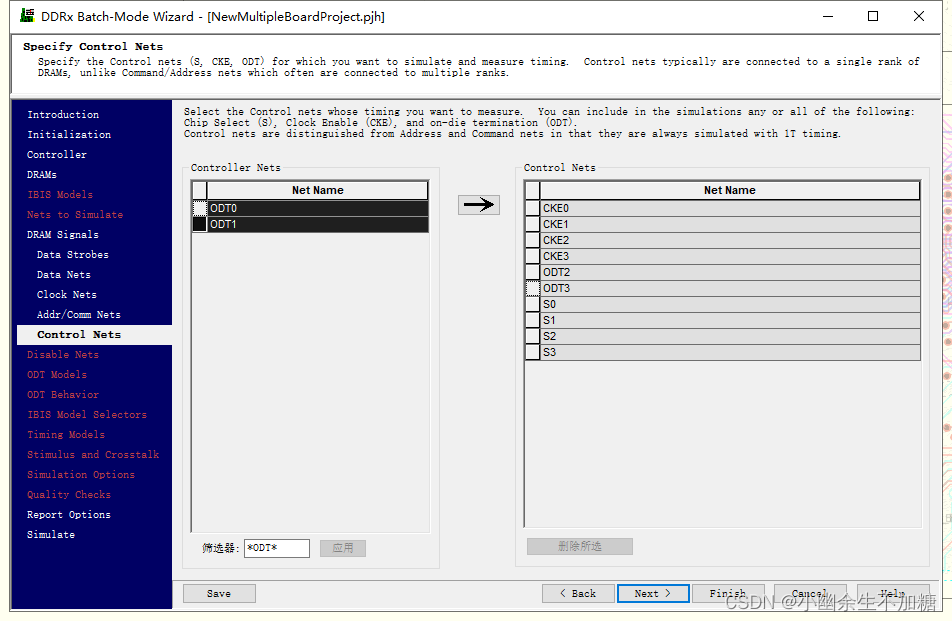

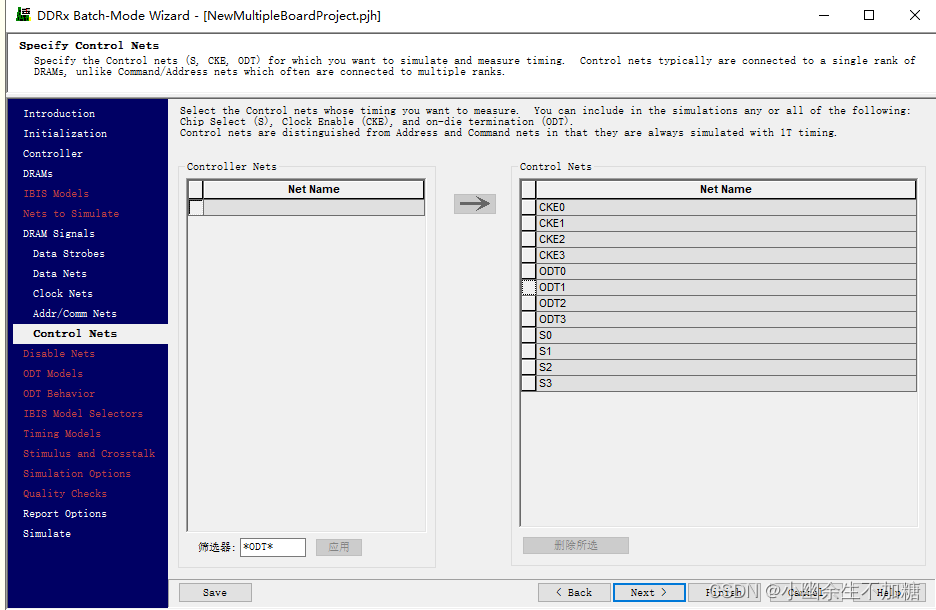

(37)单击“Next”按钮直到到达“Control Nets”页面,在页面选择中,单击Ctrl键的同时选中“ODTO”和“ODT1”,如图所示:

(38)单击→按钮,如图所示:

(39)再次进行检查,在左边的窗格中单击“DRAM Sigals”,可以看到ODT信号映射给了B01,如图所示:

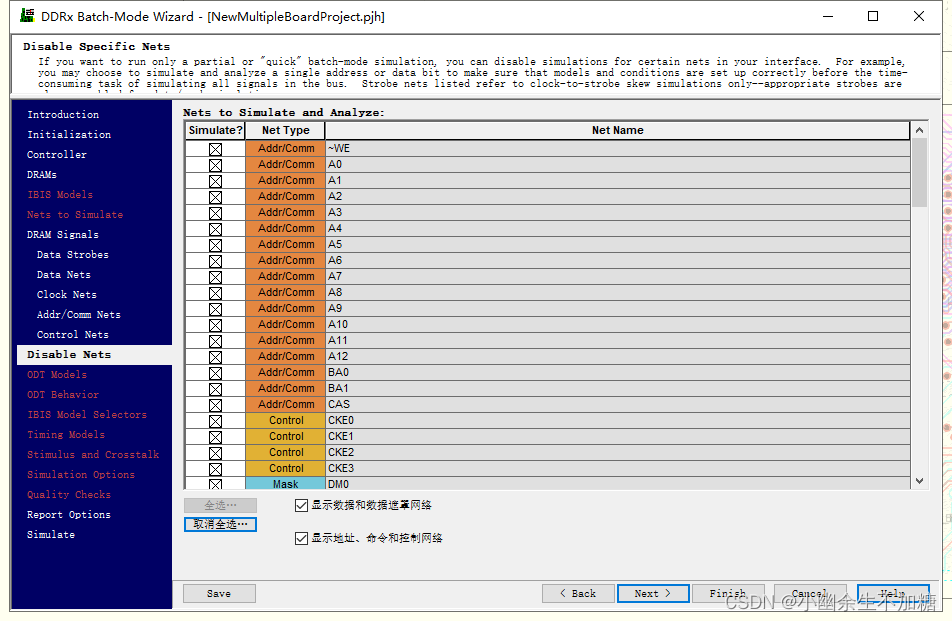

(40)单击左边窗格中“Disable Nets”,如图所示:

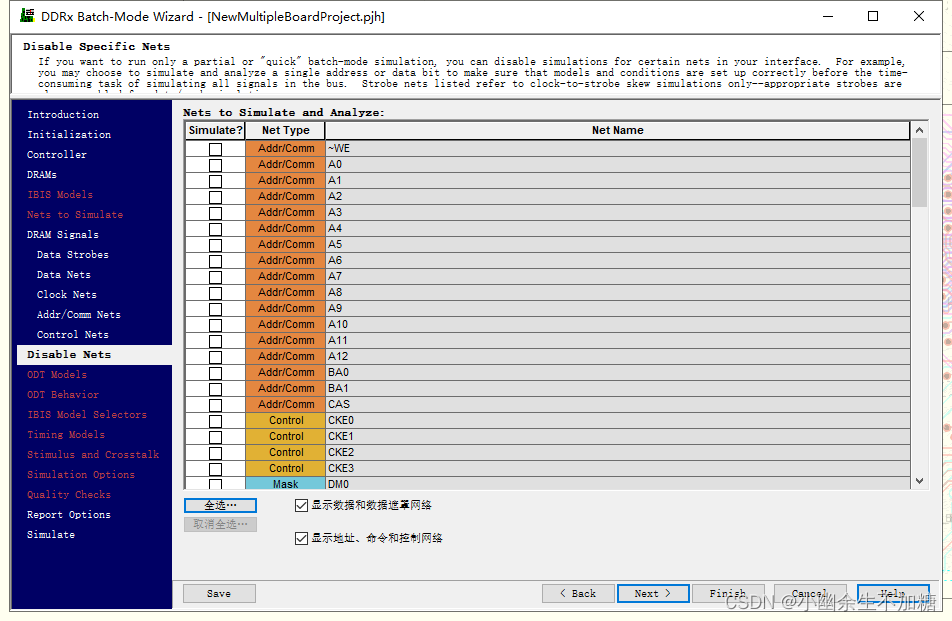

(41)单击“Unselect All”按钮。

【注意】“Unselect All”是一个好的选项,能够在仿真中避免选择不想要的网络。

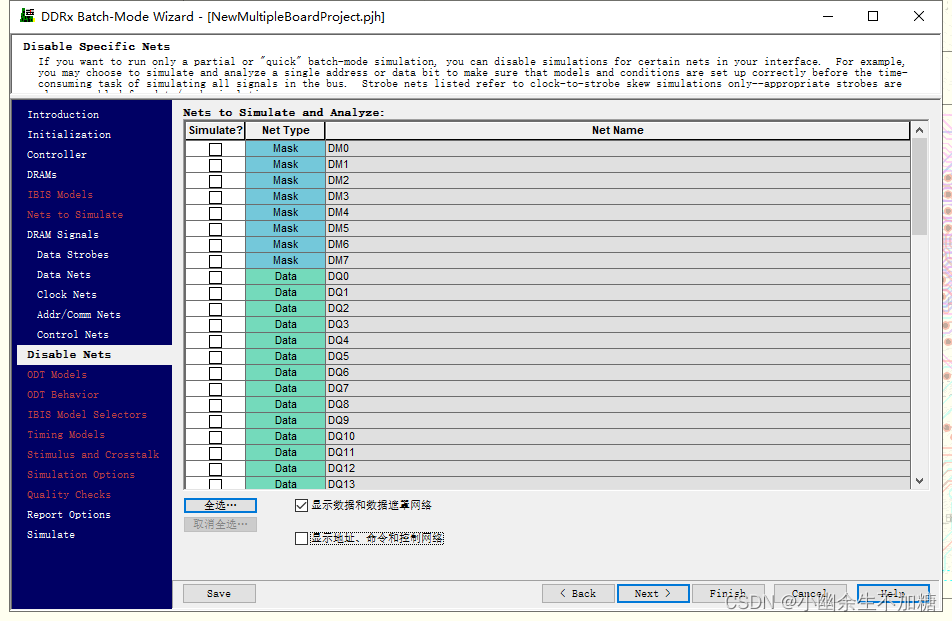

(42)取消选中“Show Address,Command,andControlNets”选项,应当看到如图所示的网络。

正如所看到的,相应的DQS不在列表中。记得之前已经定义过关联信号,一旦选择了

任何一个关联的数据网络,这个DQS信号就会自动仿真。

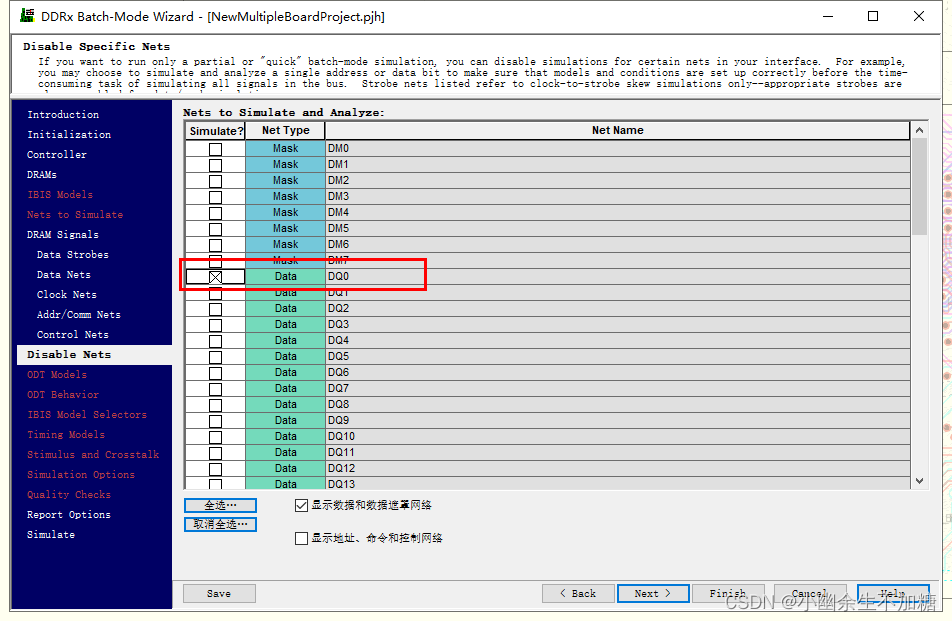

(43)单击“DQ0”信号前的选择框,如图所示,单击“Next”按钮。

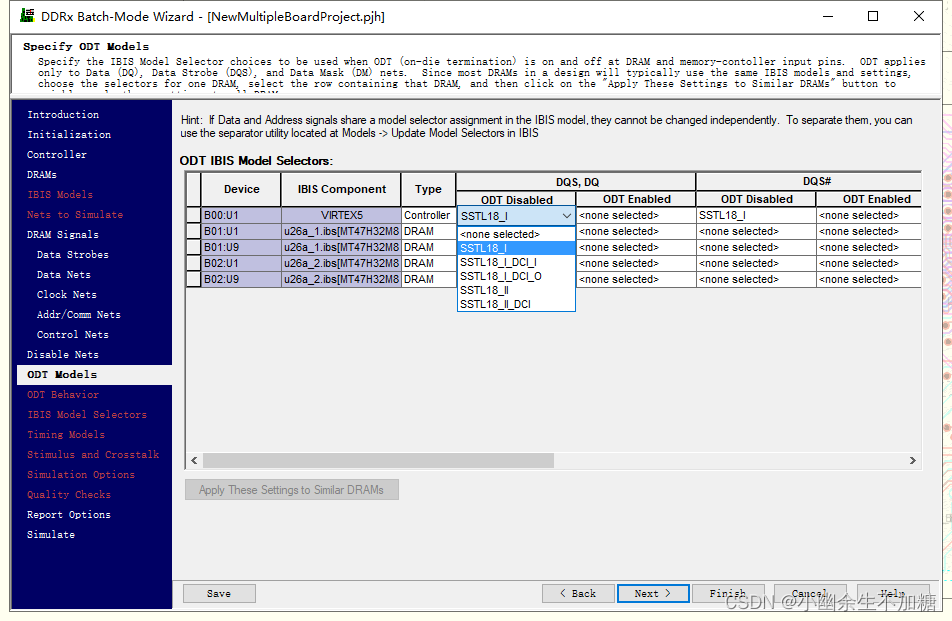

(44)单击Controller行的“DQS, DQ”信号的“ODT Disabled”列,将看到一个控制器可用模型的下拉列表,列出了[Model Selector]中的控制器的 IBIS模型,如图所示。

【注意】如果在IBIS模型中没有[Model Selector],那么这个区域是灰色的,只有唯一的一个信号名称。

(45)在列表中选择“SSTL18_I” 如图所示。

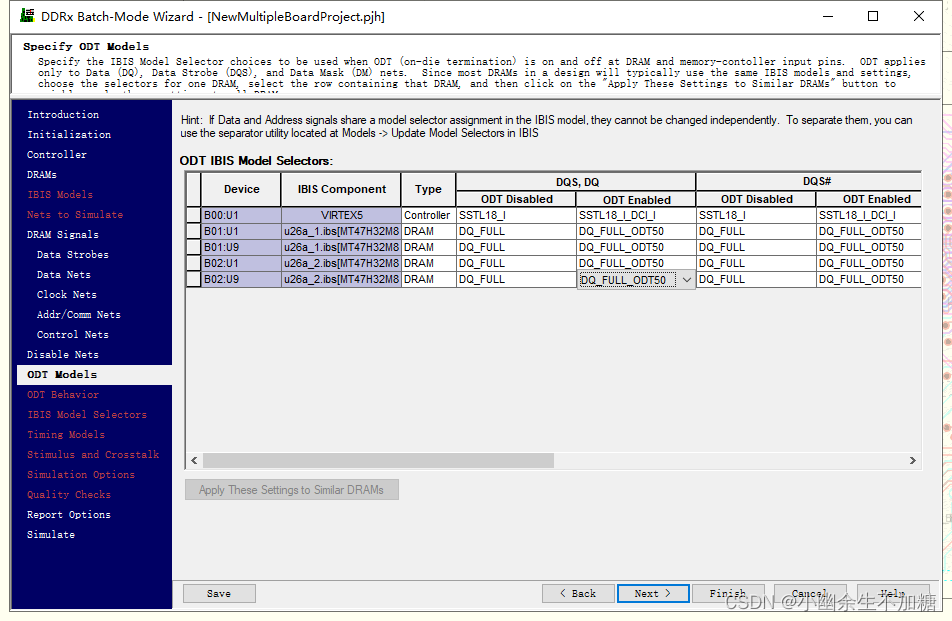

(46)为“ODT Enabled”列选择“SSTL18_I_DCI_I”模型,如图所示。

【注意】Controller的其他信号已经自动分配。这是因为在Controller的IBIS模型相同的模型选择器中,已经为这些信号分配了模型。

(47)设置BO1:U1DRAM的ODT值为默认值,如图所示。

【注意】只有B01:U19行分配了相同的设置,B02的DRAMs行没有,原因是它们是在一个独立的IBIS模型(u26a_2ibs)中分配的。

(49)使用相同的方法为B02 DRAMs分配ODT,如图所示。

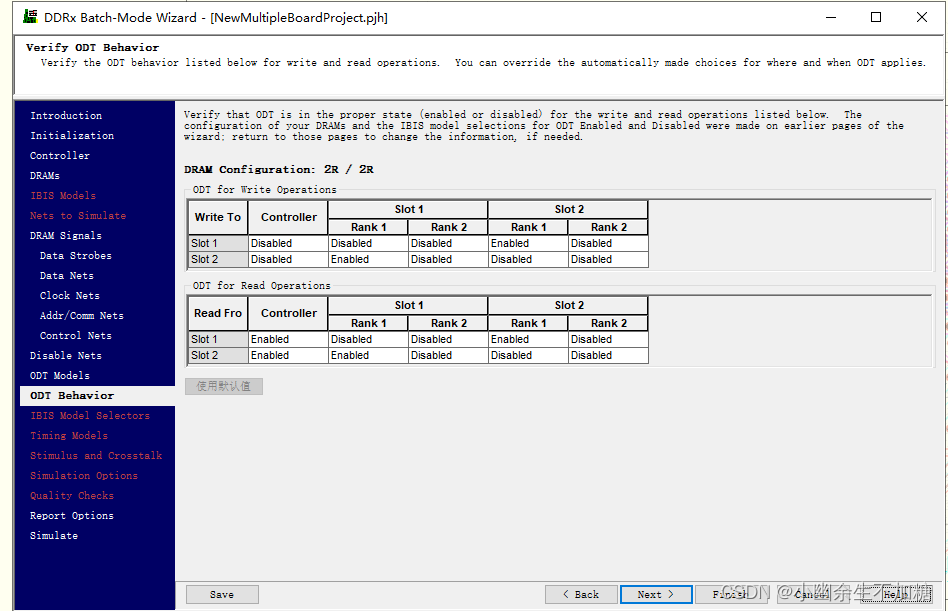

(50)单击“Next”按钮,打开“ODT Behavior”页面,如图所示:

在“ODT Behavior”页面,可以选择在不同的DRAM器件或者控制器的读/写操作中激活或取消ODT。默认设置是由Micron公司推荐的,依赖于DRAM配置。在这种情况下,

DRAM配置是“2R/2R”意味着系统中有两个RANK模型.

(51)保持默认设置,如图所示,单击“Next”按钮。

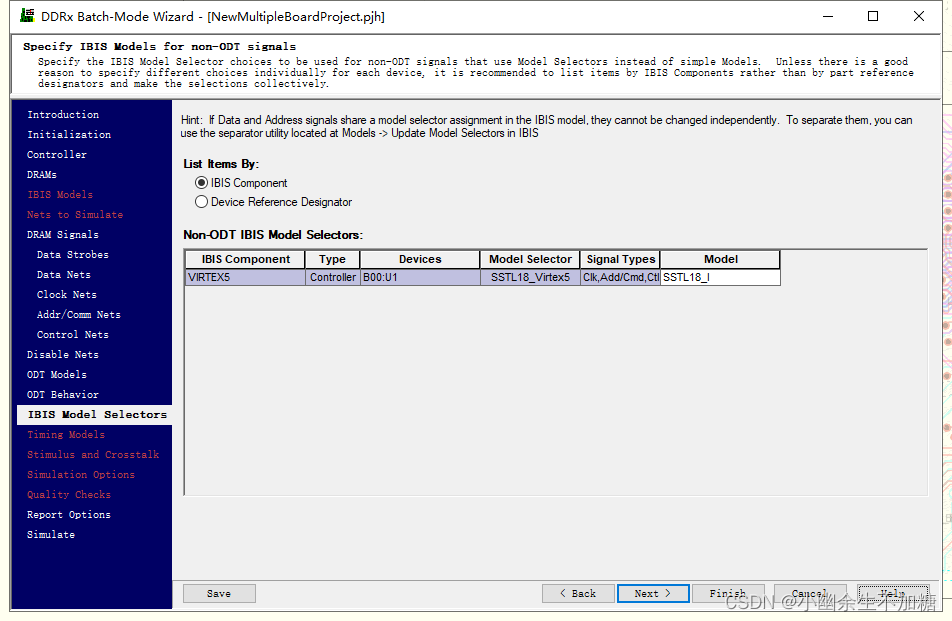

这个“IBIS Model Selectors”页面可以为没有ODT信号的模型设置模型选择器,如时钟、地址和控制信号。如果想要使用不同的模型如不同驱动力的模型来进行仿真,则这个页面是很重要的。

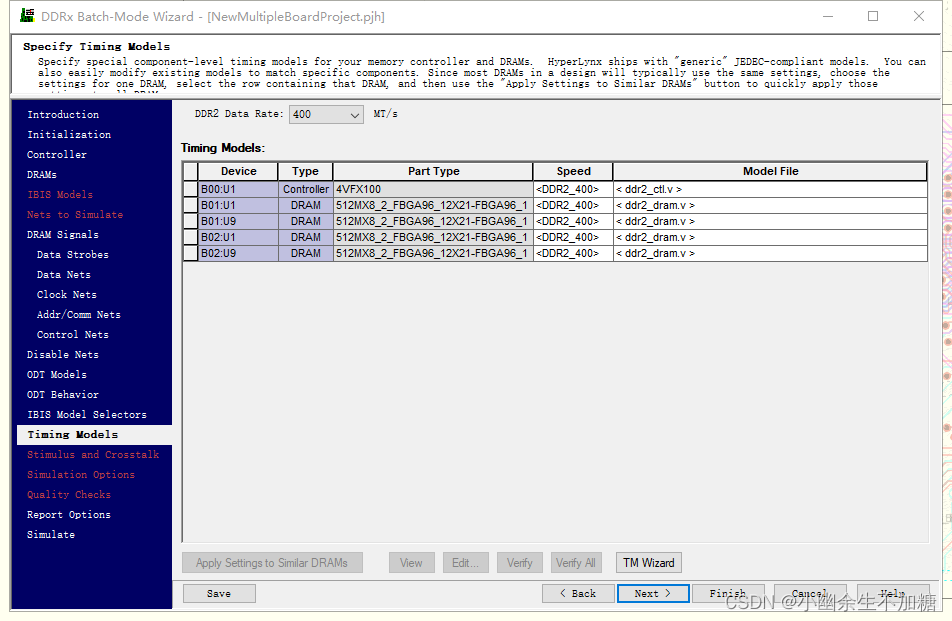

(52)保持“IBIS Component”选项被选中,Model为SSTL18_l,单击“Next”按钮,进入如图所示页面。

“Timing Models”页面可以为控制器和DRAMs定义时域模型。默认模型是HyperLynx配置的一部分。接下来,将使用该页面来观察一些预期的行为。

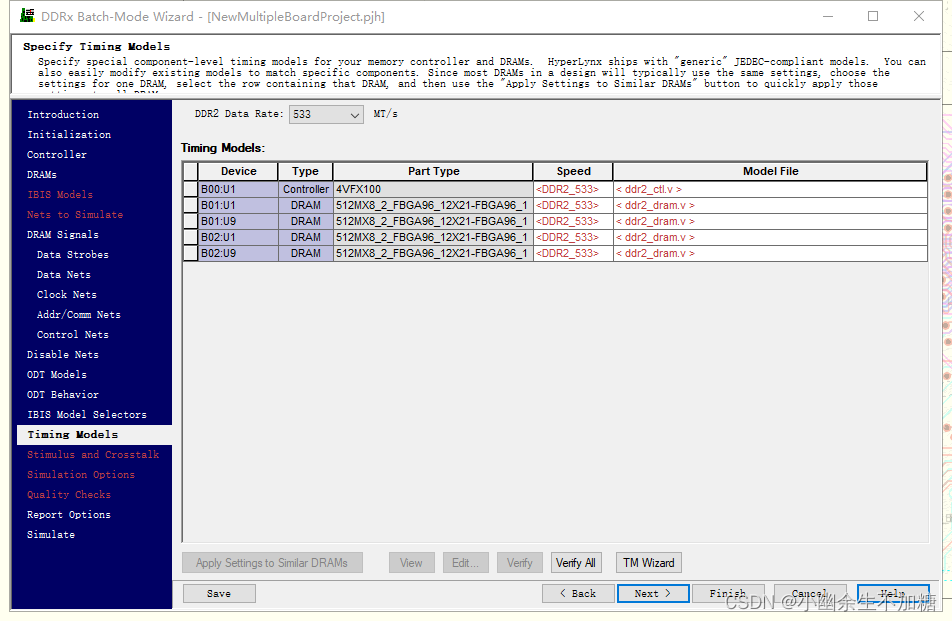

(53)从“DDR2 Data Rate”下拉列表中选择“533”。

如图中所看到的,这个值在“Speed”和“Model File”列中变为红色显示。

(54)单击“Verify All”按钮,设置“DDR2 Data Rate”返回到400MT/s

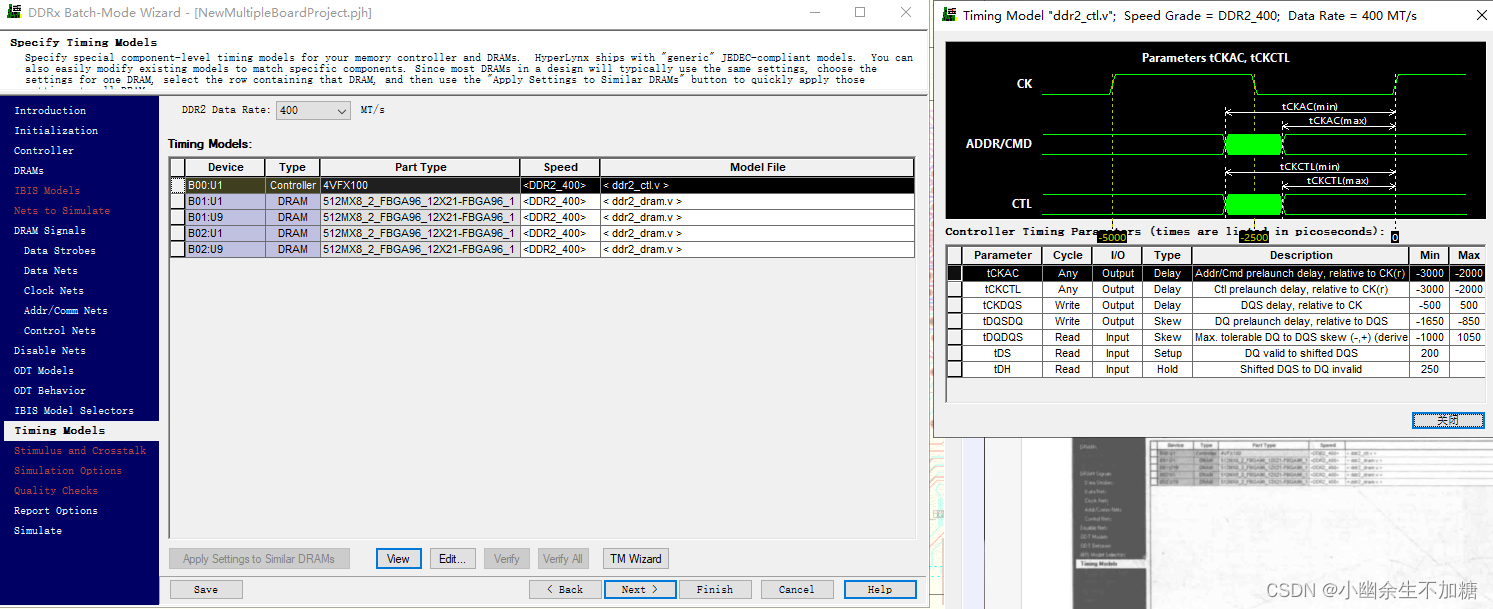

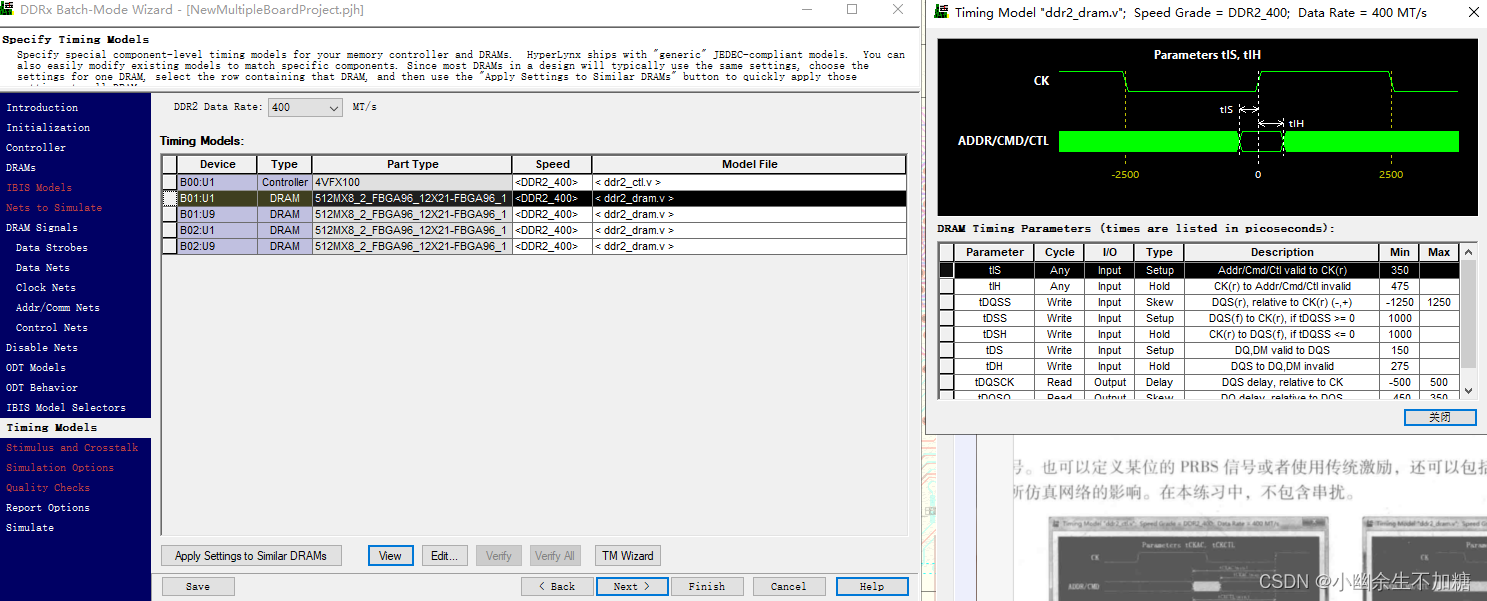

(55)为了查看Controller的时域参数,双击第一行或者选中第一行单击“View”按钮,得到如图所示页面。

在这里可以在一个控制器模型的时域图表中查看每一个参数。单击不同的行可以查看其他的参数,如图所示。

(56)在查看参数后关闭时域模型对话框,单击“Next”按钮,得到如图所示页面。

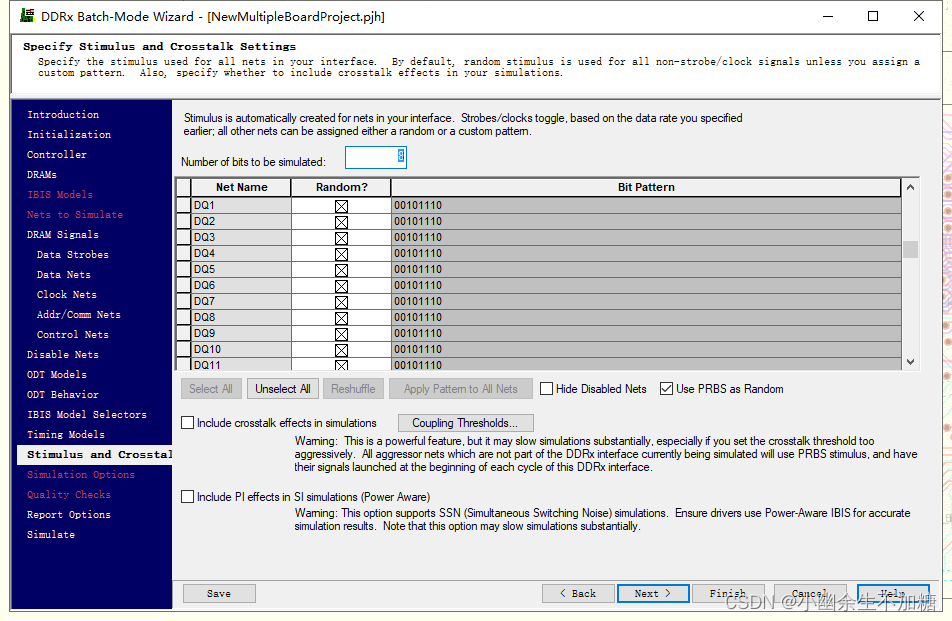

在“Stimulus and Crosstalk”页面,可以定义激励,用于仿真non-clock和non-strobe信号。也可以定义某位的PRBS信号或者使用传统激励,还可以包括串扰影响,即邻近网络对所仿真网络的影响。在本练习中,不包含串扰。

(57)改变“Bit order”为8(最下为8个),如图所示:单击“Next”按钮。

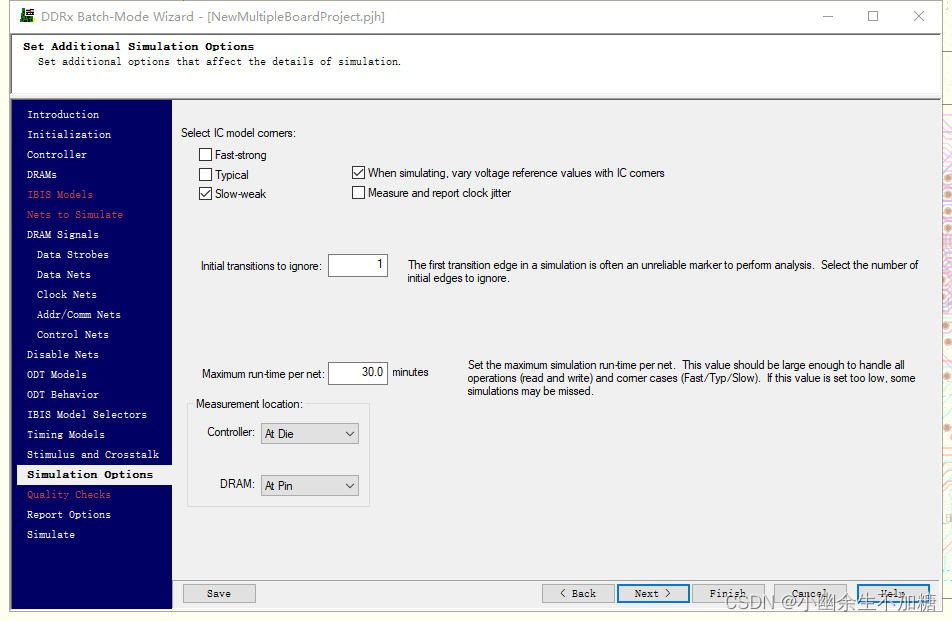

(58)在“Simulation Options”页面,只选择某些选项,其他设置保持默认,如图所示。

“Initial transitionsto ignore”选项指在时域电子表格中不想要报告的边缘数量。通常第一个边缘过渡是一个不理想的标记,可以选择设置为1来忽略它。

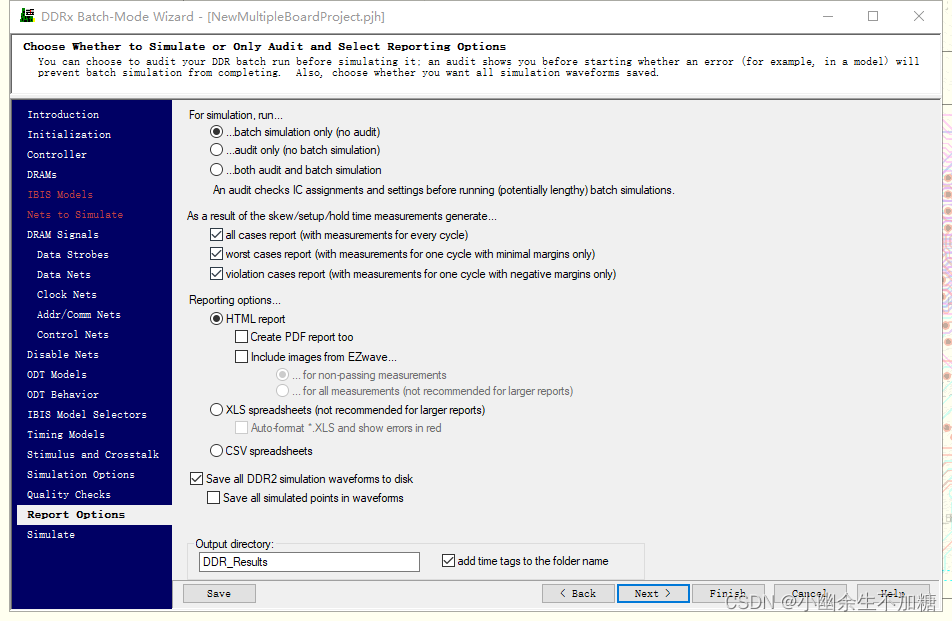

(59)单击“Next”按钮,进入“ReportOption”页面,如图所示。

(60)选择“.….both audit and batch simulation”选项,其他选项保持默认,单击“Next”按钮,得到如图所示页面。

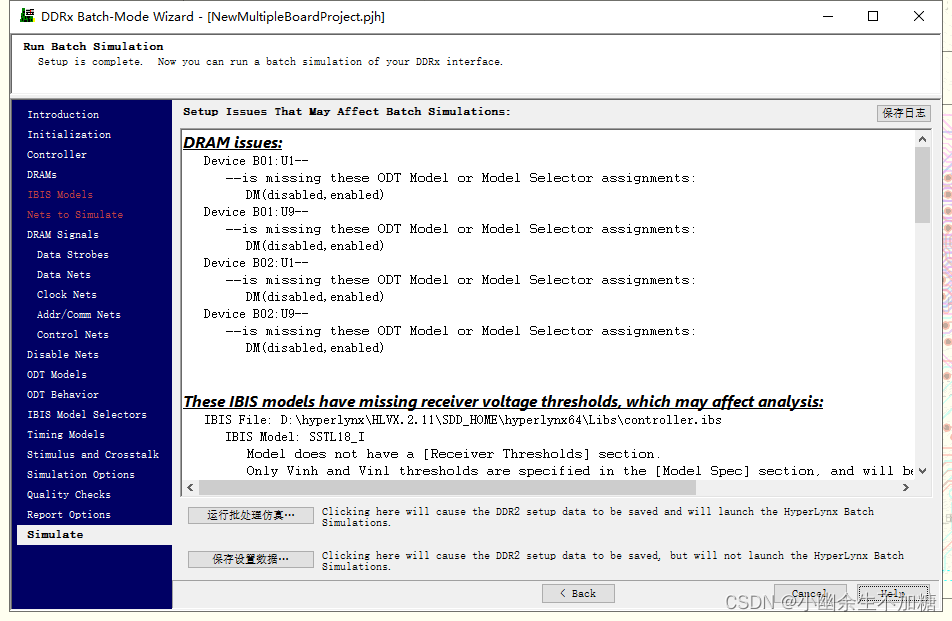

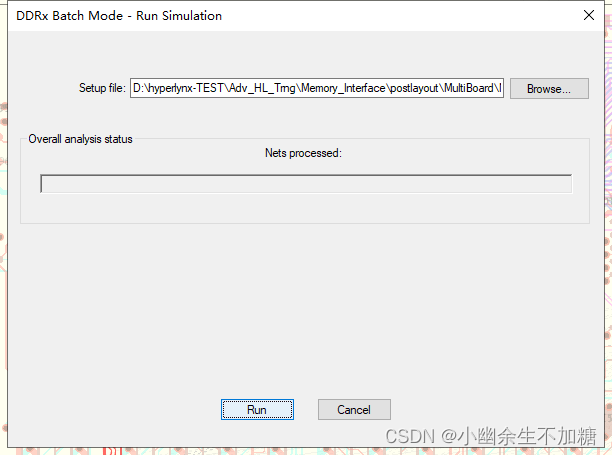

(61)单击“Run Batch Simulation”按钮。

【注意】将得到保存所有的DDRx向导设置的提示, 在一个默认名字的多板工程的 ddr文件中。

(62)单击“Save”按钮,进入如图所示页面。

(63)单击“Run”按钮。

(64)当得到“Simulation has completed…”信息息时,单击“确定”按钮,如图所示

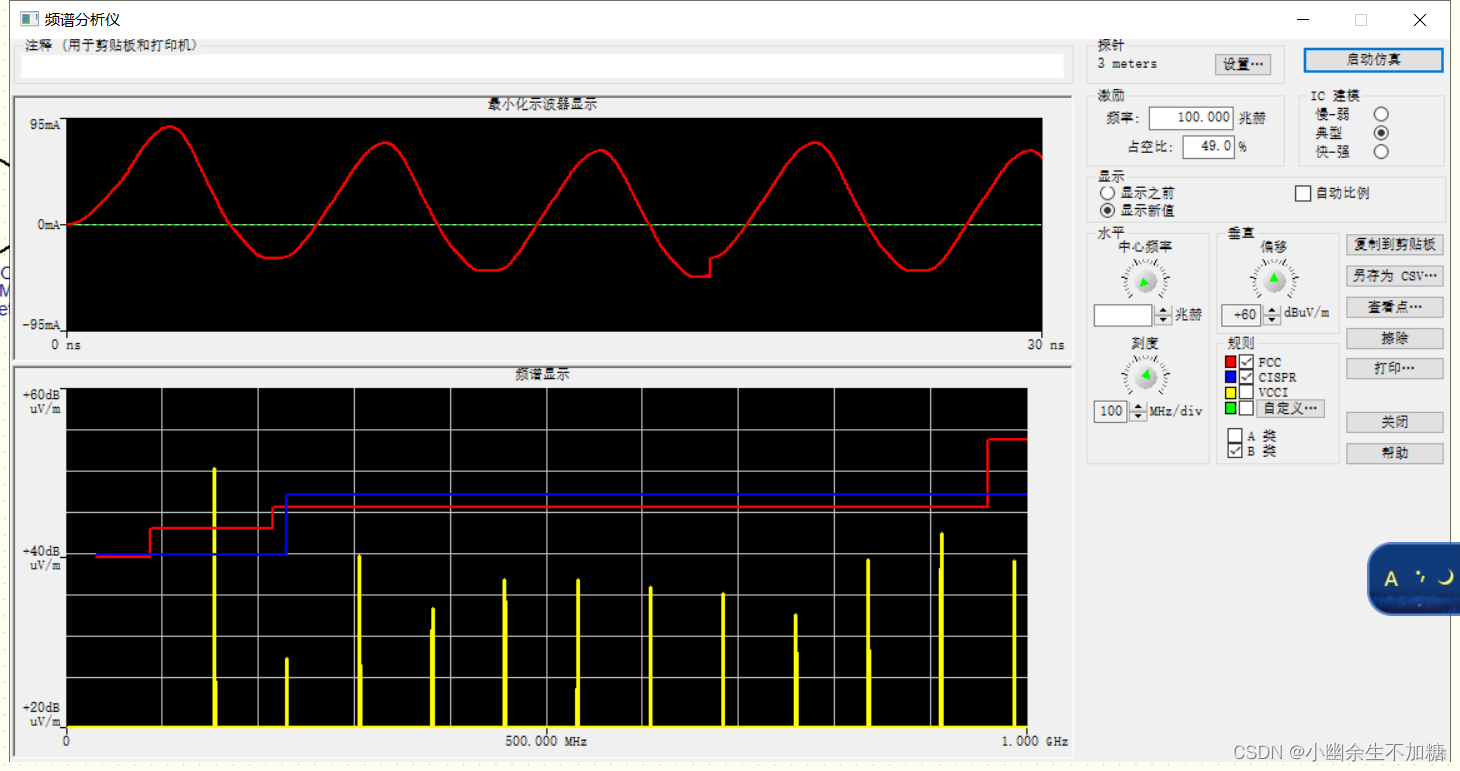

5.仿真结果分析解读

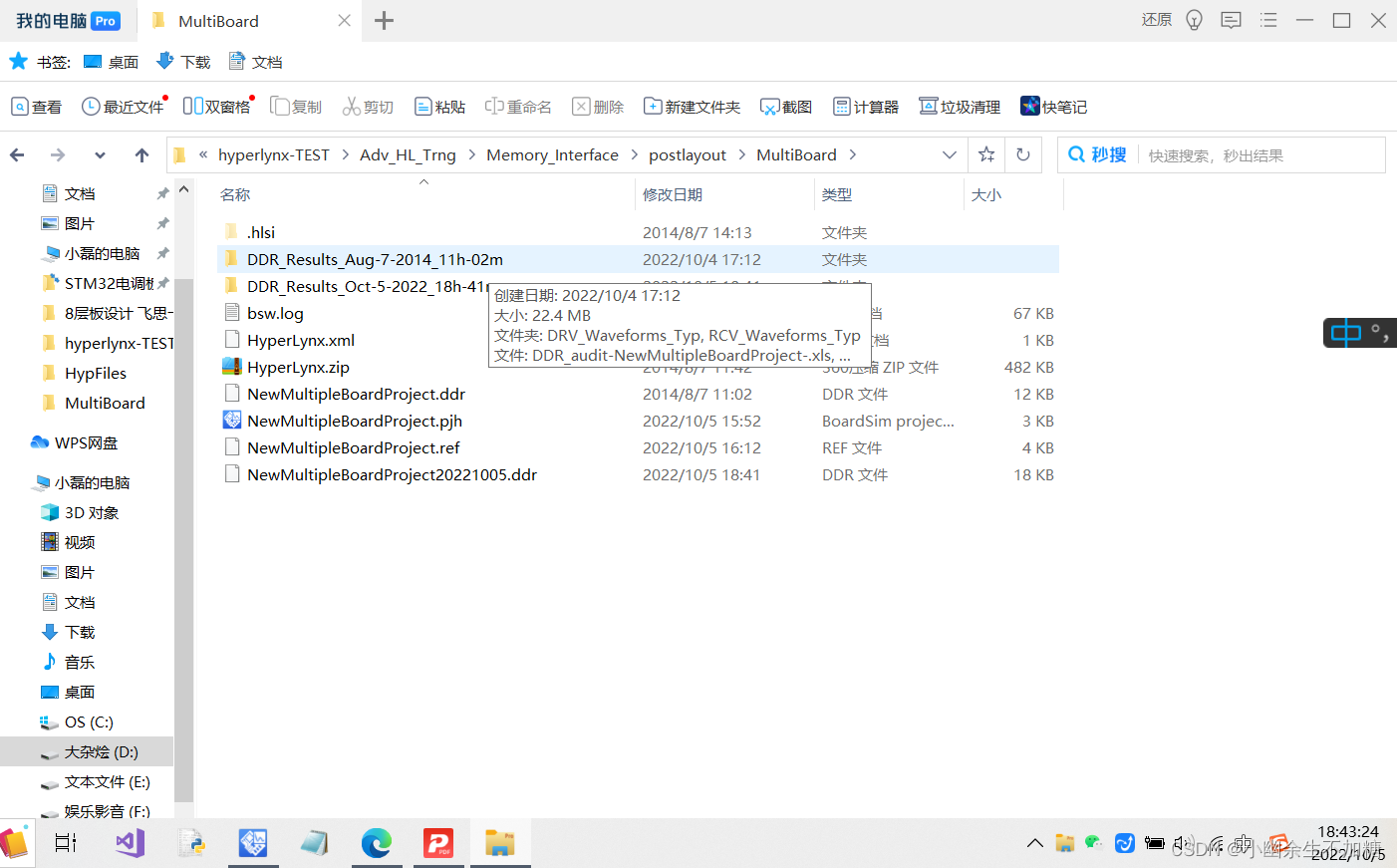

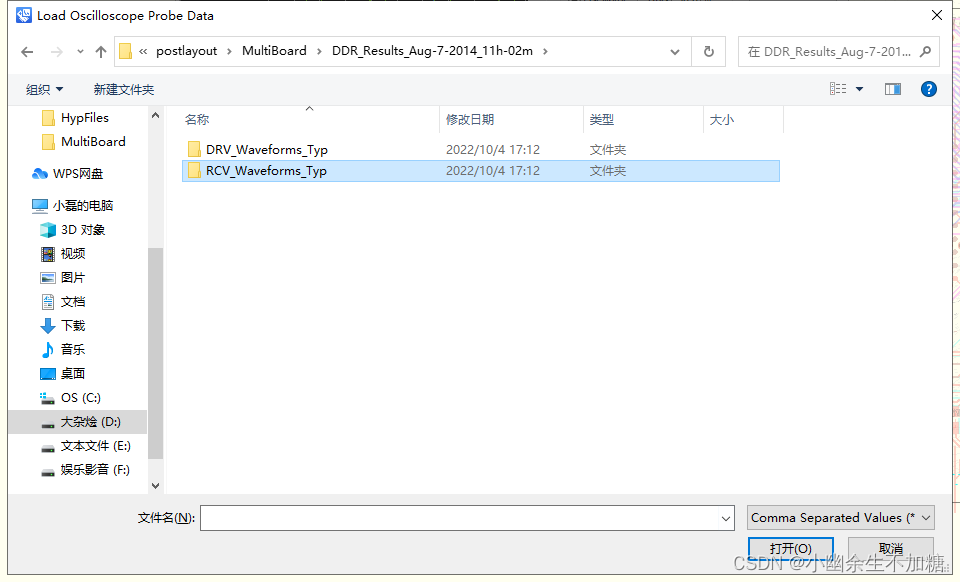

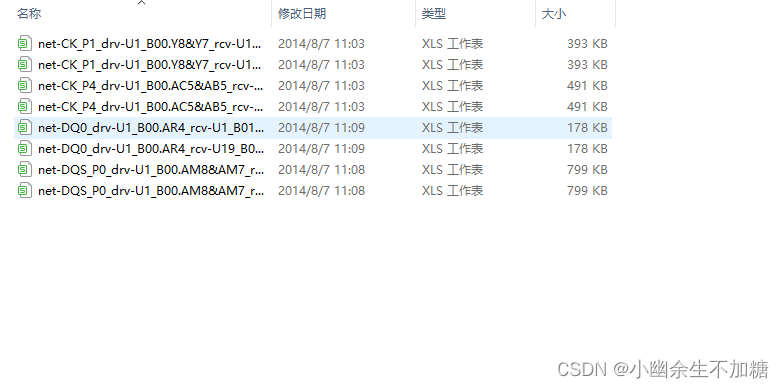

(1)从资源管理器中打开以下路径:C:\Adv_HL_Trng\Memory_Interface\postlayout\ MultiBoard,如图所示。

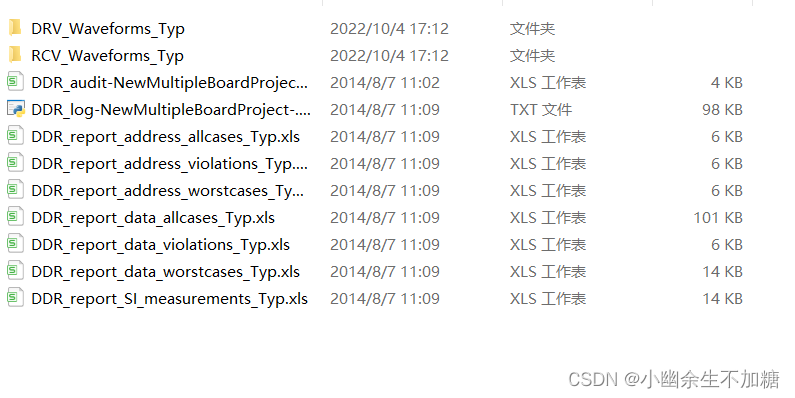

(2)双击DDRResults文件夹,如图所示。

在文件夹中,注意到有一些文件和两个子文件夹。.xls文件是结果的电子表格,两个子文件夹包含.csv文件,是仿真波形文件。请查阅帮助文档来查阅文件命名约定。首先查看读/写操作的时间裕量。

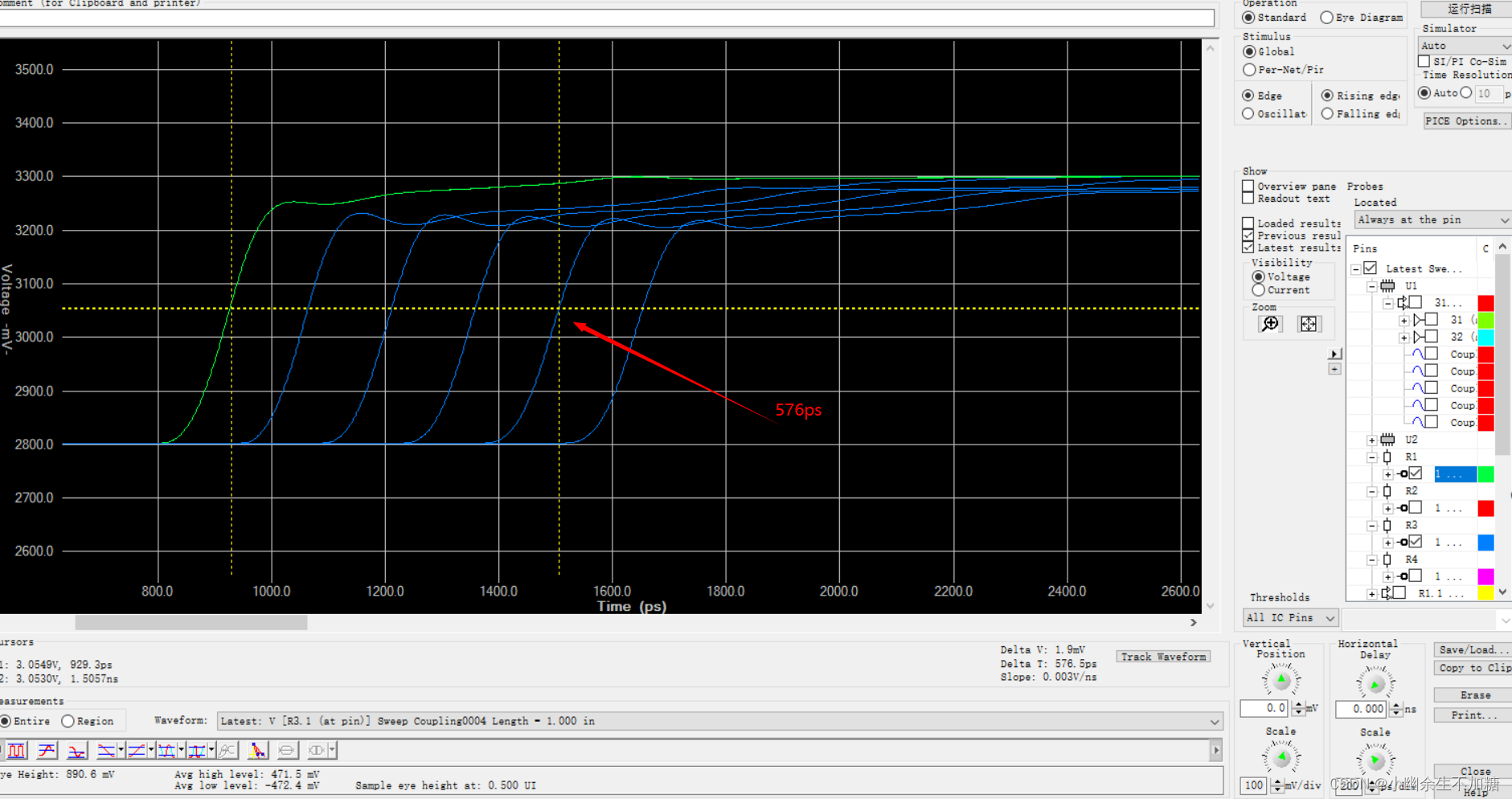

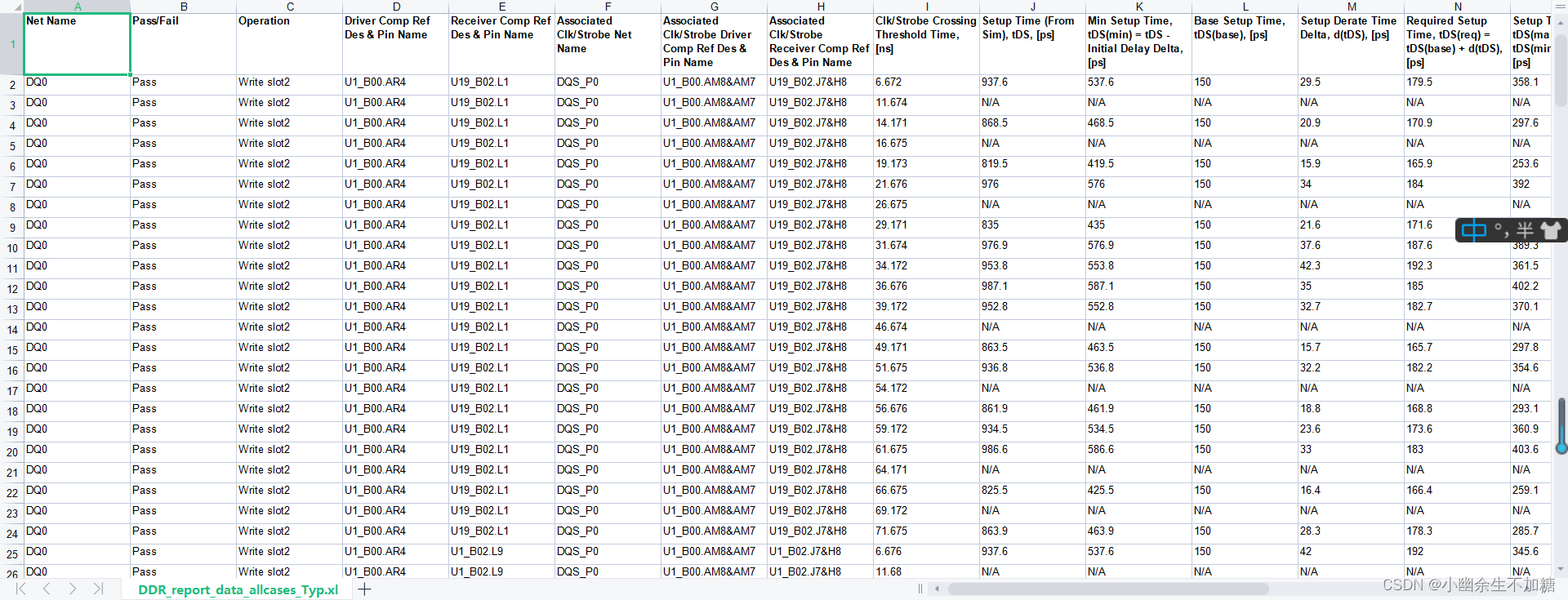

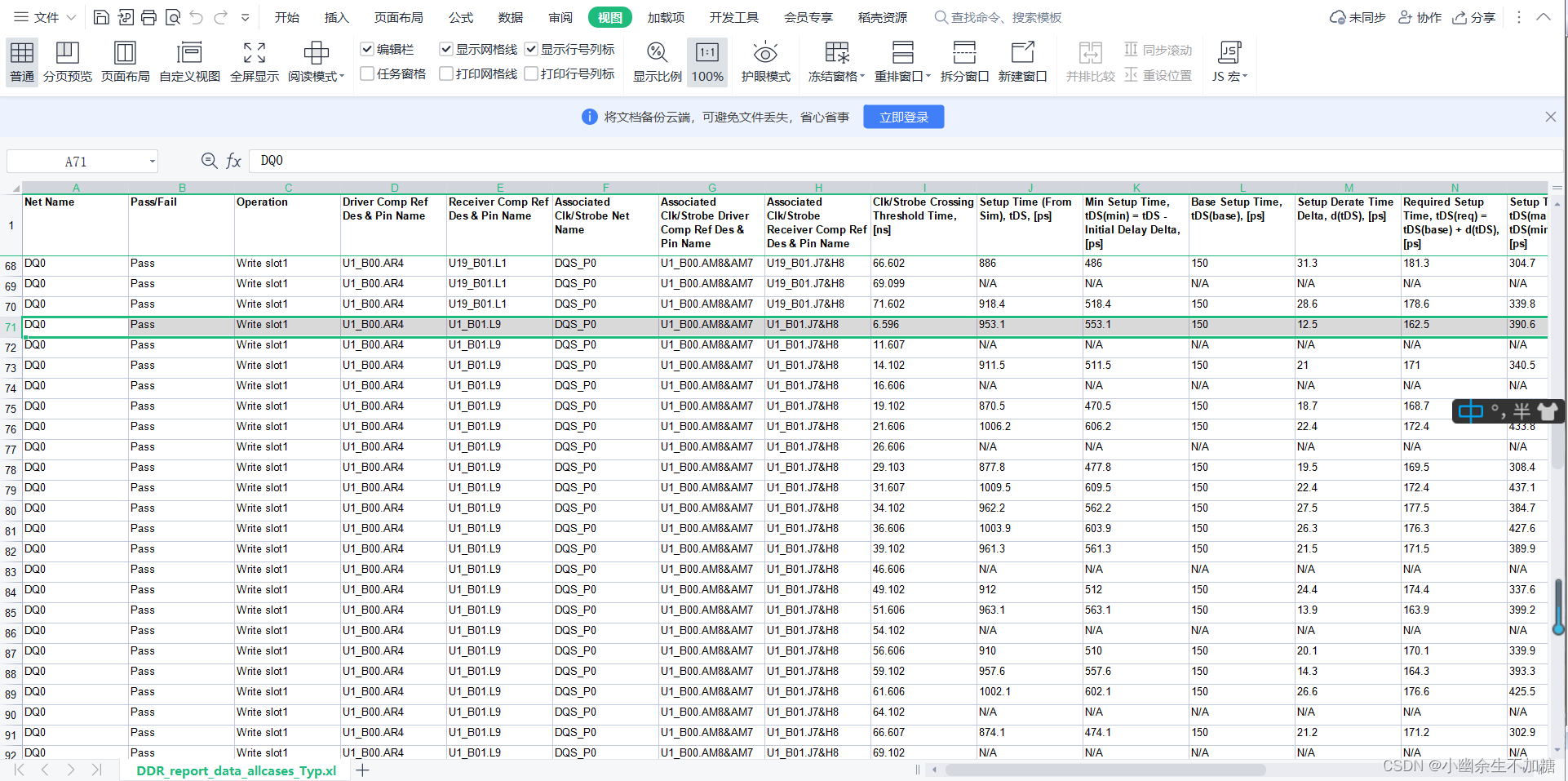

(3)打开DDR_report_data_allcases_Typ.xls文件,如图所示。一旦在“Nets to Simulate”页面选中了“Both Read and WriteCycles”选项,报告就会显示读/写操作的每一个选通边缘的设置和保持裕量。接下来,将验证报告中对应的波形测量的数字。因为之前进行了写操作SL OT1、Rank1的前仿真,所以这里将在相同的情况下进行验证。

(4)固定首行,使得当鼠标上下滑动时首行是固定的。在报告的A2格中放置光标,选择菜单,冻结窗口,如图所示。

(5)在报告中滑动鼠标,直到可以看到“Operation”列显示“Write Slot 1”,如图所示。

(6)滚动鼠标,直到E栏显示“U1_B01.L9”。

因为选择不报告第一个边缘过渡,所以第一个DOS边缘在6.762ns。这个信息显示在“Clk/Strobe Crossing Threshold Timens”列中。如果将水平滚动条滑动到右侧,可以看到没有那个边缘的保持数据。

(7)从报告中记录以下数据,如图所示。

在Strobe Crossing为19.102时的建立时间tDS,ps(J列):870.5

在Strobe Crossing为19.102时的保持时间tDH,ps(P列):1194.4

(8)再次打开多层板工程会话窗口。

(9)打开示波器。

(10)单击“Save/Load”按钮,如图所示

(11)单击“Load”按钮,如图所示。

(12)打开C:\Adv_HL_Trng\Memory_Interface\postlayout\MultiBoard\DDR_Results_< date_ time>\RCV_Waveforms_Typ。

(13)在文件名称区域输入“W*",单击“打开”按钮,如图所示。

这些滤出的文件只有写人SLOT1时的接收端波形文件,正如所预期的,将看到8个波形文件。

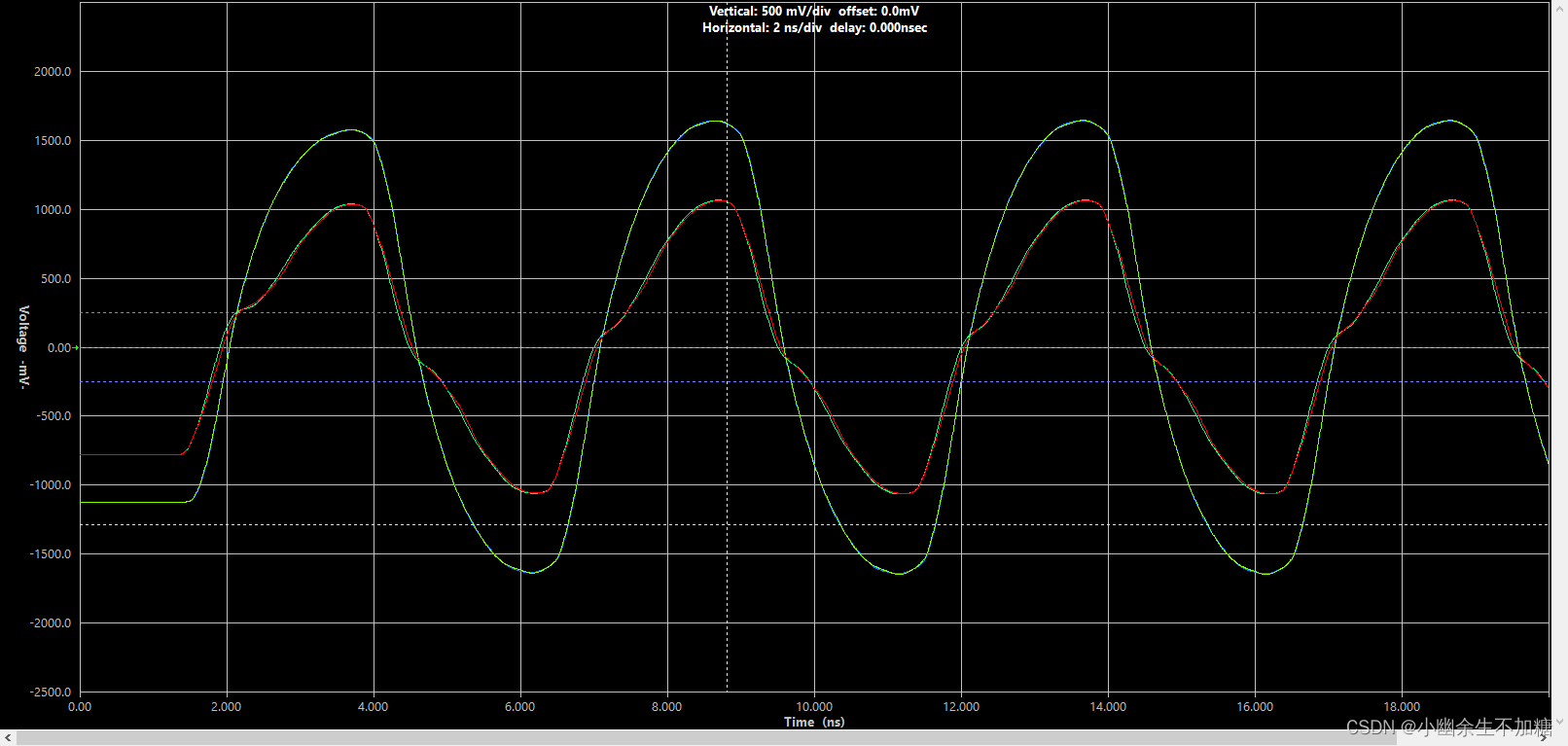

(14)使用Ctrl键选择以下波形并打开,如图所示。

.net-DO0-drv-U1 BO0.AR4-rcv-U1B01.L9-W1.csV

.net-DOS P0-drv-U1_BO0.AM8&AM7-rcv-U1_B1J7&H8-W1.csv

(15)单击“OK”按钮,关闭“Load/Save Waveforms”对话框,仿真波形文件如图所示。

(16)单击雨按钮查看所有波形。在波形图中可发现没有阈值线,这是因为这个波形是导人的波形,所以没有包含阈值信息。为了看到DQ阈值情况,需要选择一个互联的 DQ网络。

(17)选择“DQ0”网络,如图所示。

①最小化示波器窗口。

②单击“Net”按钮。

③选择任意DQ0网络,单击“OK”按钮。

(18)最大化示波器窗口。

(19)“Thresholds for”区域的设置如图所示。

(20)下降的DQ信号穿过AC Vinl时到上升的DQS信号穿过0V时之间的时间增量即为建立时间。

①单击“Track Waveform”按钮,再单击 DQS 波形。

②滚动波形到最右侧,直到到达19.102ns,放置光标在0V。

③单击“Track Waveform”按钮。

④ 选择 DQ 波形。

⑤在DQS下降沿穿过Vinl(AC)时放置光标,必须放在之前选择的DQS上升沿之前。

⑥记录Delta T的值875ps,如图所示。

(21)比较以上得到的值和步骤(7)中得到的值,这两个值应当很接近。现在知道报告中的数值就是从这里得到的。

(22)在DQ信号上升沿穿过DCVinl时和上升的DQS信号穿过0V时之间测量时间增量,即为保持时间。

注意 :对于写操作“HoldTime(FromSim)”,是上升的DQS信号穿过0V处到下降的DQ信号穿过DC Vinh处的时间增量。

6.DDR3/DDR4设计要点

DDR3依然是目前电子产品使用的主流规格,DDR4也已经开始进入消费级电子产品中。由于DDR3和DDR4的设计相对来讲比其他类型的总线设计更加复杂,需要注意硬件原理设计和PCB设计的各个环节,归纳起来主要有如下几点。

(1)电源设计要稳定,当电源不稳定时会导致抖动的增加、信号传输速率不稳定。

(2)电路阻抗匹配;要选择合适的电阻以匹配时钟/地址/控制/命令信号的阻抗。

(3)在PCB布局前,要先确定拓扑结构,是点对点,还是T形结构或者fly-by结构。

(4)若采用fly-by结构,stub线尽量短。

(5)所有的信号线,尽量远离PCB的边缘、功率器件、晶振电路、连接器等。

(6)信号参考层要分清楚,没有特殊要求的情况下,建议所有的信号都以完整的地平面做参考层。

(7)信号需要控制阻抗,并保证阻抗连续。

(8)地址/控制/命令信号与时钟信号、数据/数据掩码与数据选通信号,以及数据选通信号与时钟信号之间的长度关系要明确。

(9)信号与信号之间的距离要尽量大,以减少信号之间的串扰。

(10)参考电源布线尽量短,线宽大约为25mil;上拉电源尽量短,尽量铺铜平面。

(11)信号若换层,在换层处过孔附近,尽量添加地过孔。