1.

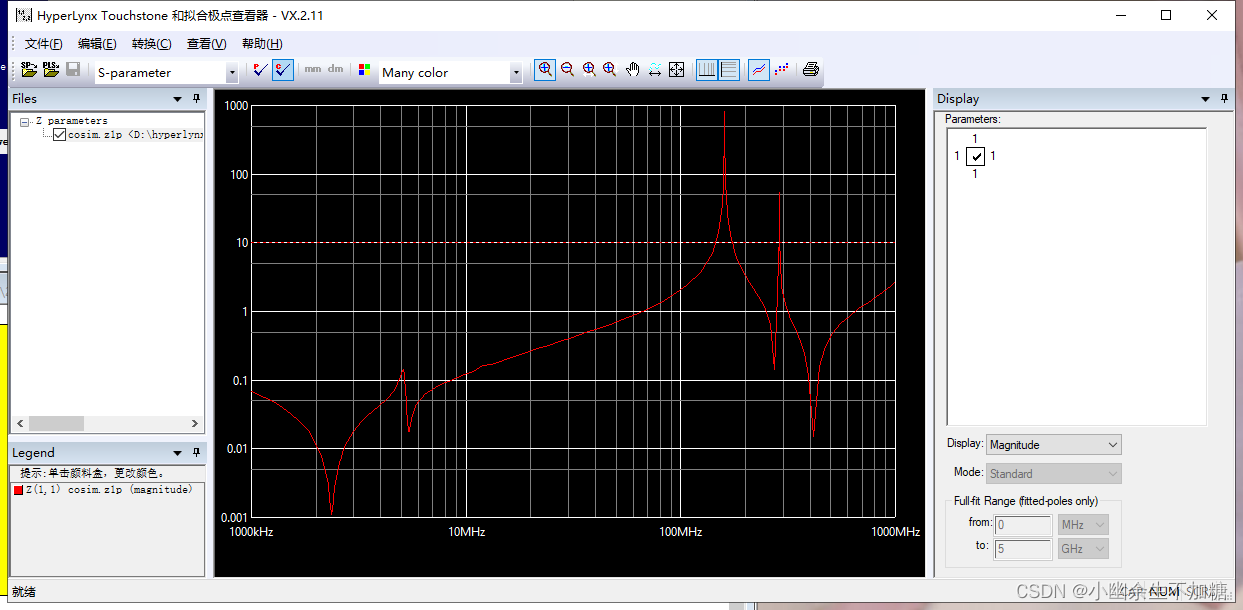

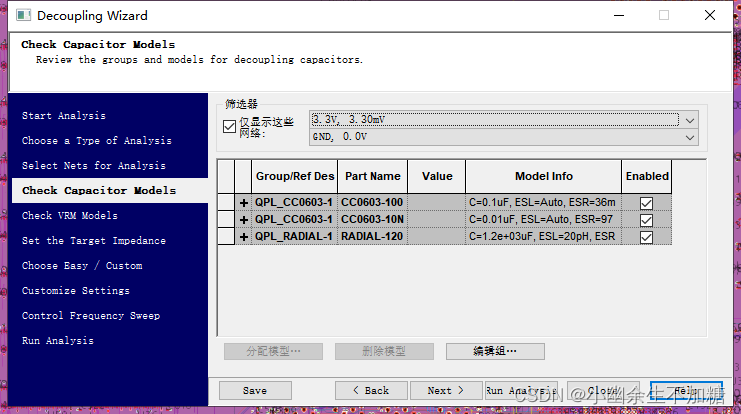

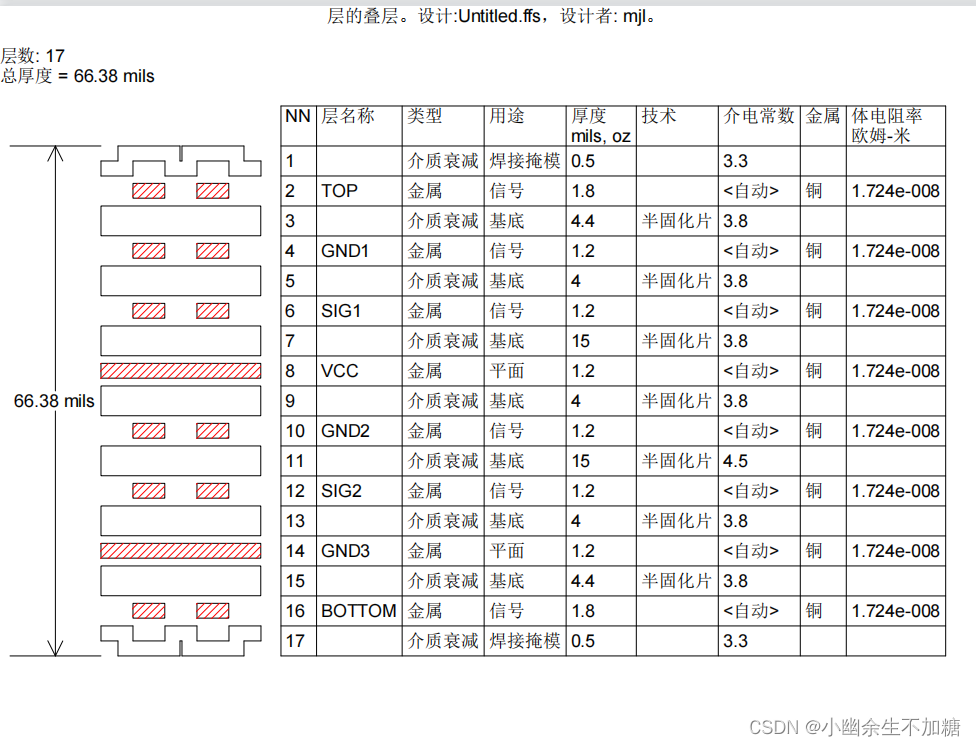

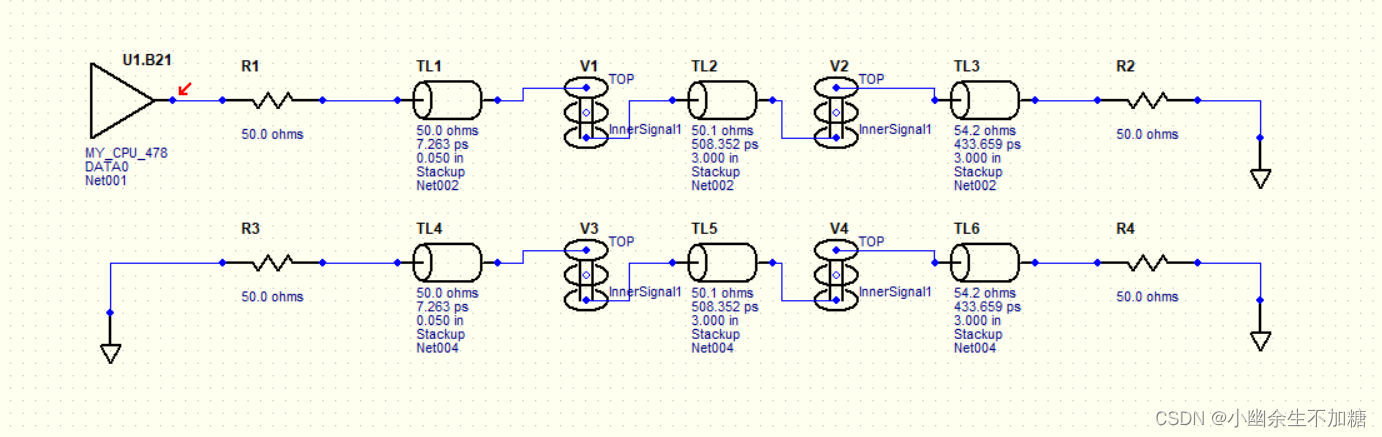

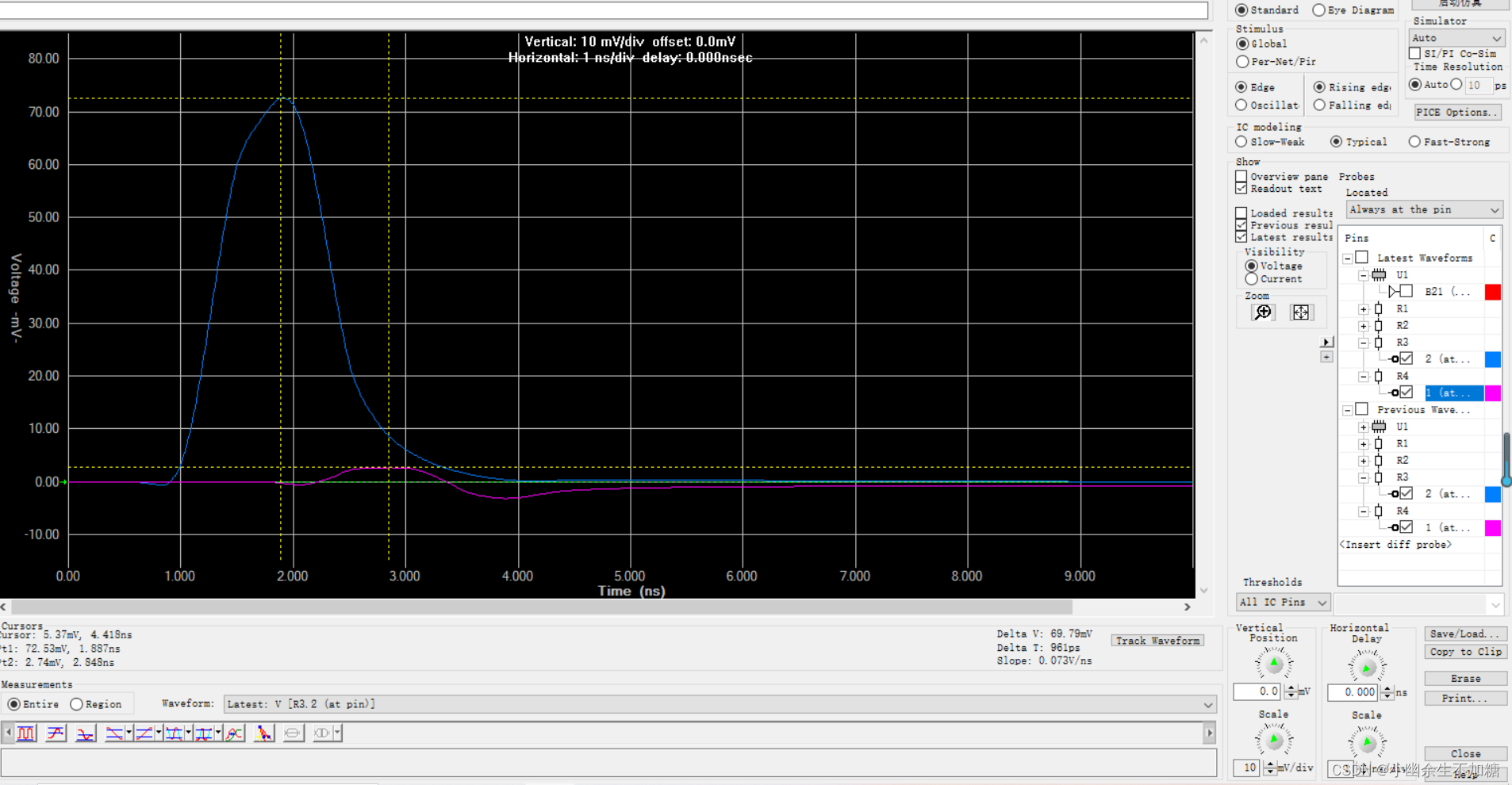

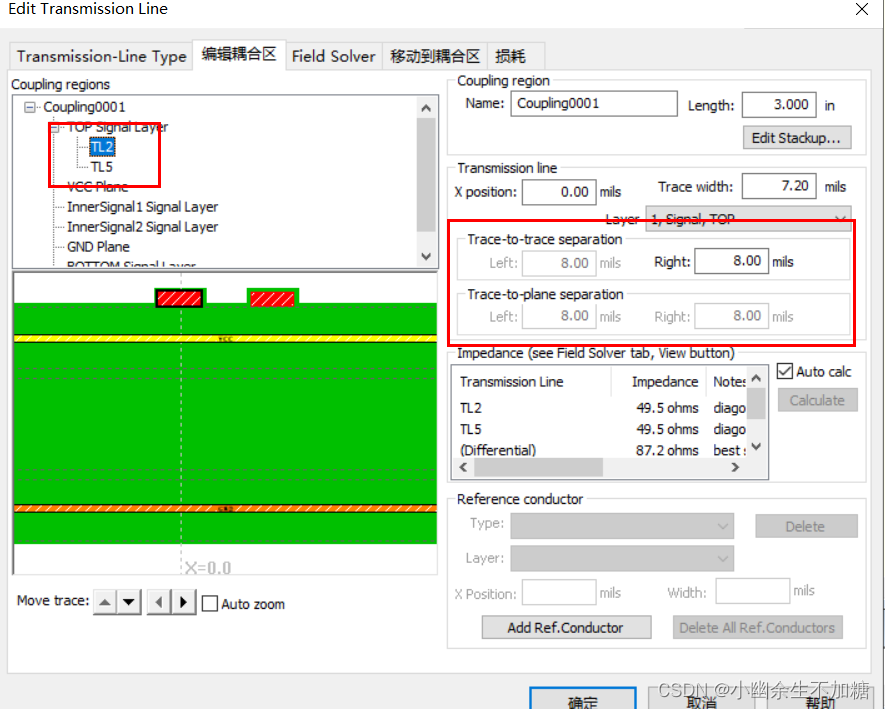

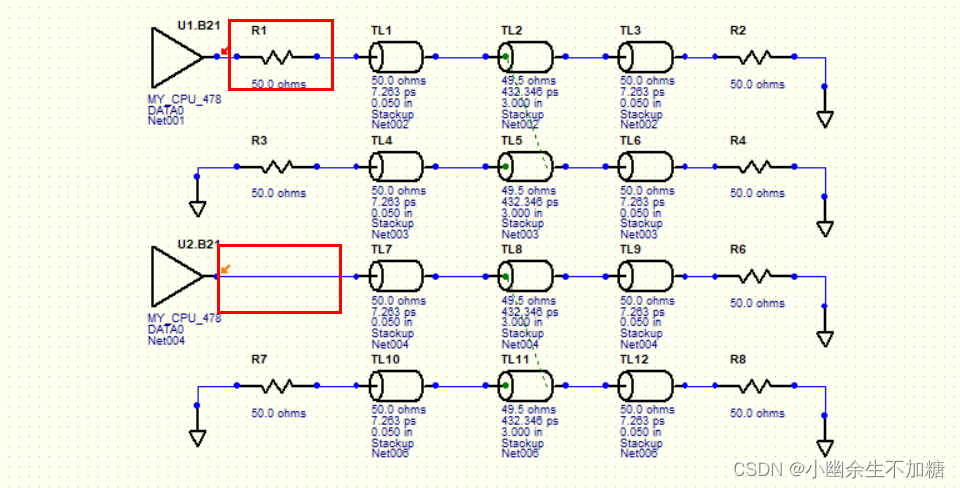

前面介绍的是微带线的串扰仿真,其实带状线的串扰与微带线的串扰有比较大的不同。主要是在拓扑结构中传输线TL2和TL5为带状线,分布在第三层,微带线与带状线通过过孔连接。带状线的仿真拓扑如图所示:

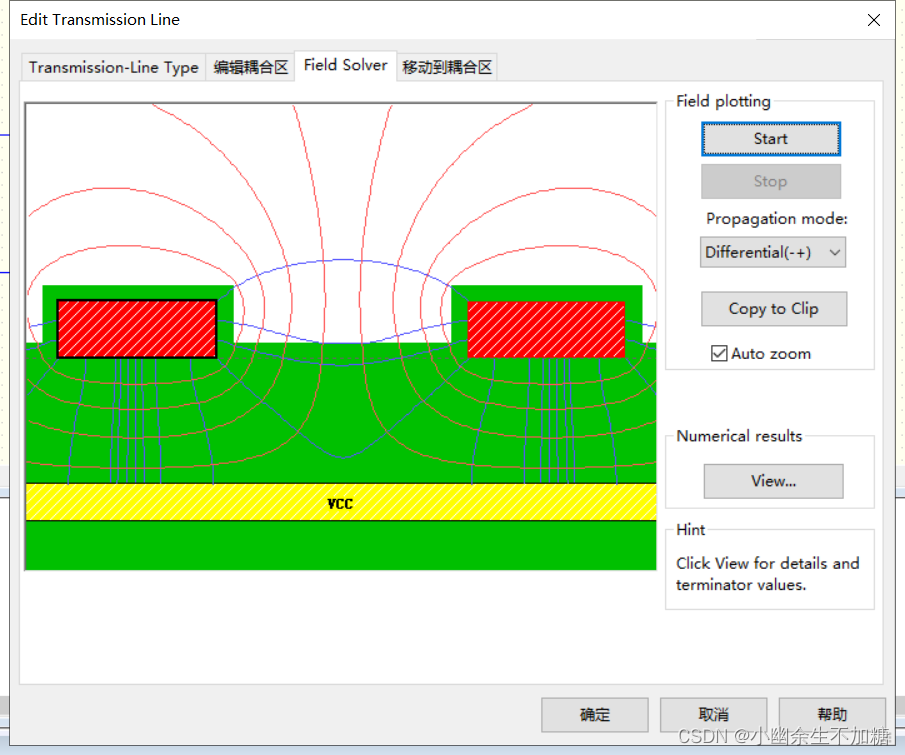

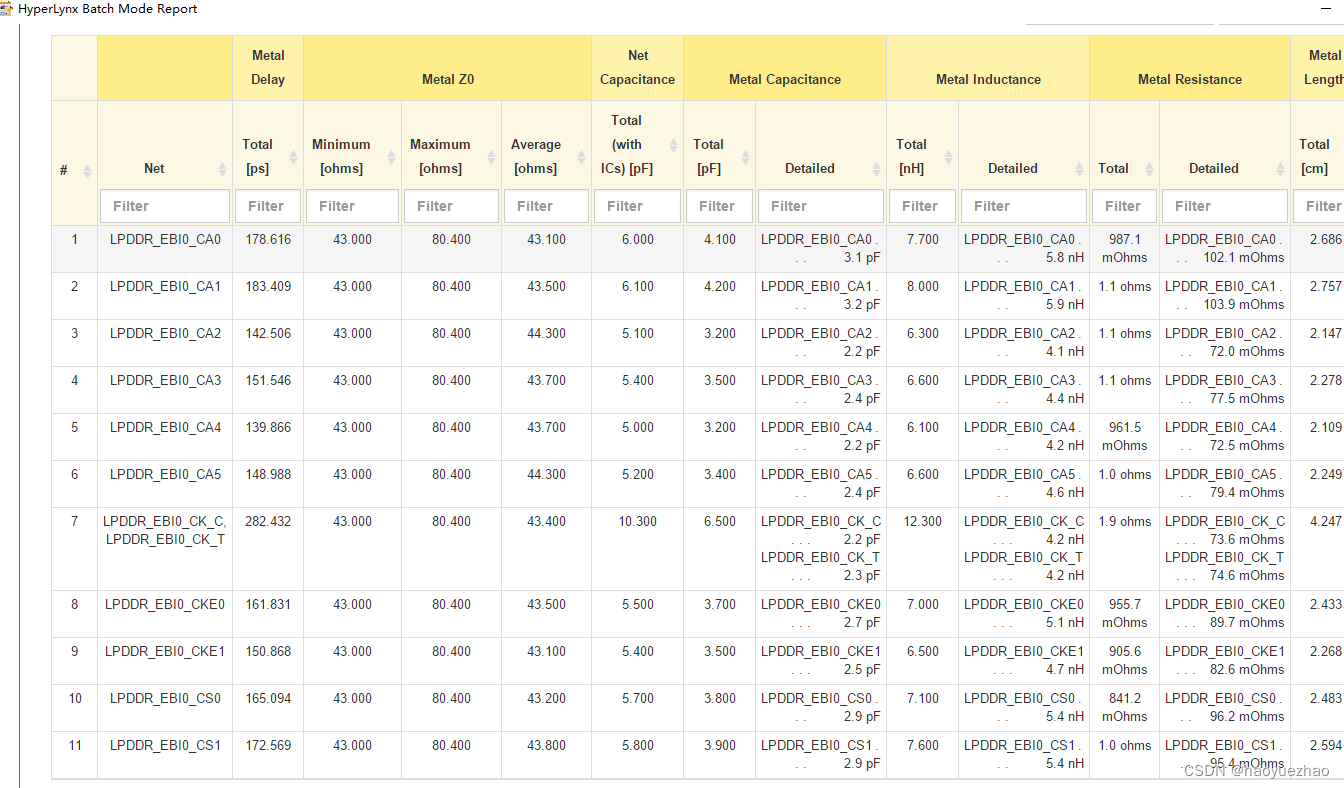

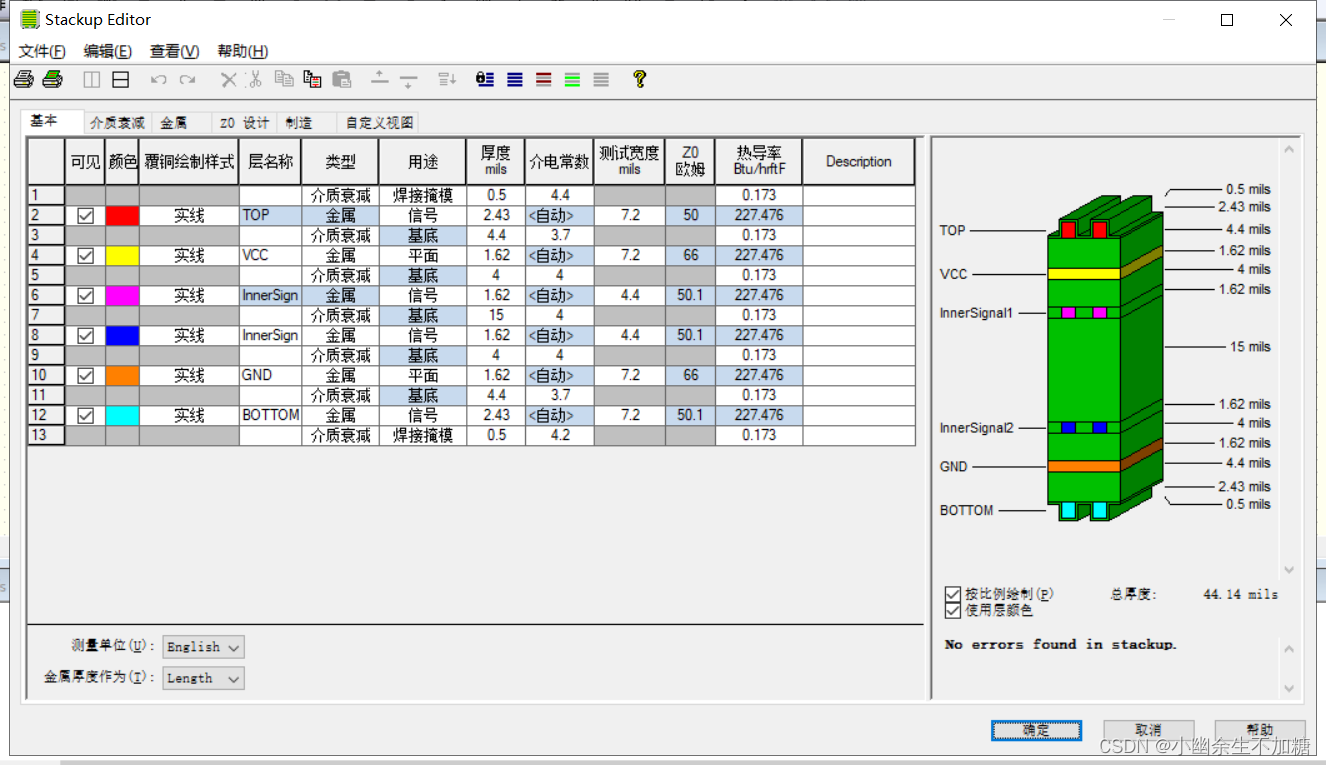

叠层信息如图所示:

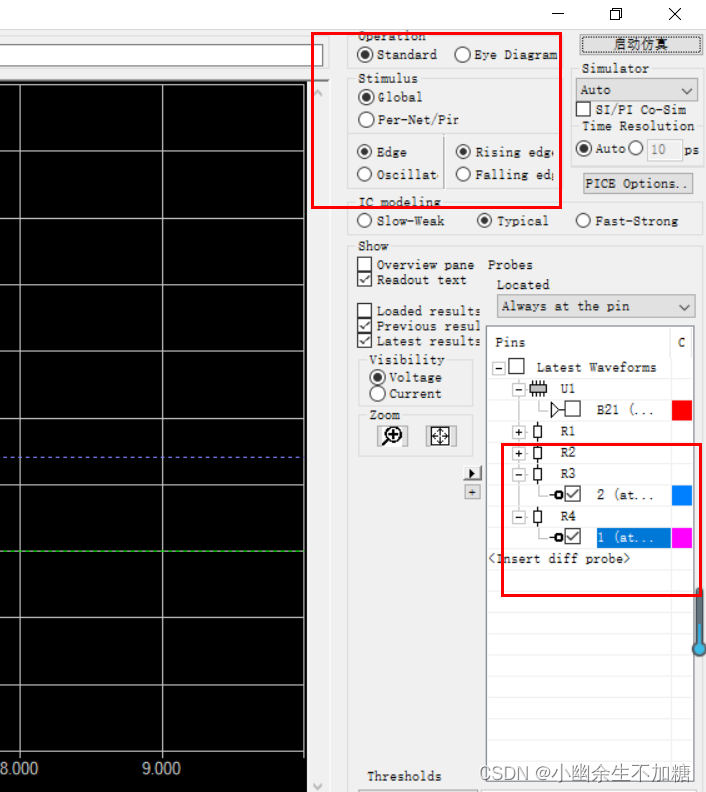

在示波器页面,操作选择为标准的(Standard),仿真激励选择边沿(Edge)和上升边沿(Rising edge),选择在电阻R3和R4处观察波形,其他设置不变。具体设置如图:

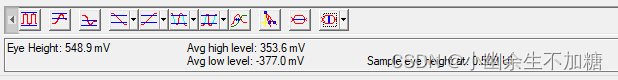

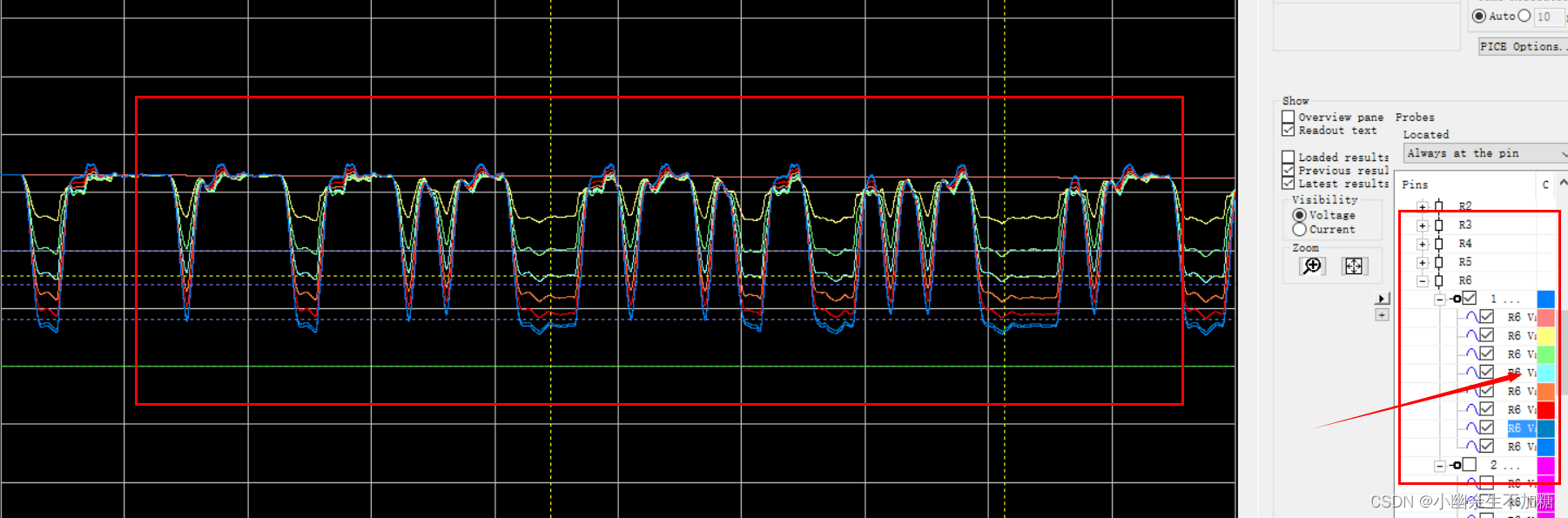

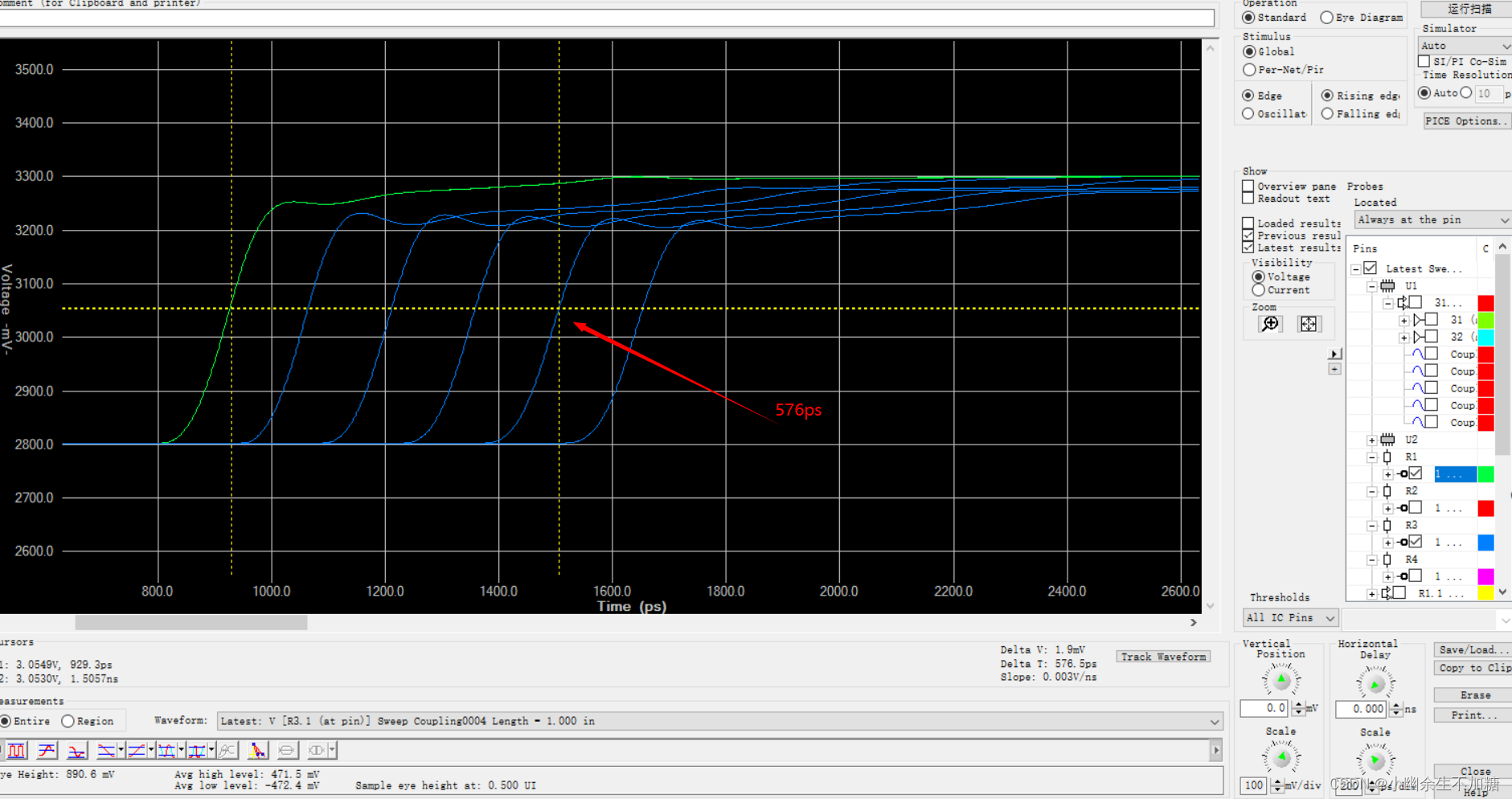

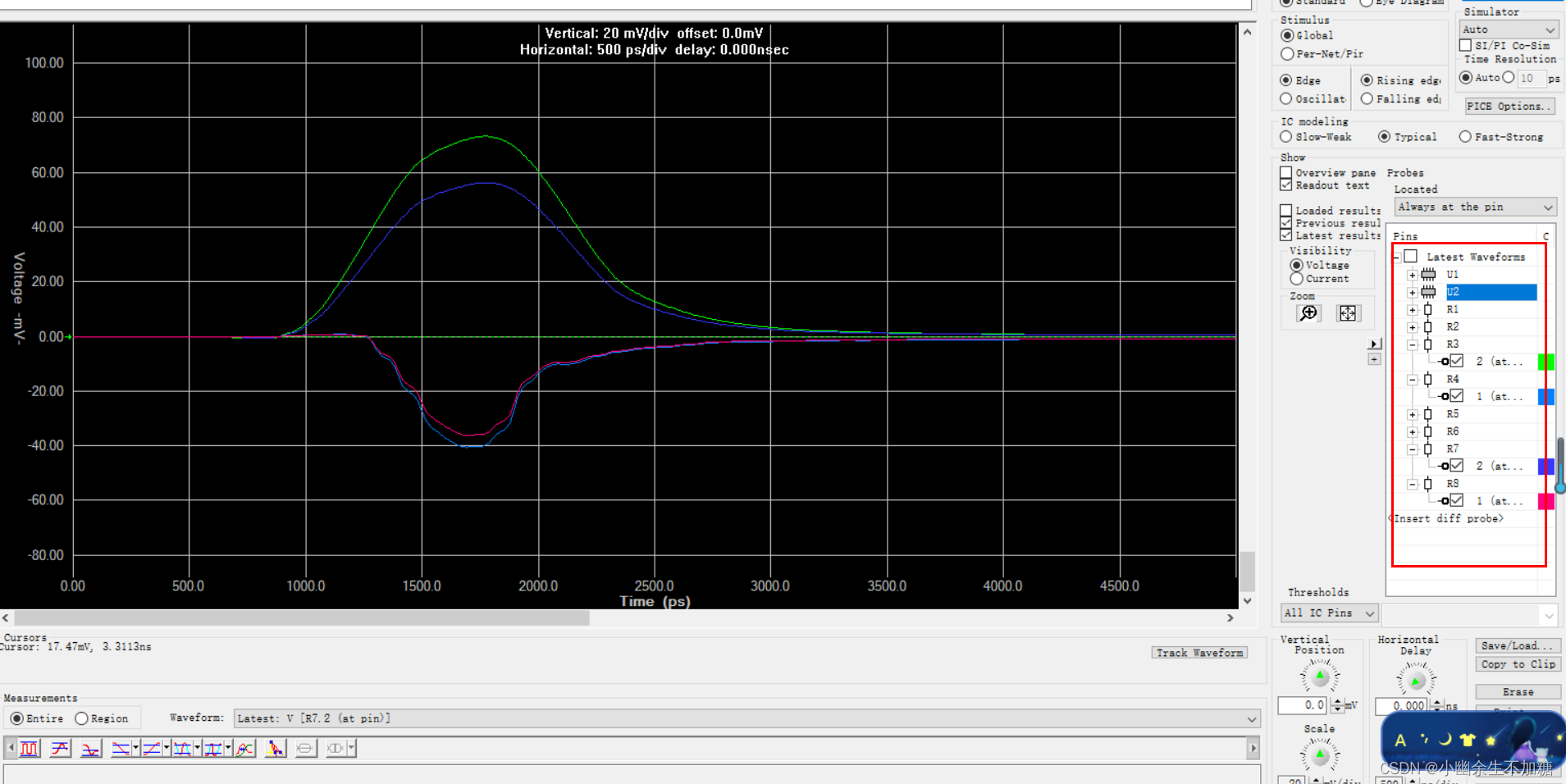

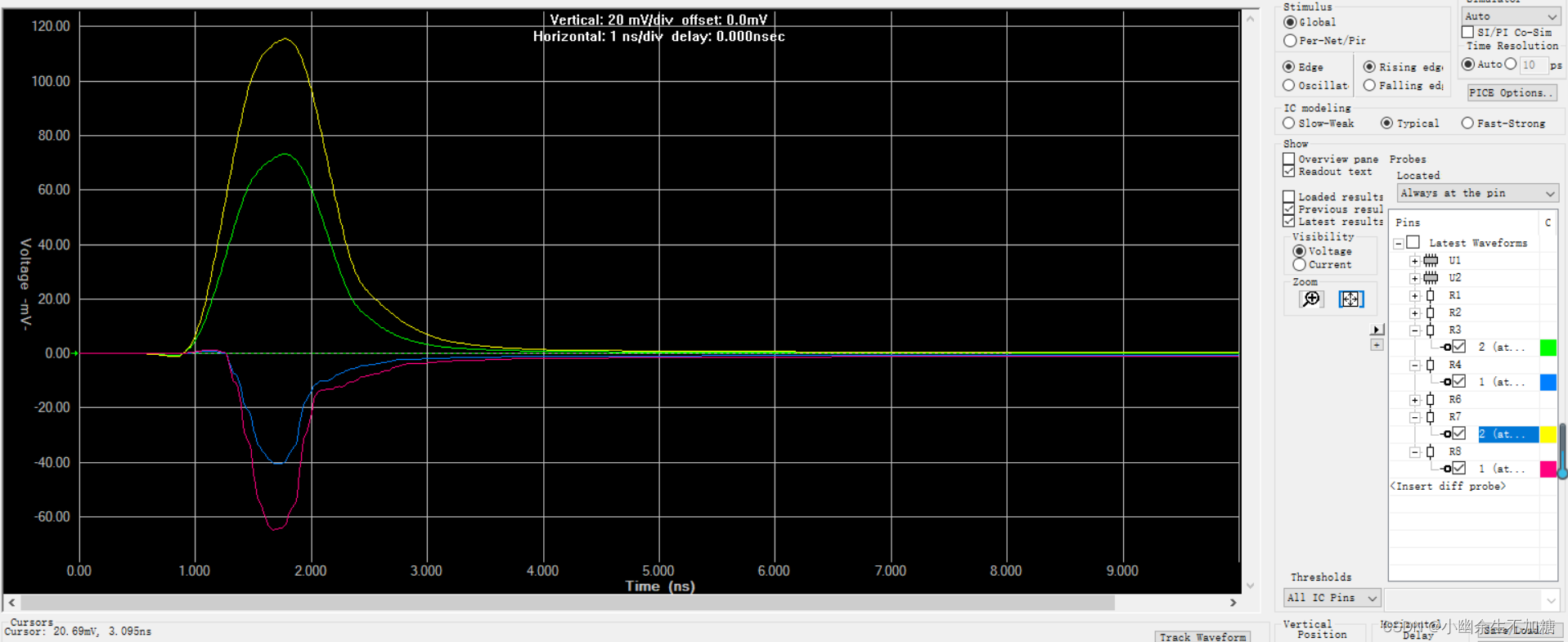

设置完成之后,单击Start Sweep按钮,观察下拉电阻R3和R4处的波形,如图所示:

分别测量近端串扰和远端串扰的幅值,分别为72.53mV和2.74mV。相对于近端串扰幅值,远端串扰的幅值可以近似为0,忽略不计。理论上,在均匀的带状线中,远端串扰的幅值为0,仿真结果与理论相符。

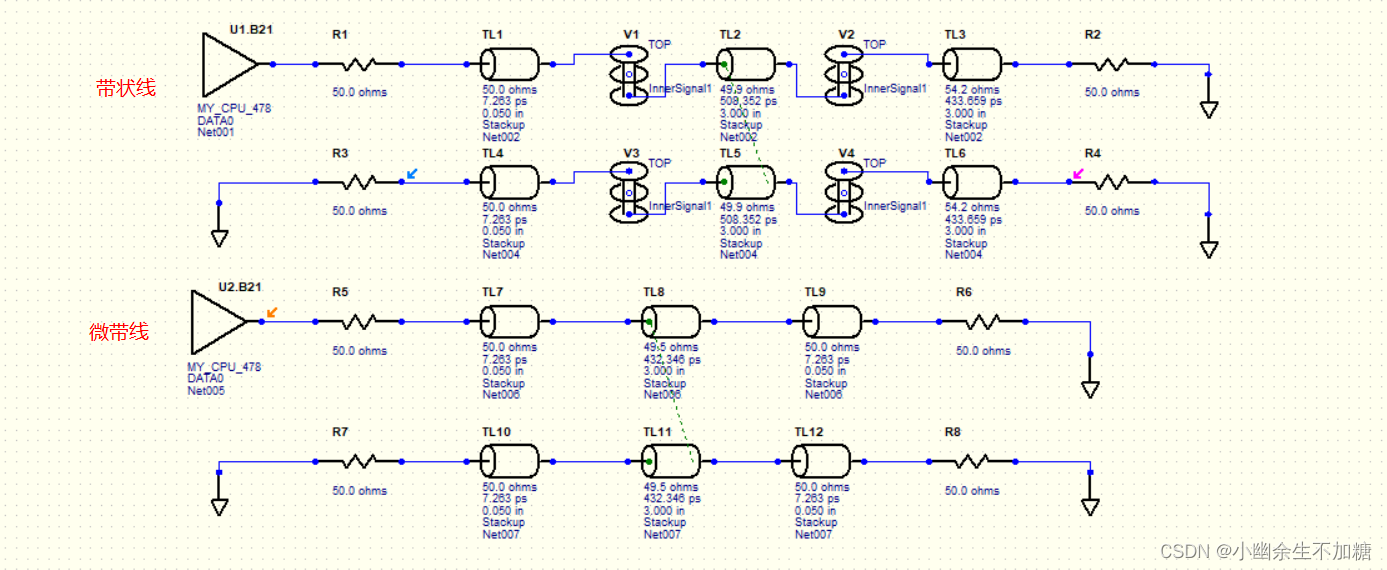

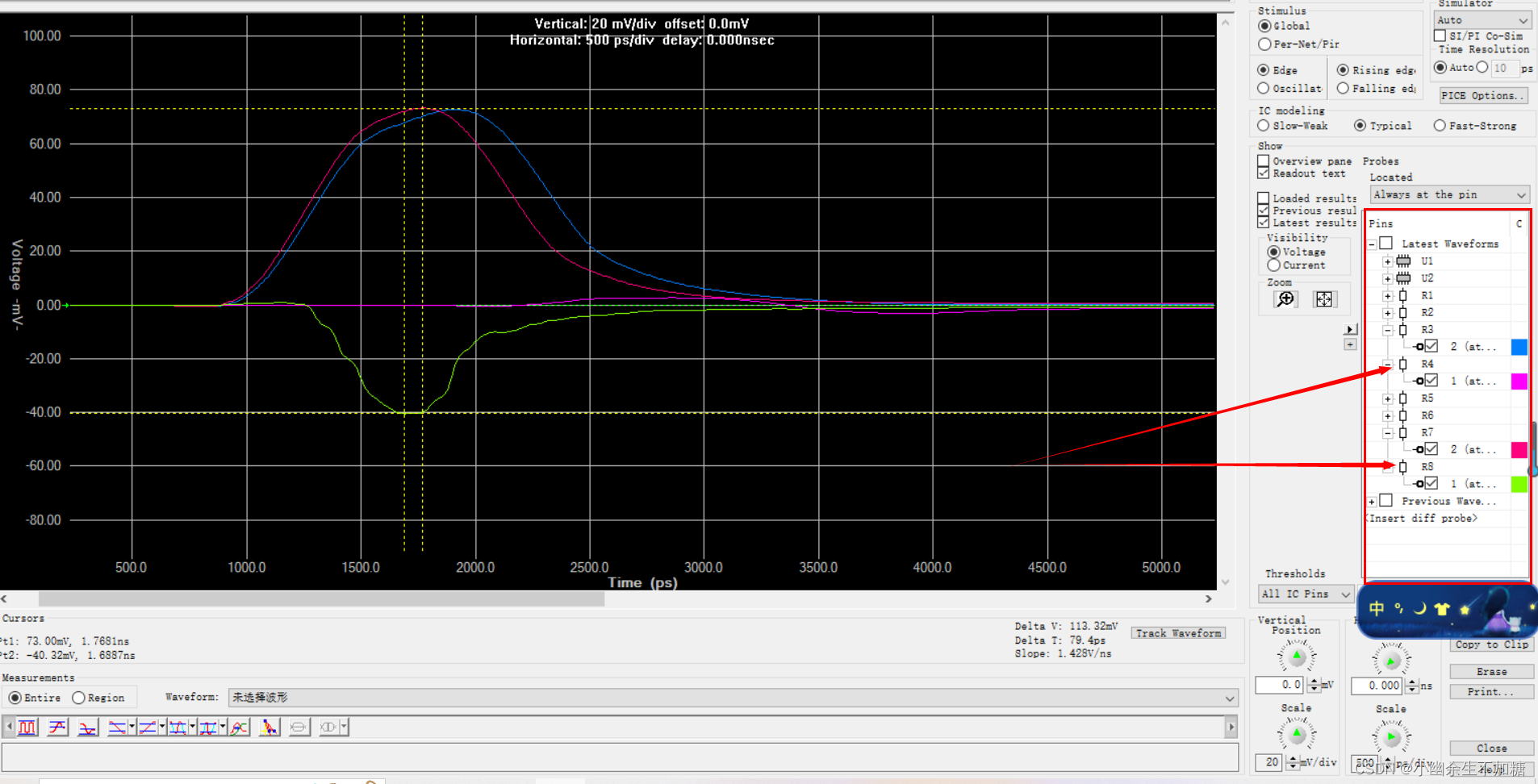

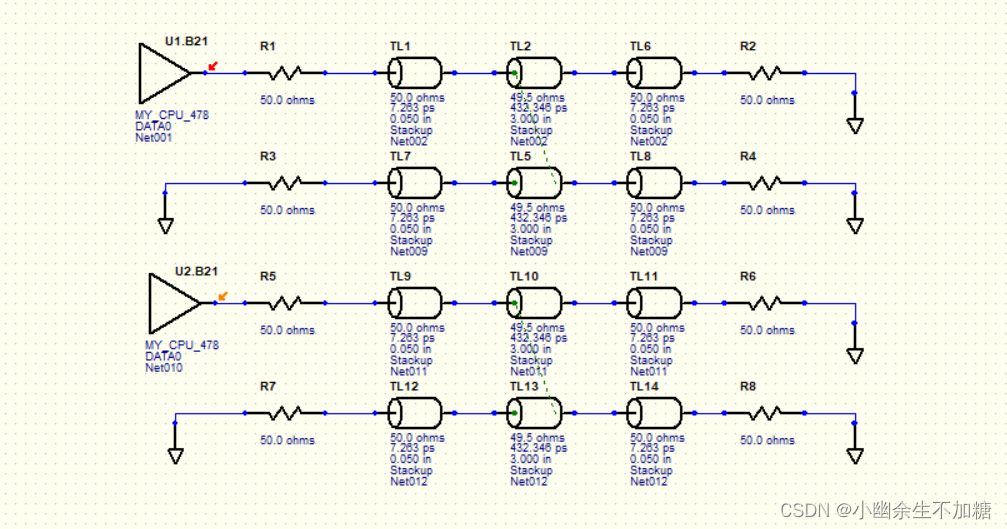

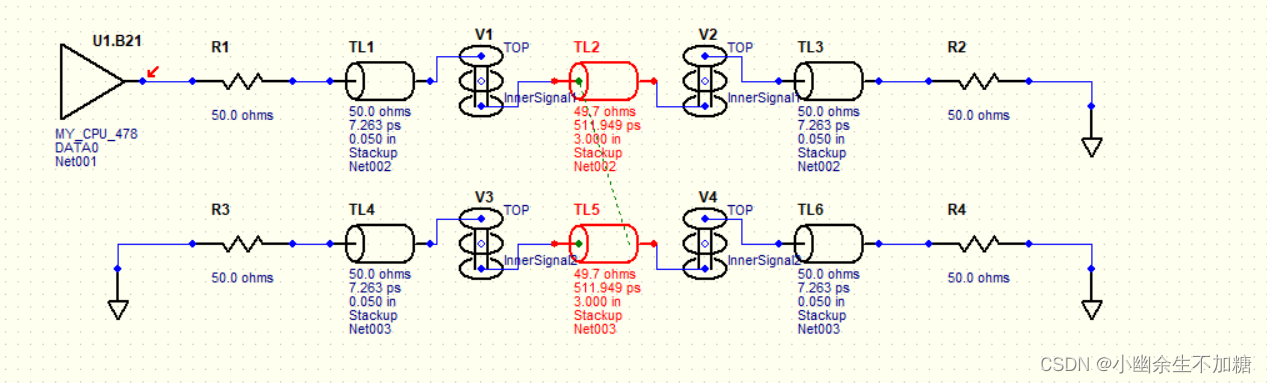

对耦合微带线和带状线同时建模,使用相同的激励源、相同长度和近似相同相同线宽的带状线和微带线,仿真拓扑如图所示:

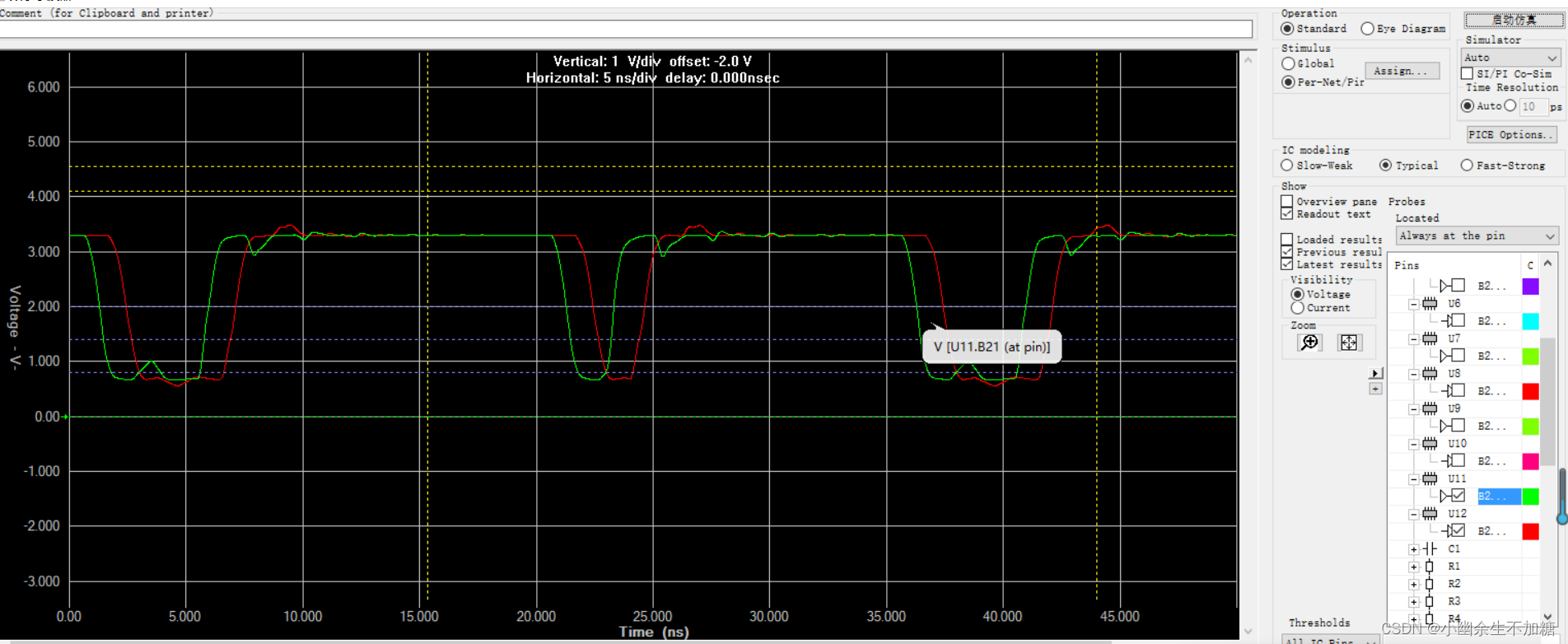

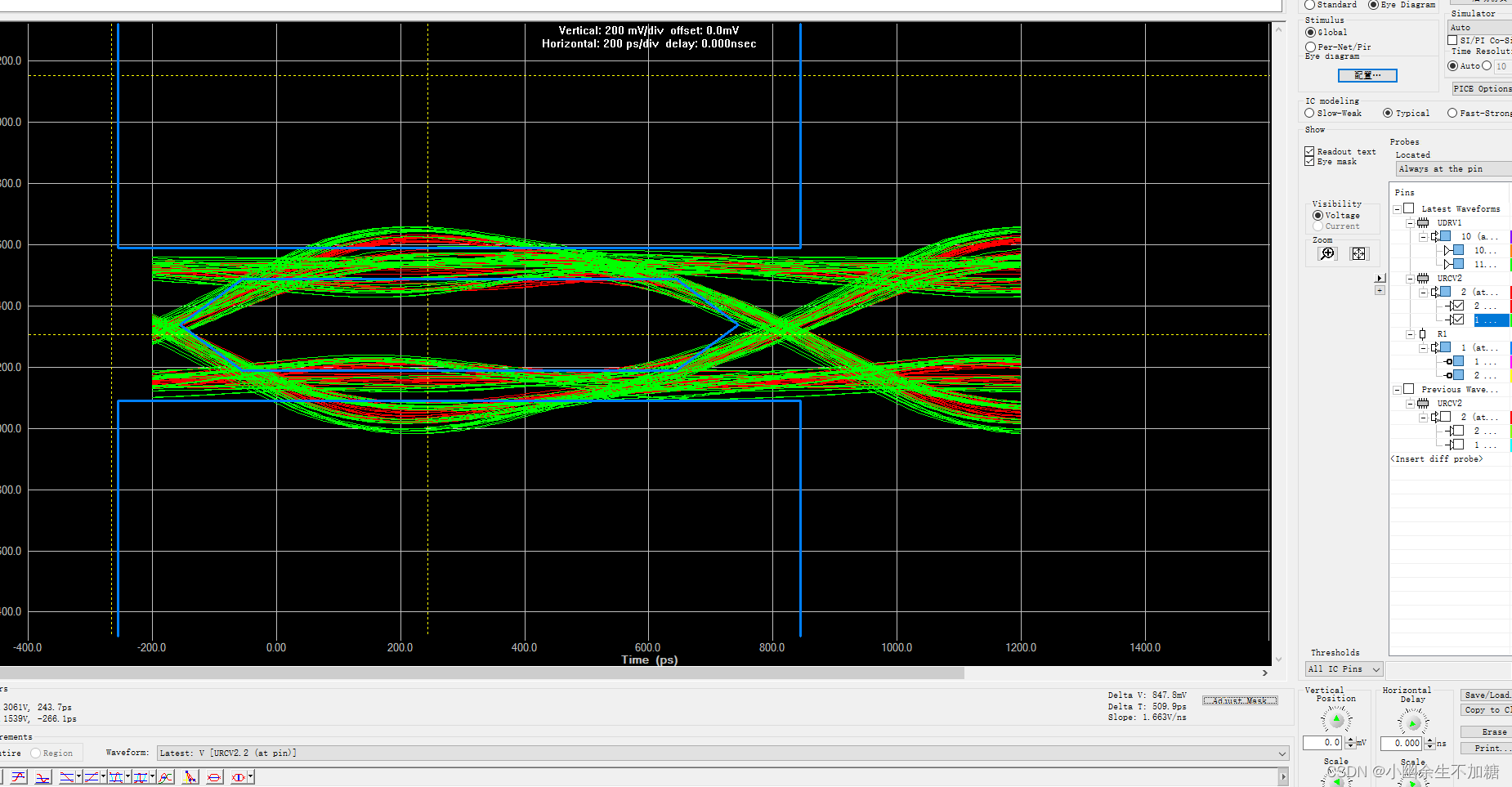

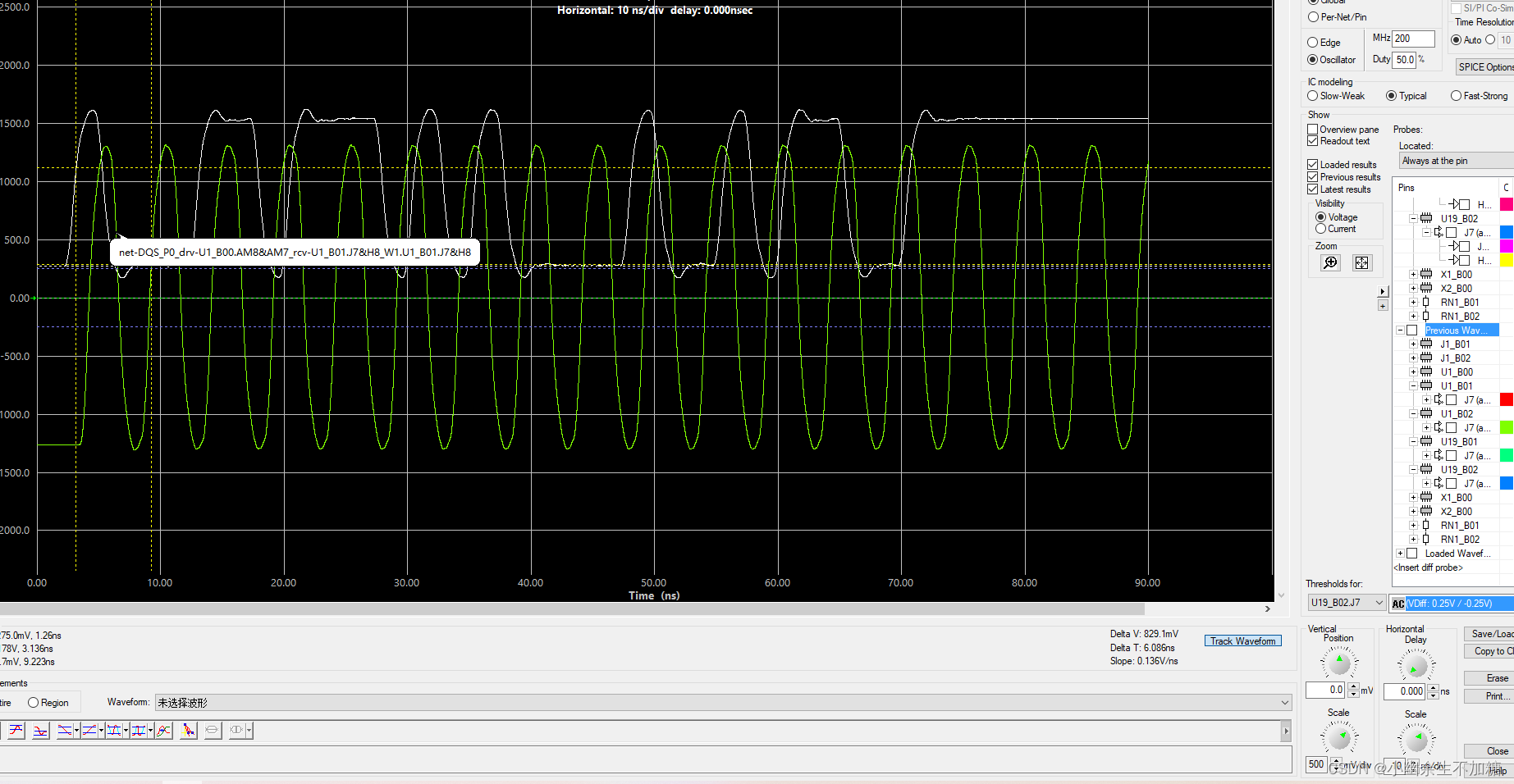

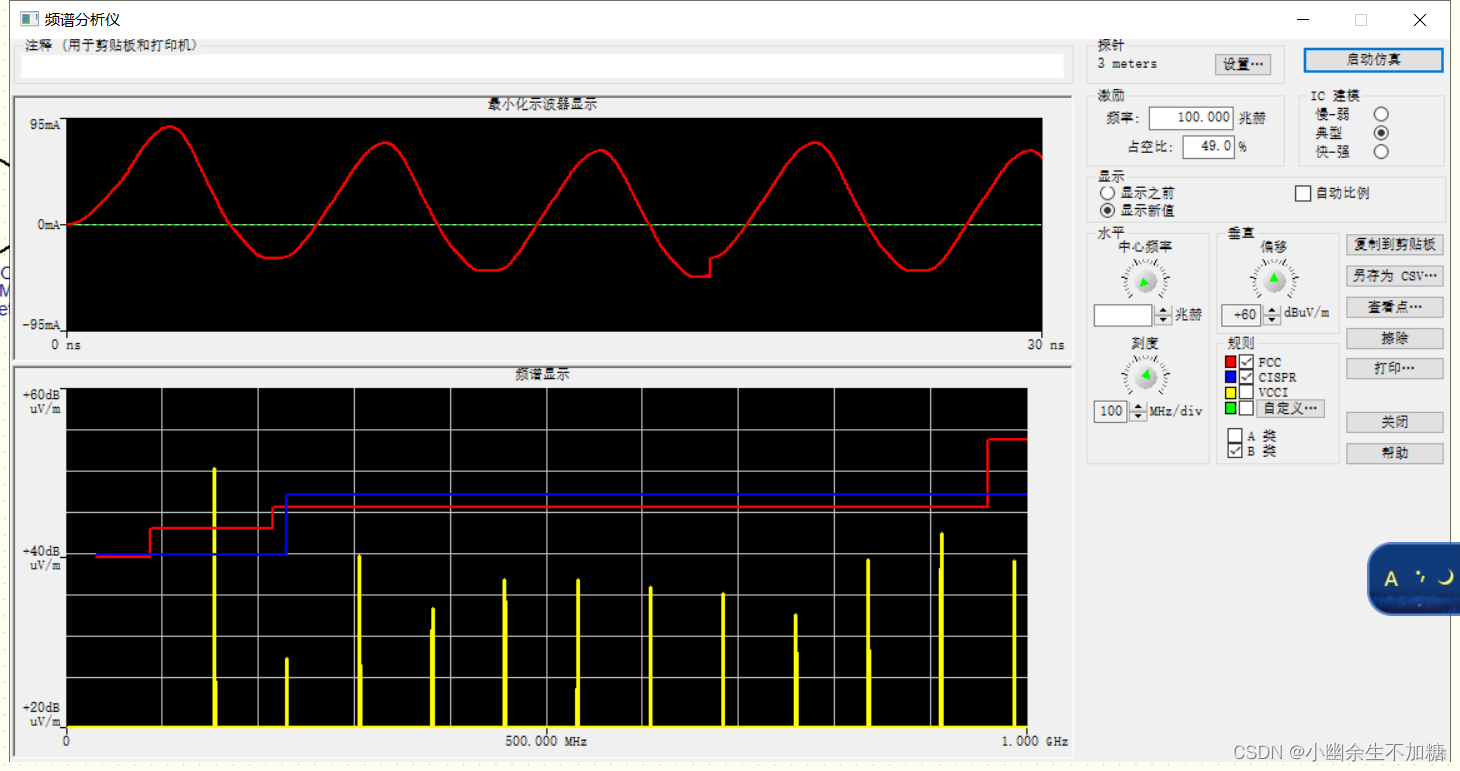

仿真获得到的对比波形如图所示:

R3和R4为带状线的近端和远端,R7和R8为微带线的近端和远端,从仿真结果上分析,在R3和R7上测量的近端串扰值几乎一样,而在 R4和R8上测量的远端串扰值差异非常大。这也就是为什么很多大型的电子产品设计,当信号的速率比较高、传输线长度比较长时,工程师会把传输线设置为内层的带状线。

当然, 在设计时需要综合考虑,如布线在内层时会增加过孔、电信号在内层传输的速度比外层的慢等。

2.传输线到参考层的距离对串扰的影响

不管是设计 PCB,还是设计连接器和线缆,工程师都追求传输线尽量靠近参考层,因为这样的设计可以使信号最快找到回流路径。那么传输线到参考层的距离是否会对串扰有影响呢?前面在介绍串扰定性分析时,都是只有一个变化的参数,但传输线到参考层的距离的改变,首先会改变传输线的阻抗,除了距离的改变,还会增加阻抗这个变量。因此,为了使仿真简单、容易观察,利用PCB层叠结构的对称性,分别建立两个拓扑结构,一个在第1层(TOP),另一个在底层(Bottom),只是改变参考层的距离和线宽以满足传输线的阻抗为50Ω,其他参数不变,如图 所示:

TL2和TL5为第1层的传输线,传输线到参考层的距离为4mil,线宽为6.36mi;TL8 和 TL11为底层的传输线,传输线到参考层的距离为5m il,线宽为8.25mil,传输线的阻抗都为单端 50Ω。电阻 R3 和 R7为近端串扰接收端,电阻 R4和R8为远端串扰接收端,仿真结果如图所示:

很显然从仿真结果来看离参考层的距离越远,串扰越大。

PCB设计需要整体考虑布局、布线及生产工艺,单纯从串扰方面而言,传输线到参考层的距离越近越好,对于整体设计和生产而言,并不一定是信号到参考层的距离越近越合适。因为在高速电路设计中,信号到参考层的距离会影响传输线的阻抗,距离越近,阻抗越小。为了匹配设计的阻抗,会使传输线线宽变小以增加阻抗,这就会使加工工艺变得更加复杂,或者使 PCB 材料的介电常数变小,所以还是要综合考量功能设计和生产制程的能力。

3.相邻布线层之间的串扰

在电子产品的发展中,小型化、轻薄化越来越越成为一种趋势,特别是现在一些领域都使用到软板设计,这就使得整个电子电路板设计得非非常薄,层与层之间的距离也非常近。那么这就会带来一些串扰的问题,特别是在轻薄化的产品中,相邻层都是布线层时,串扰就是一个非常难以解决的问题。

下面通过串扰仿真实验分析相邻层布线的设计。

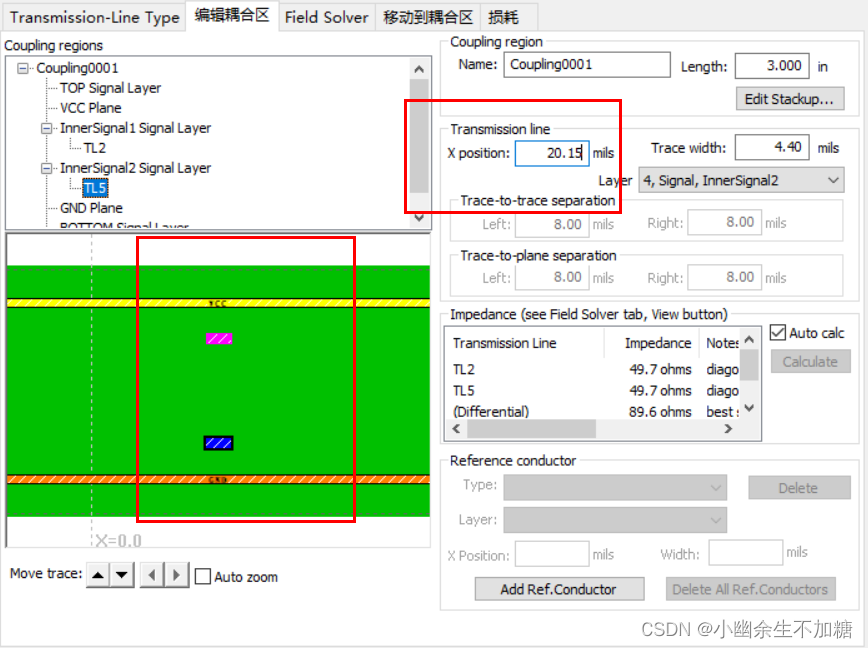

相邻层布线大部分都出现在内层的带状线上, 所以在仿真拓扑结构中的传输线应该设置到内层,TL2 放置在第层Sig03,TL5放置在第4 层,第3层与第4层之间的距离为5mil仿真拓扑结构如图所示:

在设置TL2与TL5相互耦合时需要注意,耦合设置与前面介绍的步骤一样,另外还需要设置传输线在X轴方向上的坐标,设置为完全耦合时,两段传输线的X坐标位置相同,如图所示:

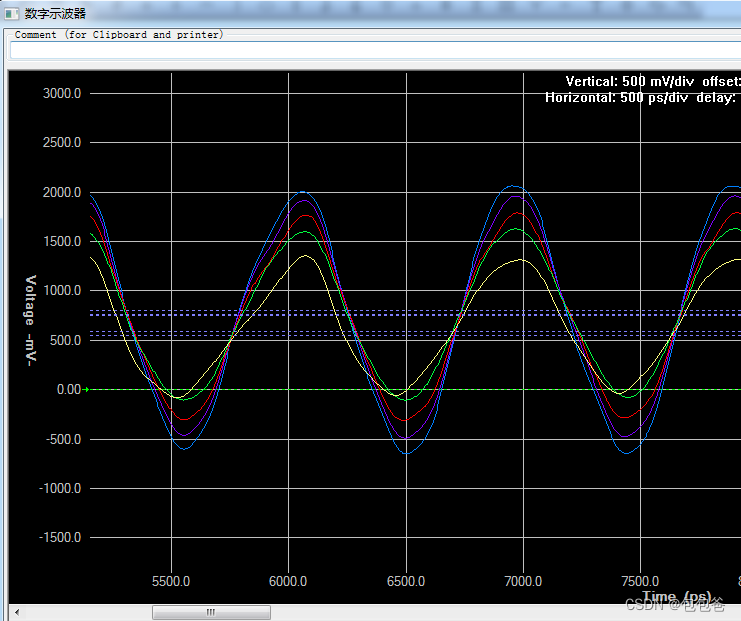

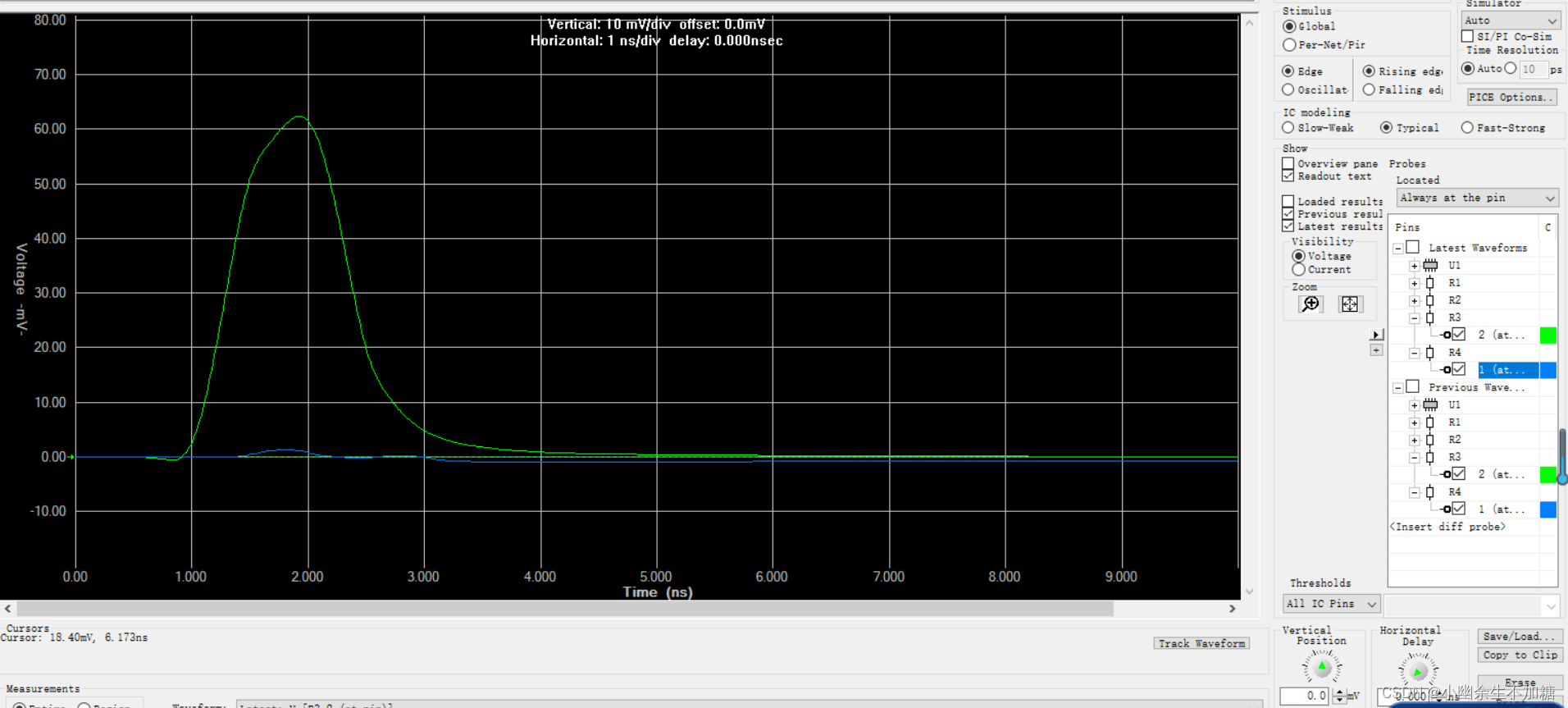

设置完成之后,开始仿真。根据前面的仿真分析可知,带状线的远端串扰几乎为0,所以在这个仿真中,只需要关注近端串扰,如图所示:

从仿真波形上看,在电阻R3上测得的近端串扰值为63.32mV。

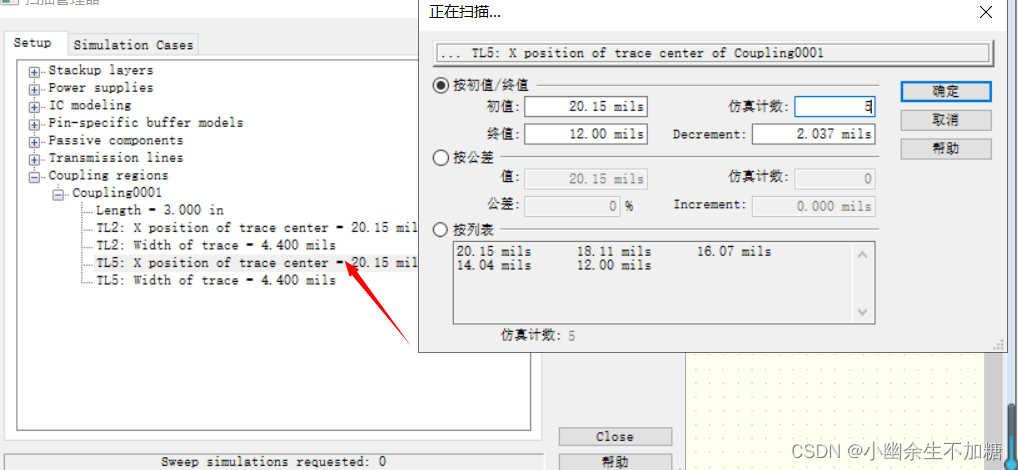

改变耦合区域的大小,可以通过参数扫描的方式进一步分析,扫描参数如图所示:

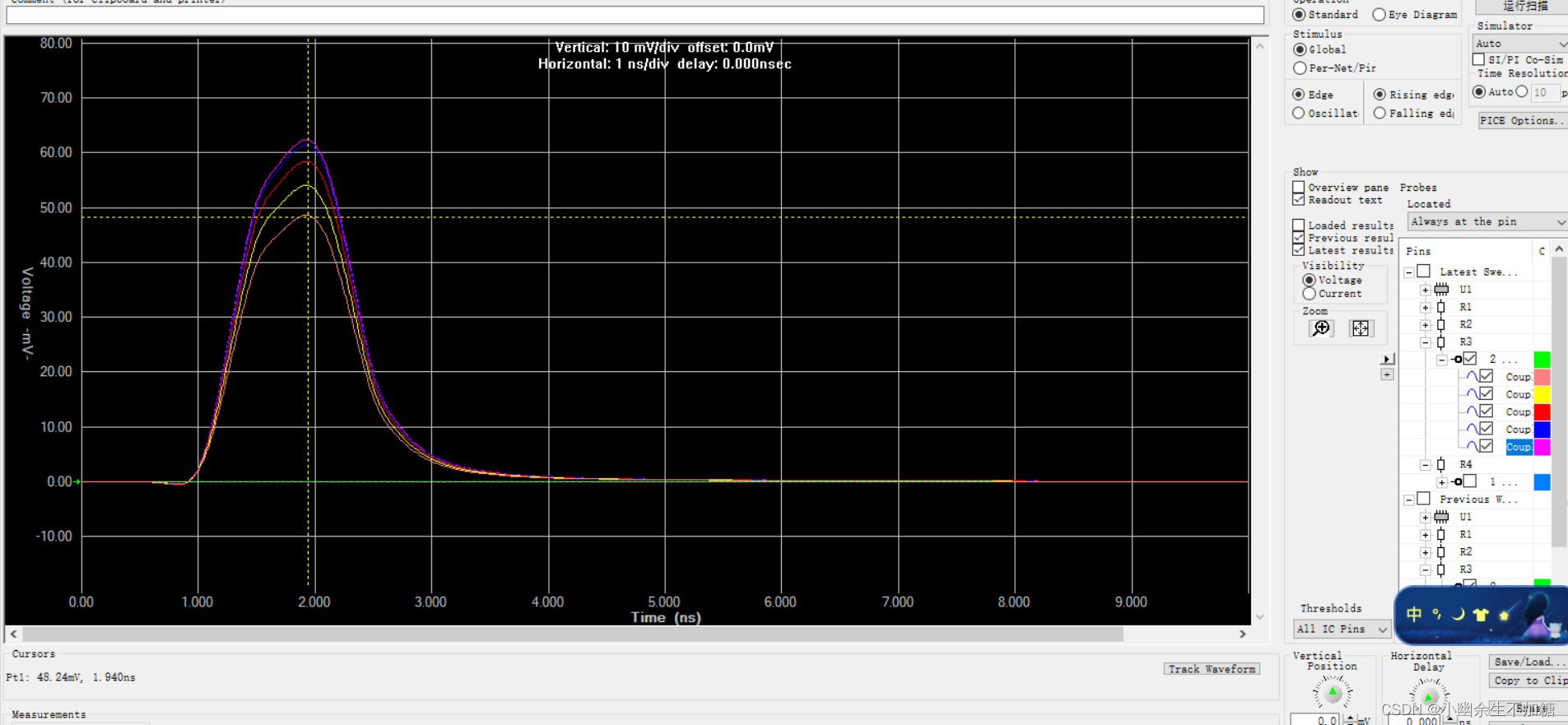

反正结果如图所示:

在电阻R3上测得的近端串扰值分别为:62.31mV,61.37mV,58.37mV,54.05mV,48.24mV,从测得的数据和仿真波形来看,说明相邻布线层相互耦合的距离越近,串扰越大。所以在相邻层布线设计中,在层与层之间的距离确定之后,一般不能使用重合或者平行布线,交叉布线是相对较好的选择。

4.传输线链路阻抗不匹配的串扰仿真

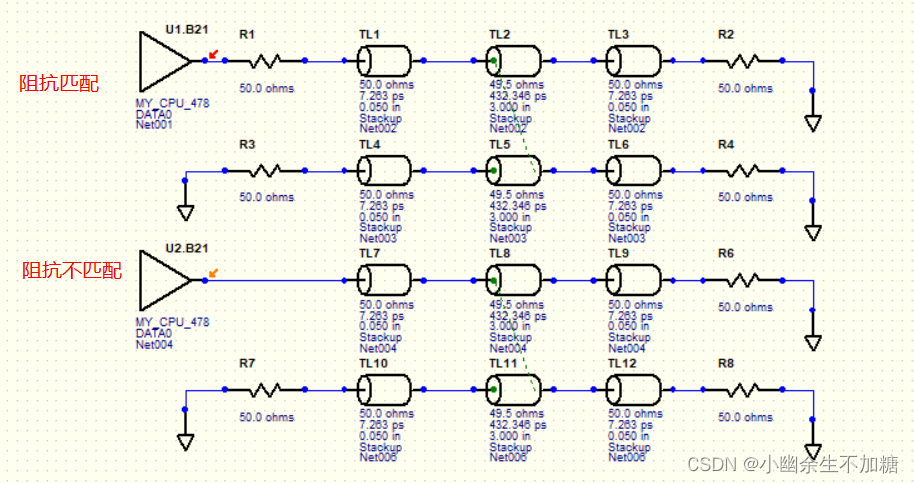

前面研究的都是在链路阻抗匹配的情况下观察串扰的波形。当传输链路上出现阻抗不匹配时,信号传输到不匹配的点时会发生反射。那么如果链路阻抗不匹配时,串扰会如何变化呢?两个仿真拓扑如下:

一个阻抗匹配一个阻抗不匹配的对比。

区别在于:

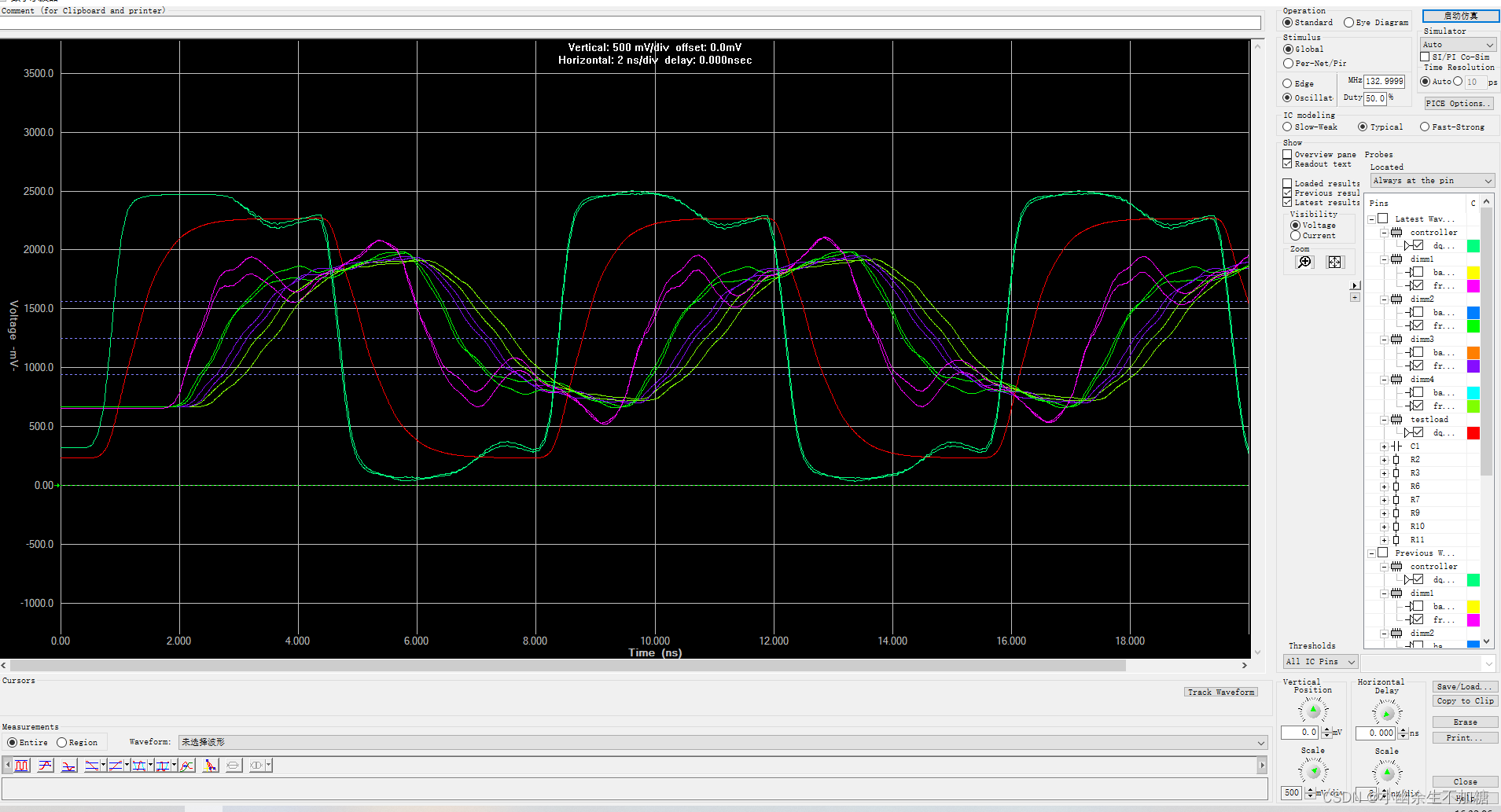

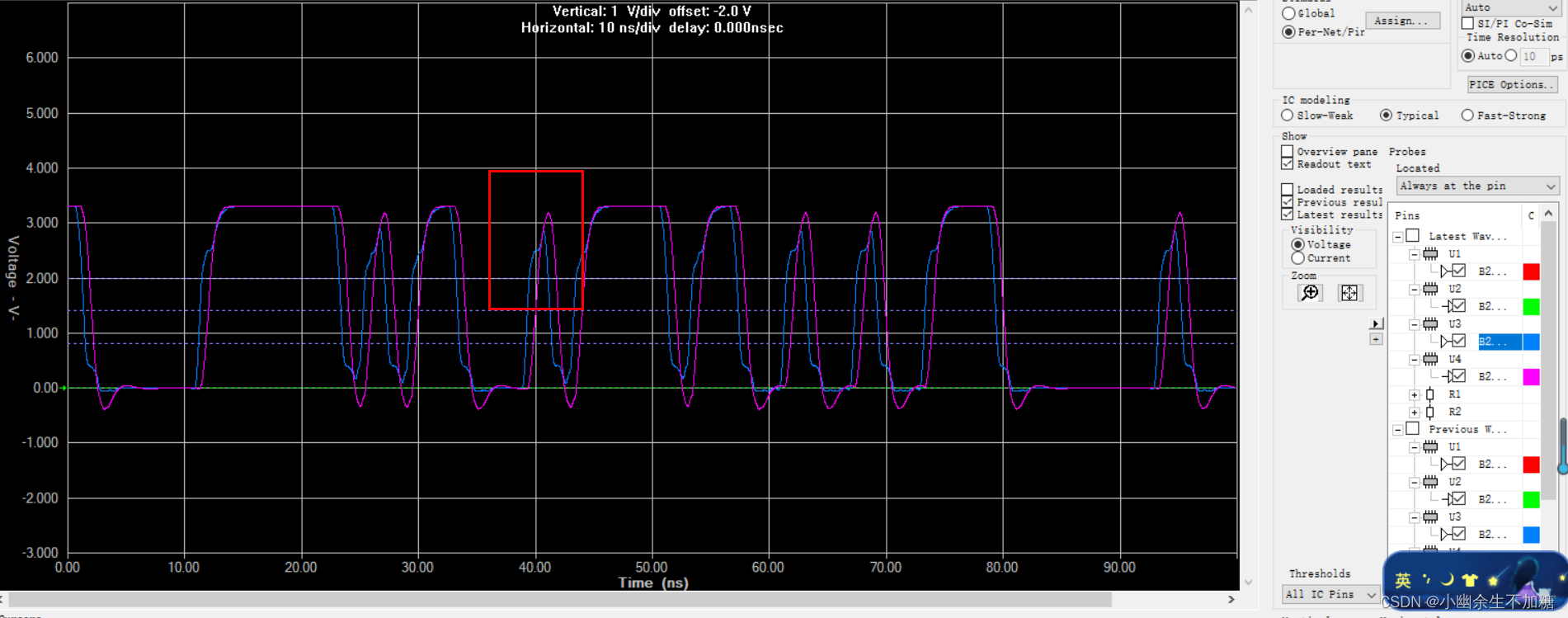

仿真波形如图所示:

从仿真波形上分析,在电阻R3和R7处测得的近端串扰值分别是31.46mV和53.99mV,在电阻R4和R8处测得的远端串扰值分别为51.33mV和90.76mV。显然,传输链路阻抗不匹配时,不管是近端串扰还是远端串扰都会比匹配好的链路的串扰大很多。所以在做电路设计时,尽量使整个传输链路上的阻抗匹配记,这样会造成信号完整性问题。

5.串扰定量仿真实例

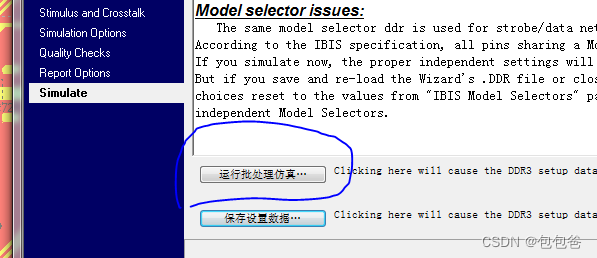

前面介绍的都是串扰的定性仿真分析,串扰的定量分析方式也类似,只是把接收端的电阻更换为实际使用的芯片模型。一般的仿真拓扑如图所示:

从仿真波形上分析,并测得U2的最大值是有串扰的,幅值为3.154V,没有串扰时是2.74V。

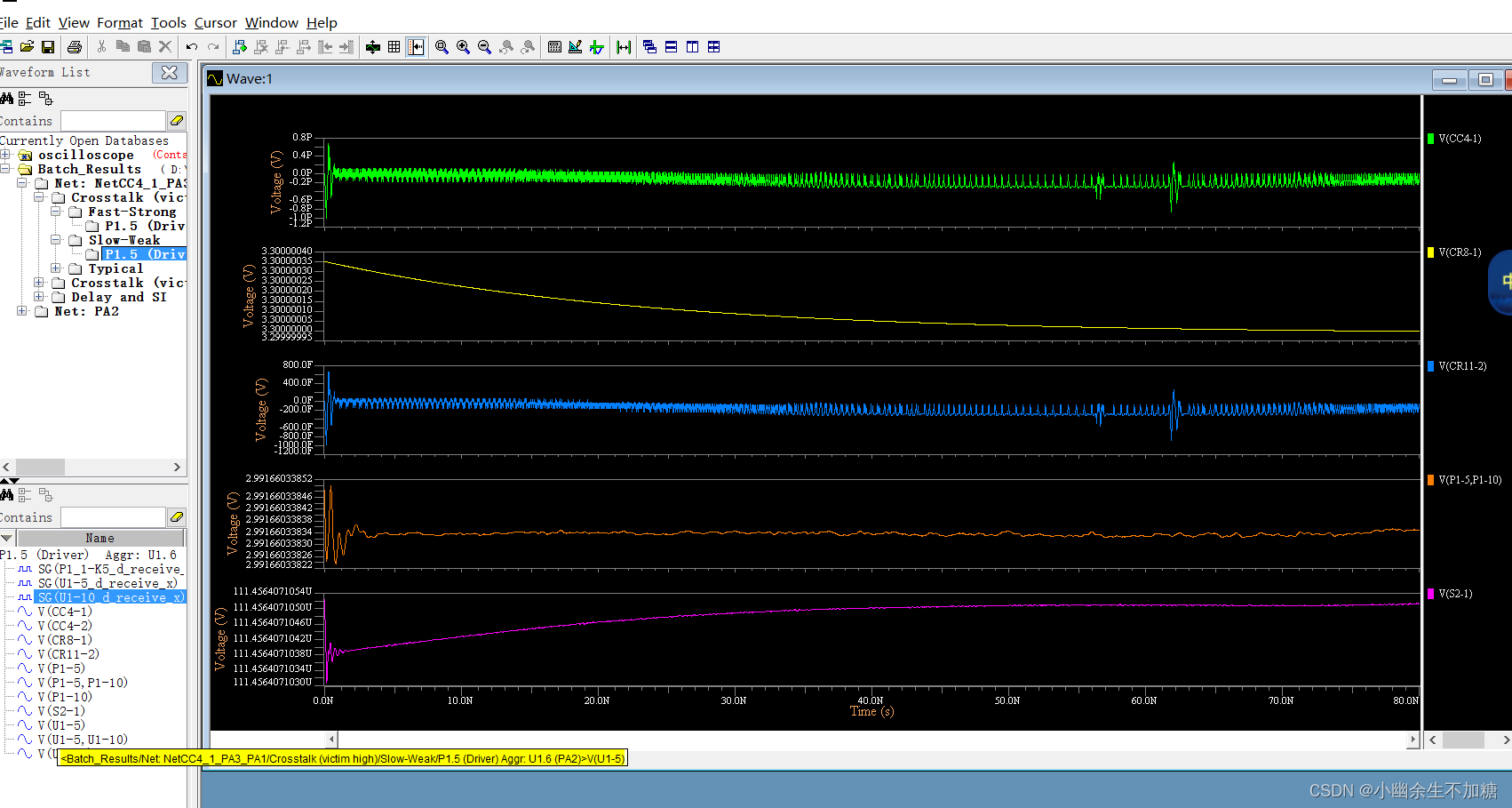

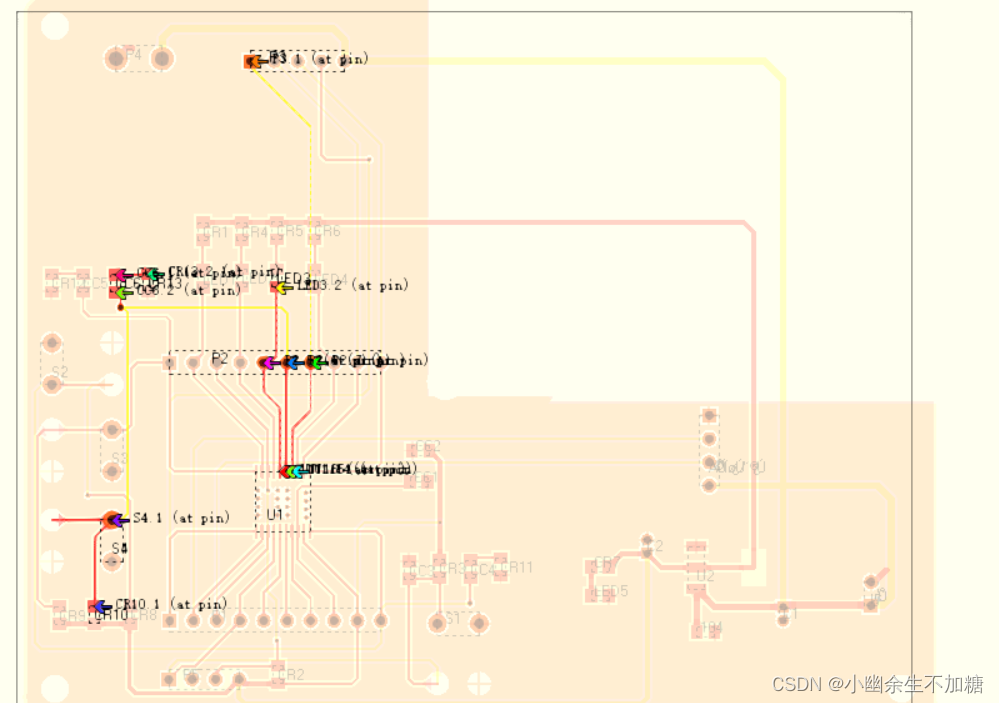

6.在BoardSim中的串扰仿真

前面介绍了几个关于串扰的实验,但都是在 LineSim 中进行的前仿真分析,那么对于已经设计好的PCB,该如何仿真呢?这是后仿真中必须面对的问题。不仅是单纯的串扰仿真,

对于DDRX、高速串行总线的信号完整性仿真也都会考虑是否需要加入串扰的影响。

BoardSim模块中考虑串扰与前仿真有一些不同之处:

第一,在工程中是否需要考虑串扰,如果需要,就要使串扰功能按钮处于使能状态;

第二,界定串扰的范围,如耦合长度及耦合间距等。

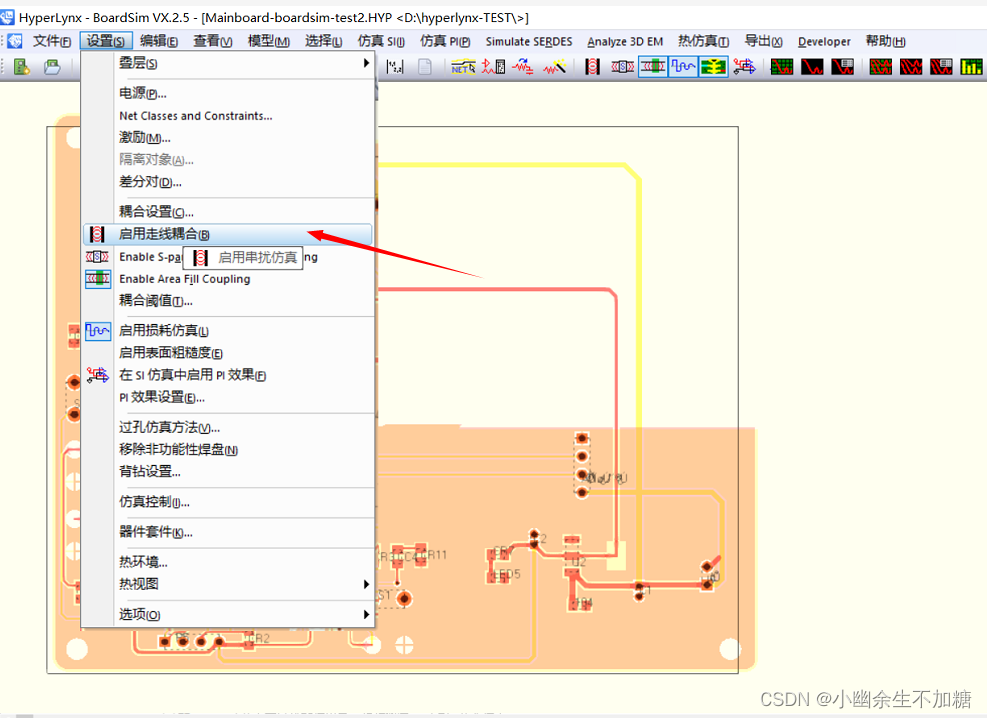

如果需要在仿真中启动串扰仿真,则在 BoardSim 的菜单栏选择设置(Setup)→启动串扰仿真(Enable Crosstalk Simulation)功能,或者在工具栏上单击按钮,如图所示。

前面介绍过,串扰是由于电磁耦合而存在的,但串扰影响的范围是有限的,有的串扰虽然存在,但并不一定会

对传输线或产品的功能有影响,所以当进行PCB 串扰仿真时,就需要考虑仿真的对象。那么,启动串扰仿真功能后,在图中,选择耦合阈值(Coupling Thresholds)设置,就会弹出如图所示的设置耦合阈值对话框。

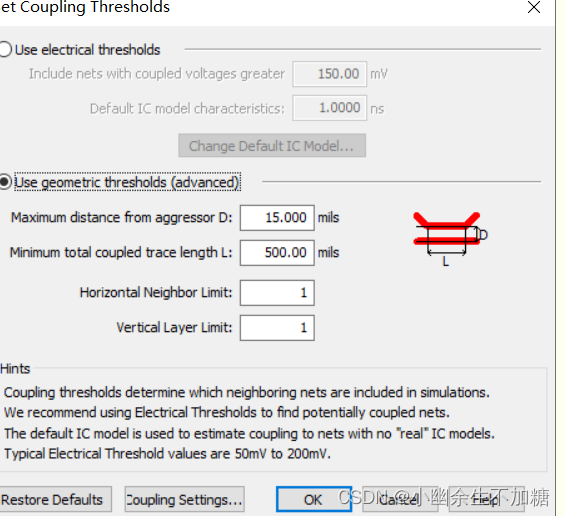

耦合阈值的设置有两种,一种是电气阈值(Use electrical thresholds),这是直接从串扰的大小的角度考虑串扰;另一种是几何结构阈值(Use geometric thresholds)这是从物理结构考虑串扰。前面介绍过,传输线之间的串扰与它们之间的距离和耦合长度有关系。

电气阈值主要是设置耦合电压,根据实际情况预估攻击端的电压是多少,例如,如果是 DDR3 信号线,攻击的电压是200mV,就设置为200mV。另外,芯片的参数设置是在耦合传输线没有模型的情况下使用的。

几何结构阈值主要是设置传输线耦合的距离和平行耦合的长度,在工程项目中常常使用这种结构的设置方式。

传输线距离攻击端的最大距离(Maximum distance from aggressor)表示把在设置的最大距离范围内的传输线都考虑在内,这只是仿真耦合串扰中的一个条件。通常设置的最大距离为所选择传输线网络线宽的3~5倍,距离再大,串扰的影响也会比较微弱。

最小耦合的长度(Minimum coupled segment length)表示软件认为是满足耦合条件的最小长度,小于设置的长度即不认为是耦合线,只要传输线上有一段满足,则会被选中。最小耦合长度一般根据信号的传输速率大小设置,速率越高,关注的长度越短。

在同一层上相邻网络的限制数(Horizontal Neighbor Limit):设置为1,即如果满足耦合长度和距离,则只有与选中网络相邻的传输线满足耦合传输线条件;设置为2,即如果满足耦合长度和距离,那么相隔一个网络之后的网络也会被选中。

层的限制数(Vertical Layer Limit)表示相邻层网络的选择,设置为1,即如果满足耦合长度和距离,则相邻一层的耦合线会被选中。

在同一层上相邻网络的限制数和层的限制数可以分别设置为0,设置为0的项表示仿真时不考虑对应层的影响,但不能同时设置为0,若同时设置为0,即使存在满足耦合长度和距离的传输线也不会被选中。

如图为线为5.2mil 传输线,最大距离设置为26mil、耦合长度为150mil、邻网络数为1、层设置为0。

设置完成之后可进行下一步仿真。

7.如何减小串扰

在高速、高密度的 PCB 设计中普遍存在串扰,而串扰对系统的影响一般都是负面的但串扰无法被彻底消除,那么就需要找到相应的优化或减小串扰的措施,在不影响系统设计成本和功能的情况下,使串扰尽量变小。

前面已经做过很多关于串扰的实验,当然还有很多关于串扰的研究,如传输线是否需要加防护地、使用变化较缓慢的上升/下降边沿等,结合实验结论及相关的工程实践经验,总结出减少串扰影响的常用方法主要有以下几类。

(1)在布线空间允许的情况下,尽量使传输线之间的距离增大,保证间距至少两倍于线宽,能使串扰减少很多。

(2)耦合传输线之间,平行布线的长度尽量短,保持在饱和长度以内。

(3)在布线的过程中,适时地改变布线间距,这也是一种减少平行布线距离的一种方式。

(4)在工艺允许的情况下,布线层尽量靠近参考层。

(5)在满足时序的情况下,尽量使用边沿变化缓慢的器件。

(6)相邻层都是布线层时,上下两层尽量垂直布线,如果有平行布线,也要尽可能短。

(7)高速信号,当传输距离比较长时,尽量布线到内层,以减少远端串扰,进而减少串扰的总和:传输距离较短时,可以布线在外层。

(8)传输链路的阻抗尽量匹配好,可以同时减少远端和近端串扰。

(9)在空间足够大时,可以考虑给高速信号线加防护地,防护地上一定要加适当的地孔减少串扰的方式有很多,但在工程中一定不要单纯地只考虑串扰,还应该综合考虑各方面的因素。