1.DDR简介

2.DDR仿真概述

3.DDR数据仿真前的数据验证

4.DDR数据仿真具体步骤

1.DDR简介

DDR(双倍速率同步动态随机存储器)是一个内存名称,意思即双倍速率同步动态随机存储器,是内存的其中一种。

DDR 总线是由 SDRAM 发展而来的一种并行总线。

SDRAM在一个时钟周期内只传输一次数据,它是在时钟的上升期进行数据传输;而DDR内存则是一个时钟周期内传输两次数据,它能够在时钟的上升期和下降期各传输一次数据,因此称为双倍速率同步动态随机存储器。DDR内存可以在与SDRAM相同的总线频率下达到更高的数据传输率。

DDR内存的频率可以用工作频率和等效频率两种方式表示,工作频率是内存颗粒实际的工作频率,但是由于DDR内存可以在脉冲的上升和下降沿都传输数据,因此传输数据的等效频率是工作频率的两倍。

DDR 总线规范由JEDEC(Joint Elec- tron Device Engineering Council)组织制定并发布,其官方网站是:www.jedec.org。

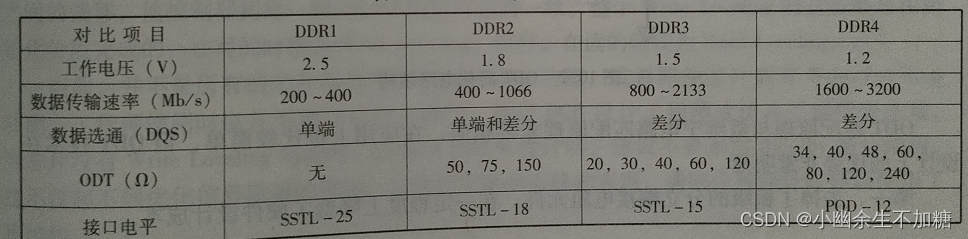

从第一代的 DDR1,经历了 DDR2 和DDR3,发展到目前的第四代 DDR4,由于一些移动端设备或对低电压和低功耗有要求的设备的需求,还发布了 LPDDR2和LPDDR3等低功耗产品。DDRx线伴子技术发展而发展的,也是由于DRx电子产品数据交换的“中转站”的功能而决定的。

DDRx线率提升和供电电压的降低。最初的 DDR1据最大速率只能达到400Mb/s,到当前DDR4 的最大速率可以达到3.2Gb/s;DDR1的供电电压为2.5V,常规的DDR4的供电电压只有1.2V。其实 DDRx总线每一代的升级不仅是数据传输速率的提升及电源电压的降低,还包含很多方面技术的提升和改变,如端接电阻 ODT 的应用、数据预取技术的发展和应用等。

如图所示为几种主流的DDRx参数对比数据。

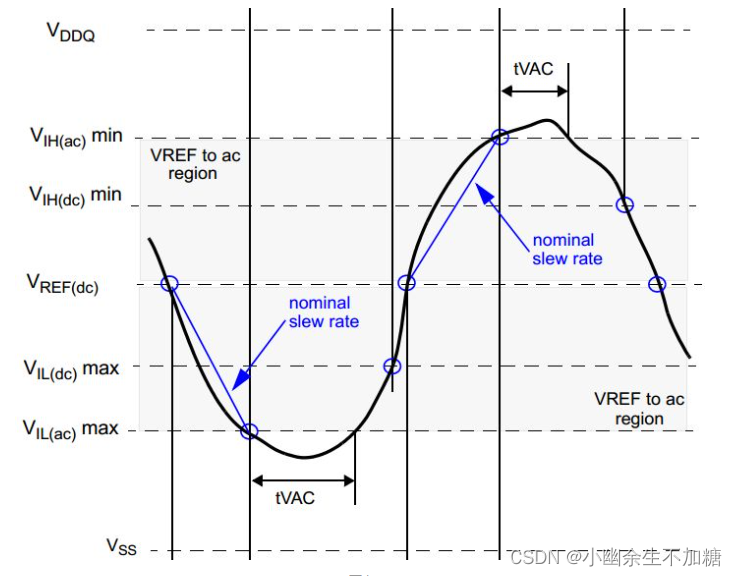

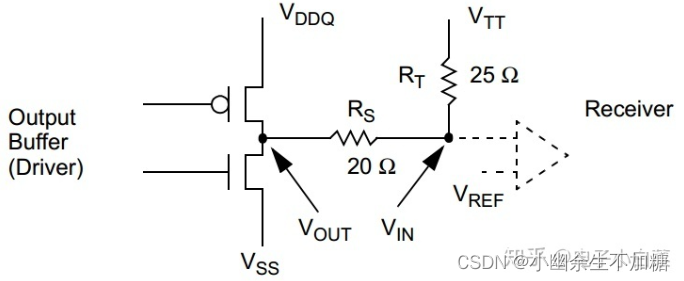

(1) SSTL电平

LVTTL电平为单端信号,而SSTL电平本质上是差分对,其实现机制是将信号与参考电平Vref组成差分对进行比较,如图所示,VIH和VIL各有一个交流参数AC和直流参数DC,信号第一次越过AC门限的时刻,作为时序计算的参考点,此后只要信号保持DC门限内,逻辑状态保持不变,这种设计减小了噪声、振铃等对于信号质量的影响。在SSTL_18中,规定了端接电阻上拉到VTT电源,如图所示。在典型应用中,VREF和VTT等于VDDQ/2,因此接收端的电压同时取决于驱动器、端接电阻RT和端接电压VTT,驱动器的输出电阻Ron一般不会大于21R。这个端接电阻最主要的作用是提高信号完整性,特别是在一驱多的Fly-by拓扑中,此外还能增强驱动能力,当DDR颗粒较少时(1颗或2颗时,可咨询DDR原厂确定),VTT可以不用。另外,当驱动端电平分别为高或低时,电流流向相反,因此VTT电源需要具有提供电流和吸收电流的能力,不能使用普通的电源。

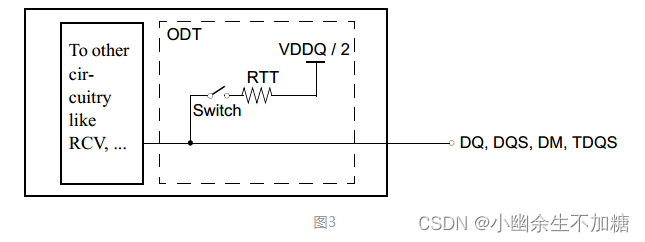

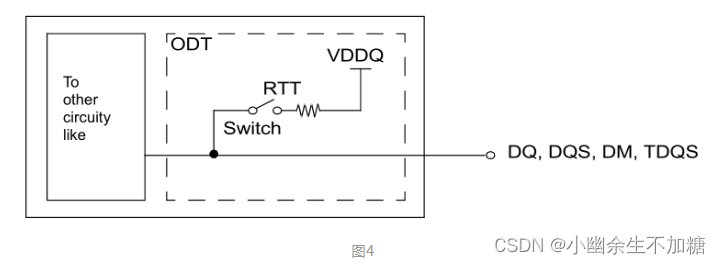

(2) POD电平

POD是伪漏极开路电平,其内部端接上拉到VDDQ,而SSTL内部是上拉到VDDQ/2,分别如图3和图4所示。因此,当驱动端输出高电平时,由于驱动端和接收端端接电压均为VDDQ,因此没有电流流动,降低了功耗;驱动端输出低电平时,POD由于上拉电压高,功耗稍大于SSTL。正因此,DDR4多了一个DBI功能,即数据总线翻转,当一个字节里0的位数大于1的位数时,可以将0和1反转,以降低功耗。

由于POD的参考电平Vref大小会随着驱动强度、负载、传输线特性等不同而改变,因此DDR4数据信号的参考电平VrefDQ是由芯片内部自己产生的,没有外接该电平的管脚,只有地址信号的参考电平管脚VrefCA。POD的VrefDQ通过控制寄存器设置值由芯片自行优化调整,称为VrefDQ Training。

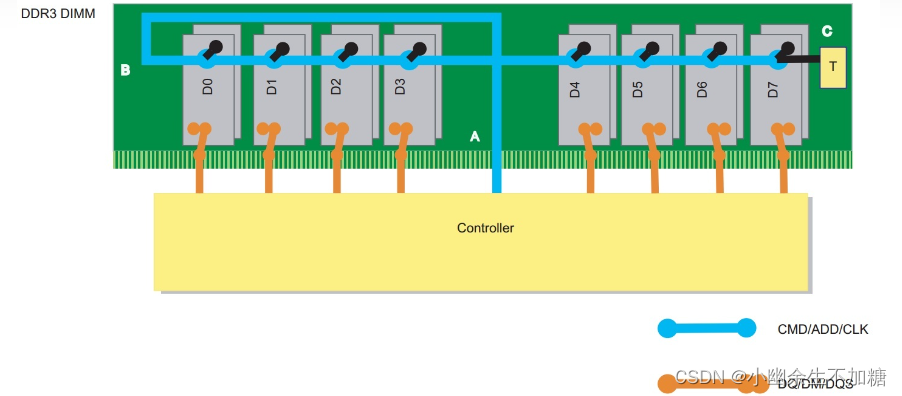

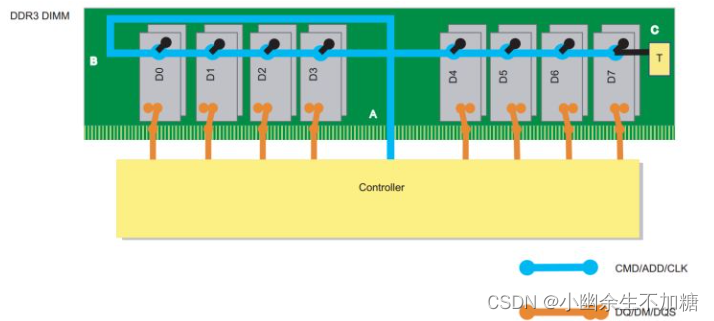

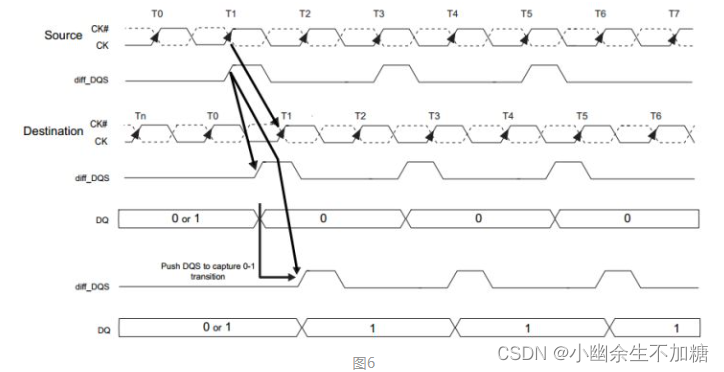

(3)Writing Leveling

为了更好的信号完整性,DDR3内存模块对命令、地址、控制和时钟信号线采用了fly-by拓扑结构(一种特殊的菊花链),如图所示。该拓扑结构能够减小stub的数量和长度,但同时也会引起各内存颗粒CLK和DQS信号之间的飞行时间偏差,因此,DDR3颗粒引入了Writing Leveling功能,如果DDR控制器同时也支持该功能的话(并非所有控制器都支持该功能),就可以补偿CLK和DQS之间的飞行时间偏差。Write Leveling的本质目的是使DQS信号的上升沿在到达DDR颗粒时能够和CLK时钟信号对齐。DDR控制器通过不断地调整DQS的发送延时,DDR颗粒则在DQS信号的上升沿采样CLK时钟信号,并通过DQ数据信号将CLK时钟状态反馈回给DDR控制器,直到DQ信号从0变成1,此时就使CLK和DQS对齐了,确定DQS延时值,完成调整过程,如图所示。

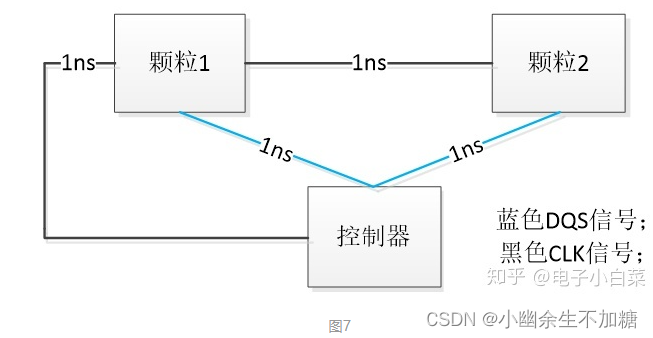

上述调整过程的文字描述可能不是很直观,下面通过一个简单的例子来说明,如图7所示,颗粒1的CLK飞行时间为1ns,颗粒2的CLK飞行时间为2ns,颗粒1和颗粒2的DQS飞行时间均为1ns。如果不进行Write Leveling调整,颗粒2的CLK信号和DQS信号的飞行时间偏差为1ns,没有对齐。经过调整后,控制器在发送颗粒1的DQS后,延时1ns再发送颗粒2的DQS,则颗粒1在1ns后收到对齐的DQS和CLK,颗粒2在2ns后收到对齐的DQS和CLK,从而满足了时序关系。

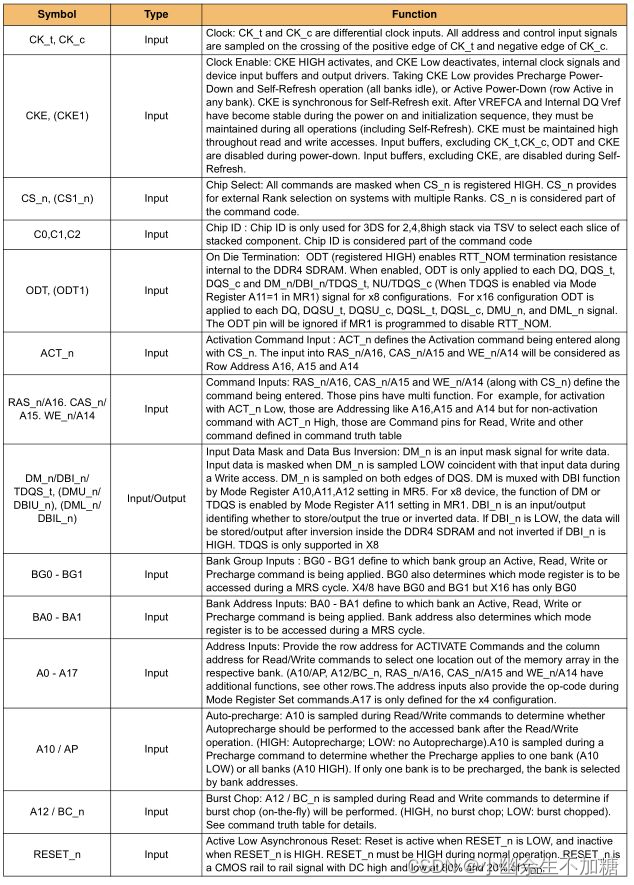

(4)DDRx引脚说明

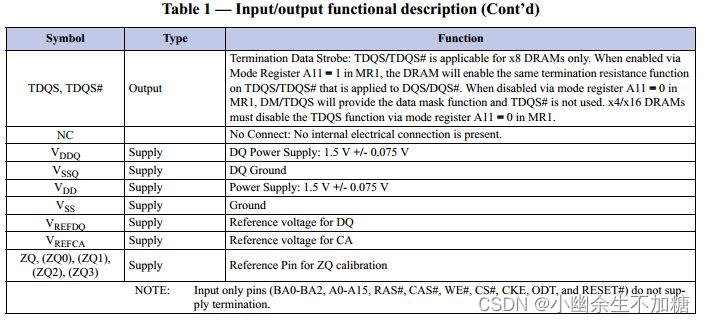

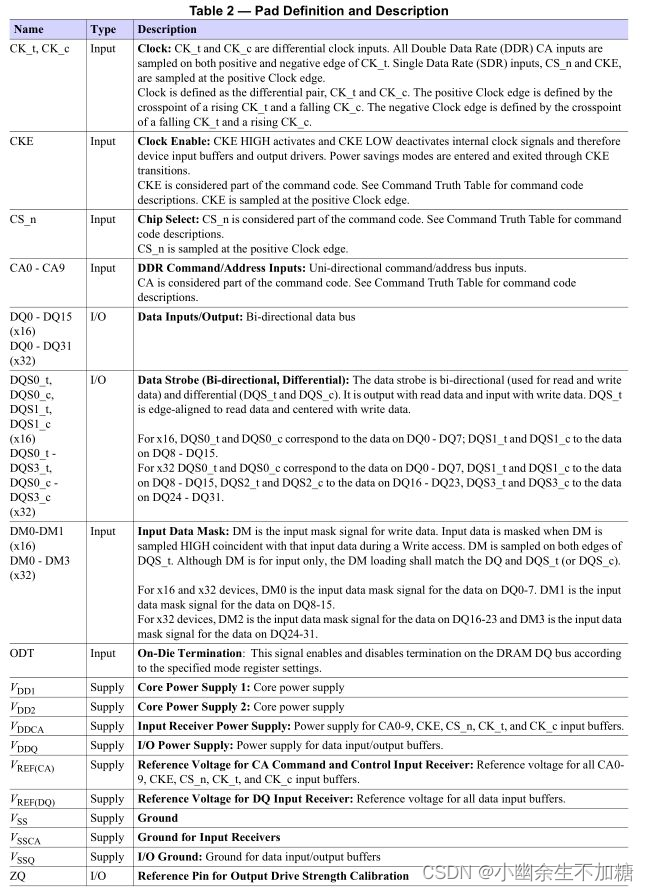

DDRx是典型的源同步时钟(另一种时钟系统是共同时钟),其信号引脚主要有差分时钟CK/CK#、时钟使能CKE、片选CS#、行地址选通RAS#、列地址选通CAS#、写使能WE#、BANK地址选通BA0-BAn、地址A0-An、数据DQ0~DQn、数据选通DQS/DQS#、数据掩码DM。不同一代的DDR/DDR2/DDR3的引脚有所不同,以下几幅图分别是DDR3,LPDDR3和DDR4的引脚说明。

除了上述引脚,DDR3引入了新的引脚,RESET#复位引脚在正常运行时必须是高电平。ZQ引脚必须接一个 240 欧姆的1%高精度电阻到GND,该电阻的作用是校准内部ODT电阻值和DDR导通电阻值Ron,因为内部的电阻会随着温度而发生变化,需要校准才能保证准确的终端匹配。

DDR3的参考电压也分为2个,分别是数据信号的VREFDQ和地址控制信号的VREFCA。

2.DDR仿真概述

随着处理器和传输速率的不断增加,时序和信号完整性要求变得越来越难以满足。HyperLynx的DDR技术套件使硬件工程师能够快速地开发出DDR内存子系统的解空间,在负载电流最低和最高的路由约束之间权衡,以满足信号在JEDEC的DDR规格下的完整性和时序要求。

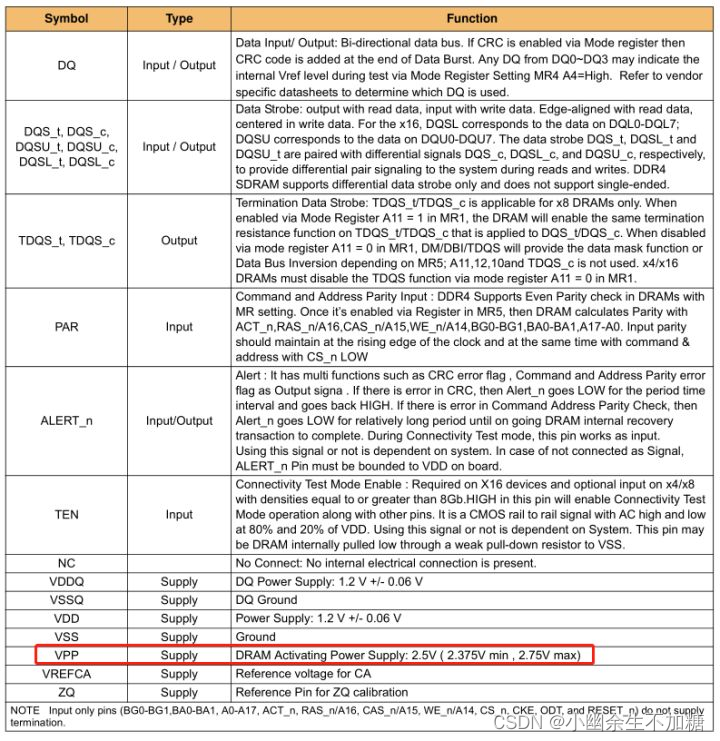

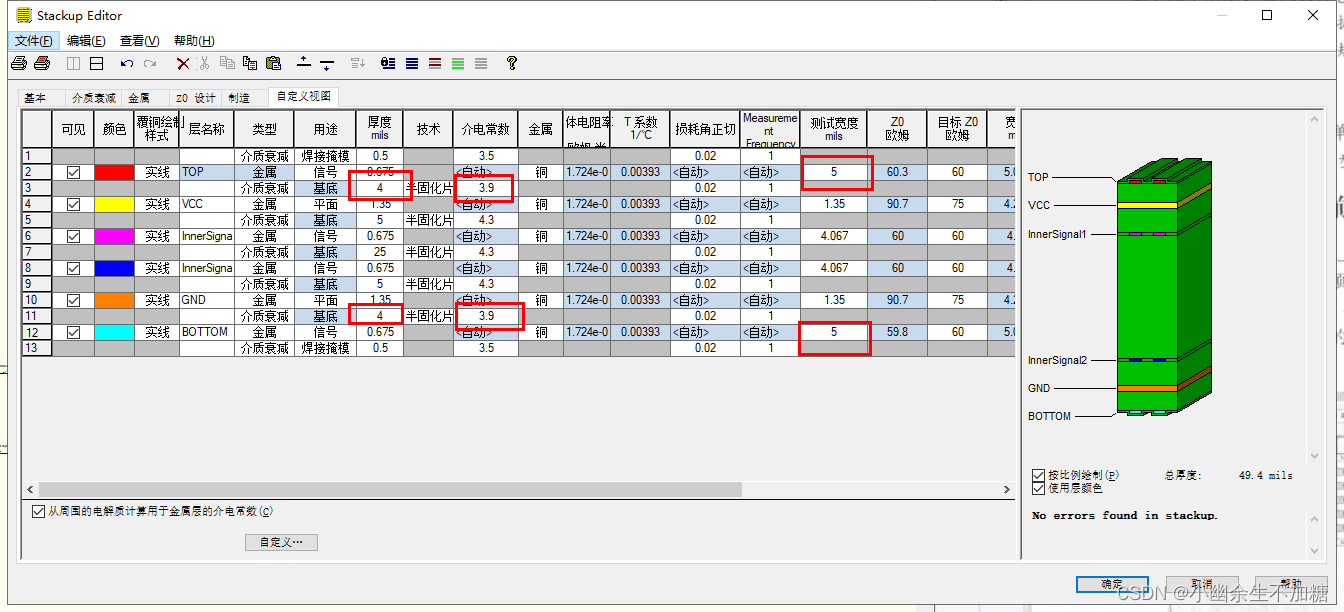

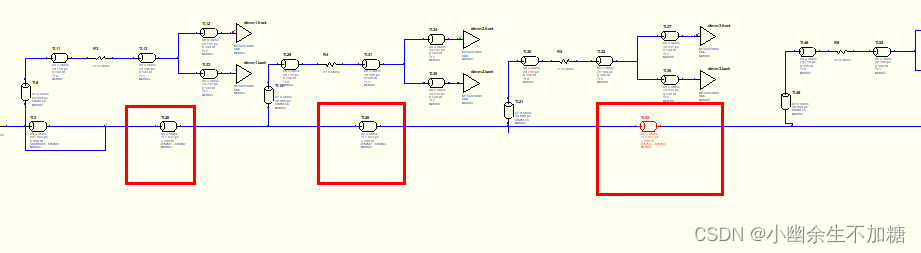

HyperLynx的DDR设计套件包含4个DIMM模拟布局,分别位于DDR的地址和数据接口LineSim上。它采用了Xilinx公司的带有MicoMT46V16M8A0SDRAM组件的Virtex-4控制器,界面可以运行多种速度的DDR,但本节主要研究DDR266MBS型的数据总线设计,其仿真电路如图所示:

如上图中所示,布局具体包括以下元素:

(1)带有净长度的DIMM数据网布局是由JEDEC规范定义的(独立的LineSimFFS文件已

被创建,其中包含两个规范所允许的最小和最大长度);

(2)上拉电阻;

(3)串联电阻;

(4)Xilinx指引控制器的简单封装模型:

(5)互连长度要符合一个典型的印制电路板要求。

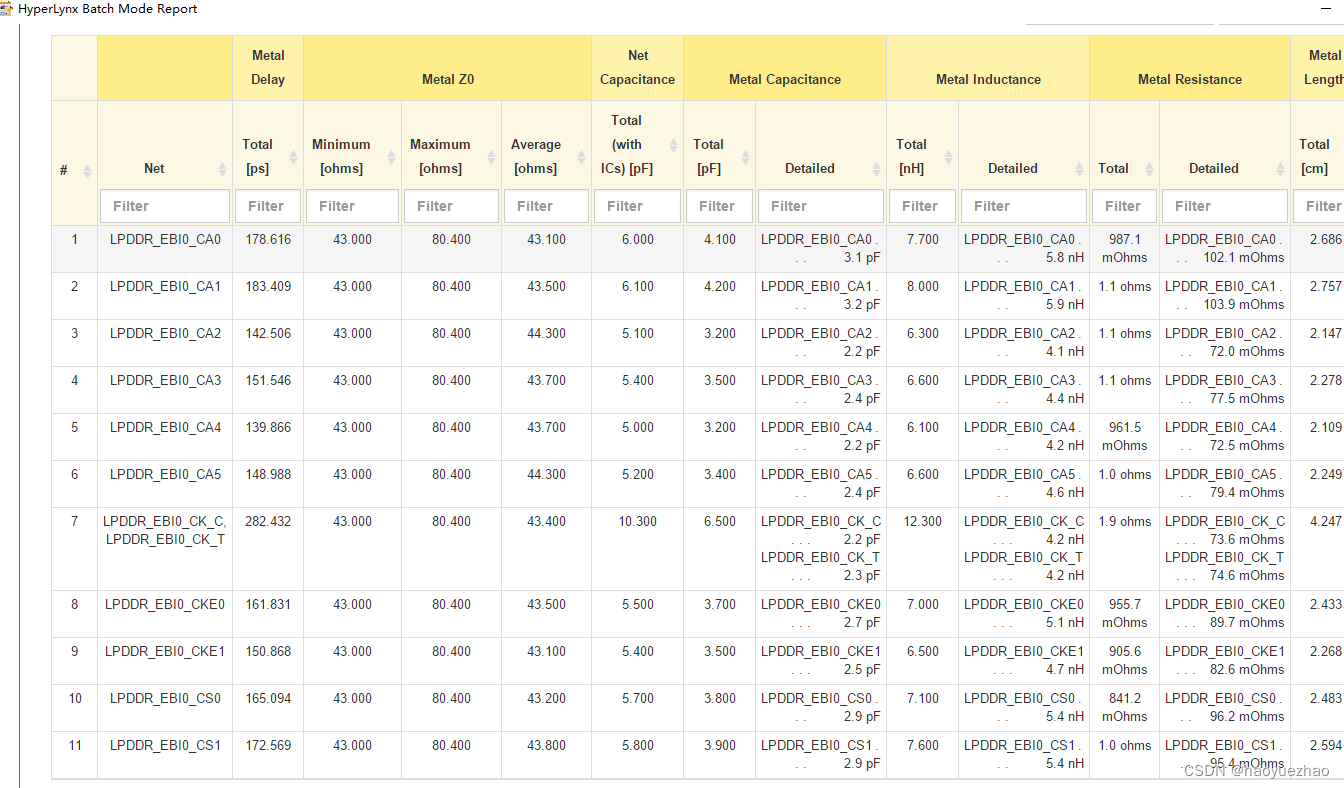

3.DDR数据仿真前的数据验证

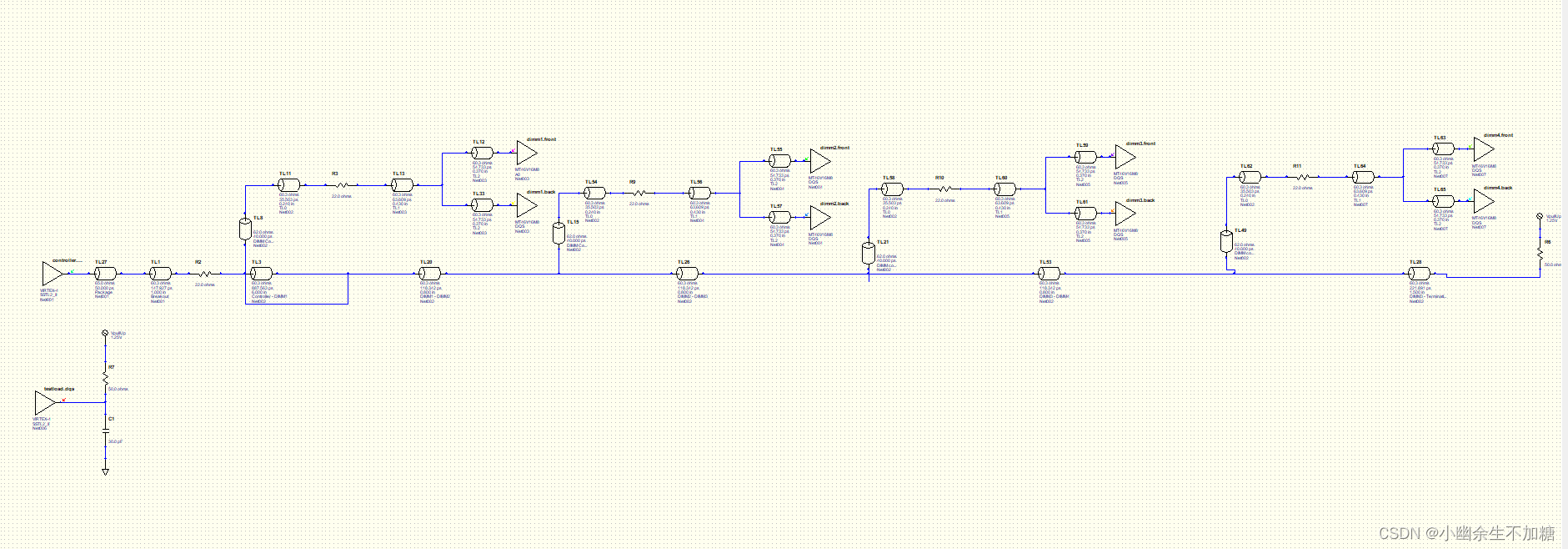

打开文件目录中的“DDR_4DIMM_data_min.ffs”,验证下列项目。

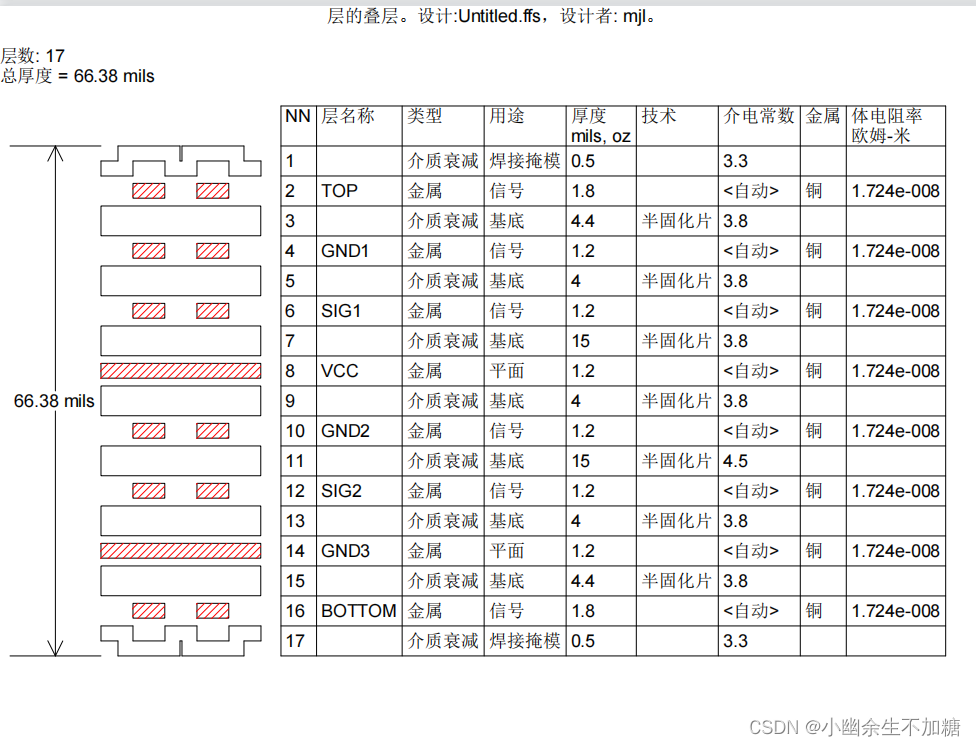

(1)打开叠层编辑器,顶层和底层设置线宽为5mil,介质厚度从上到下分别设置为4mil。

(2)顶部和底部电介质的介电常数设置为3.9,完成后关闭叠层编辑器。叠层设置如图所示。

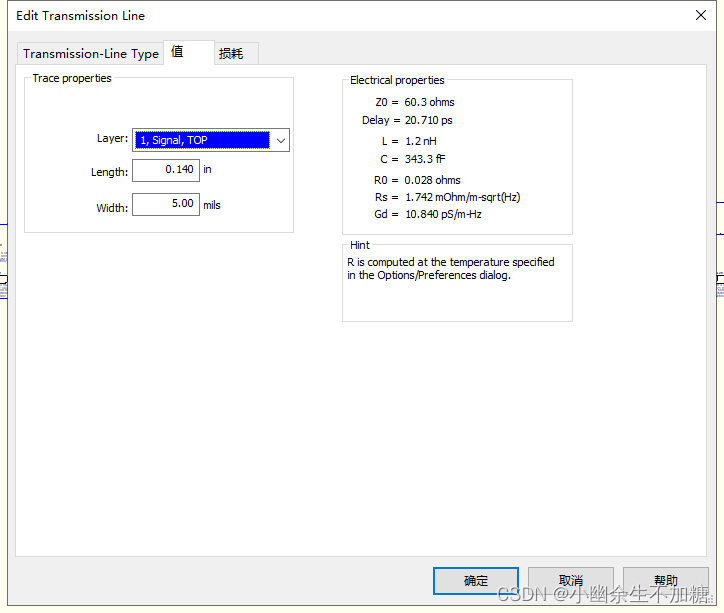

(3)线长由传输线标志来表示,线宽都是5.0mil,并且所有传输线都应在顶部信号层上,如图所示。

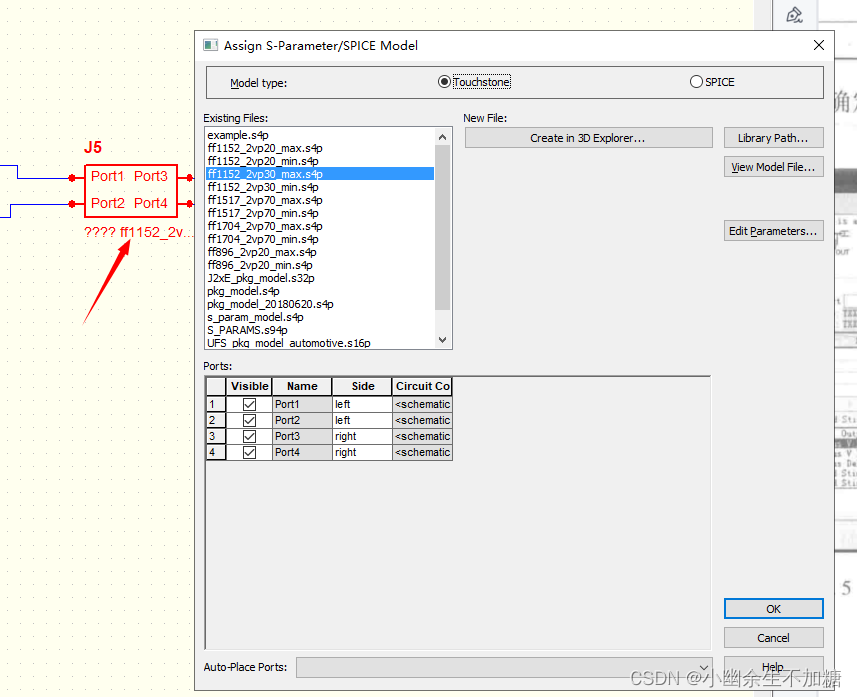

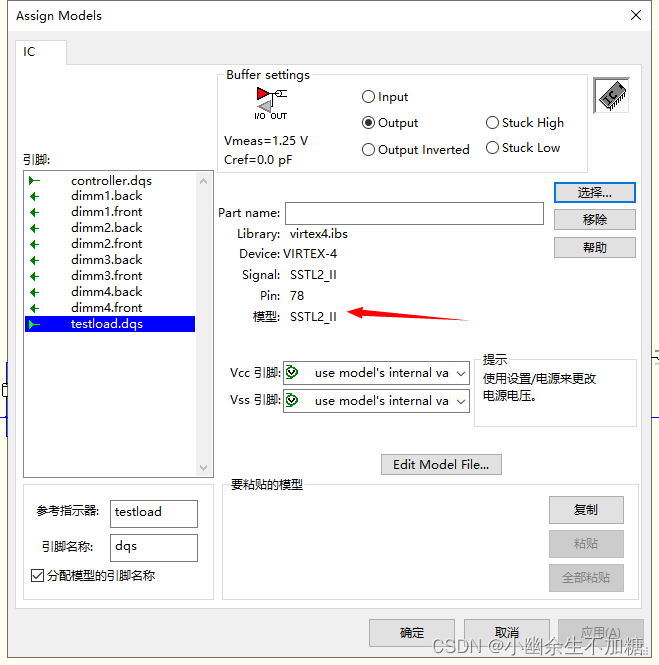

(4)检查“virtex4.ibs”是否用到con- troller.dqs和testload.dqs。信号SSTL2_II应从模型内选择,如图所示。

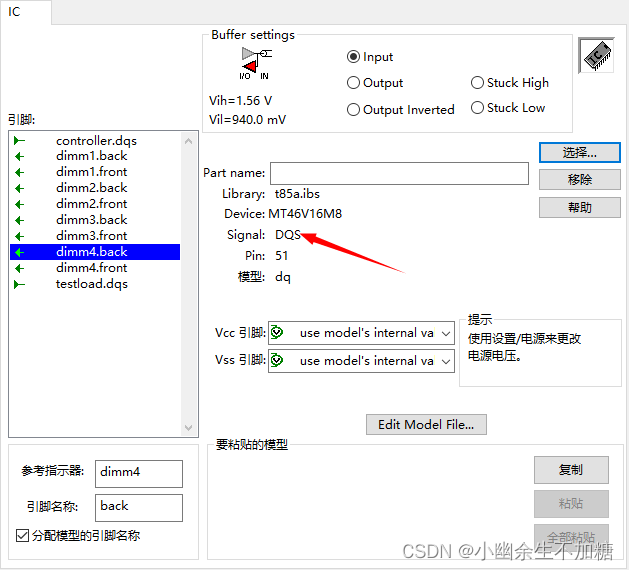

(5)确认“t85a.ibs”适用于所有的 SDRAM元件:DIMM[1-4][front,back]。 DOS信号也应从模型内选择,如图所示:

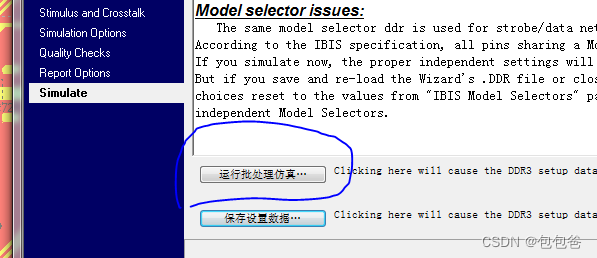

4.DDR数据仿真具体步骤

DDR数据总线可以在任何组件驱动拓扑结构中驱动,其中可以有很多复杂的操作。本节中,我们值研究当Virtex-4单独驱动时的信号质量。

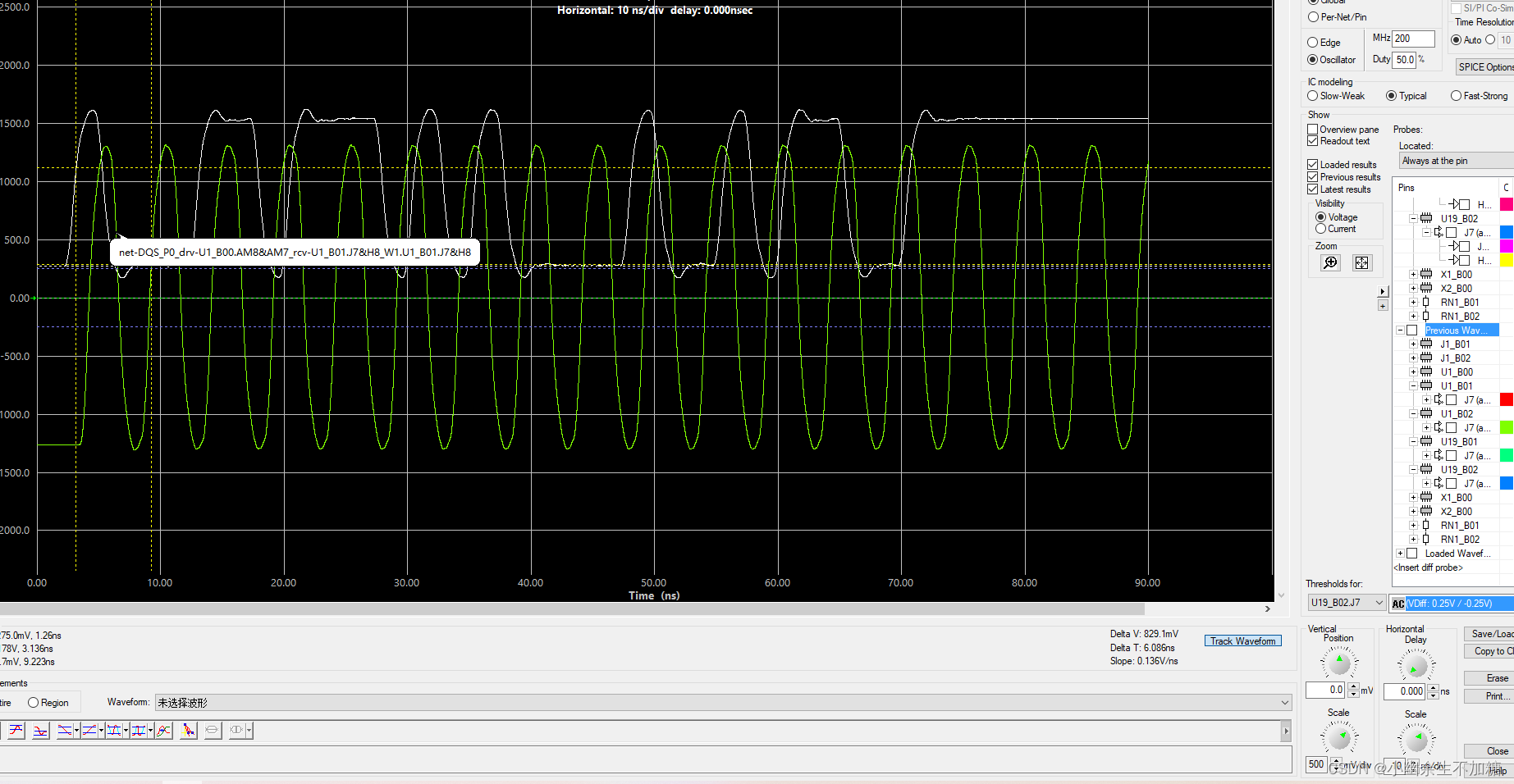

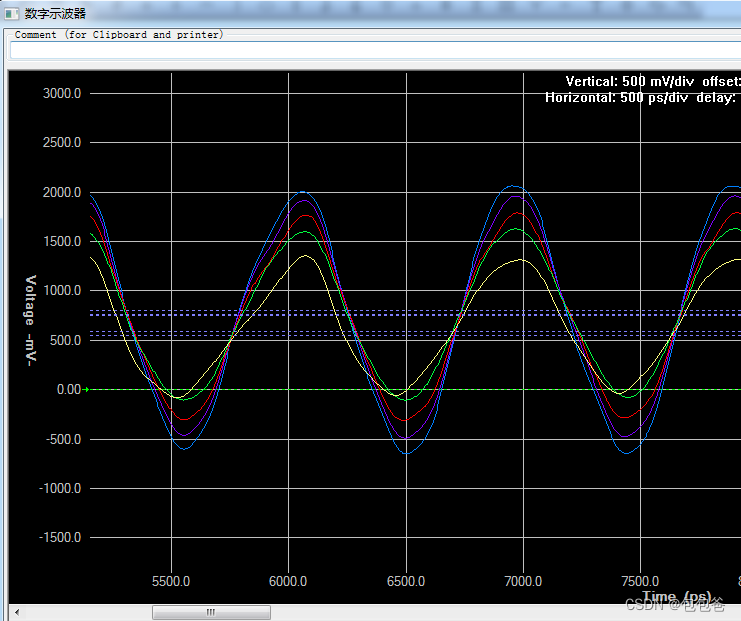

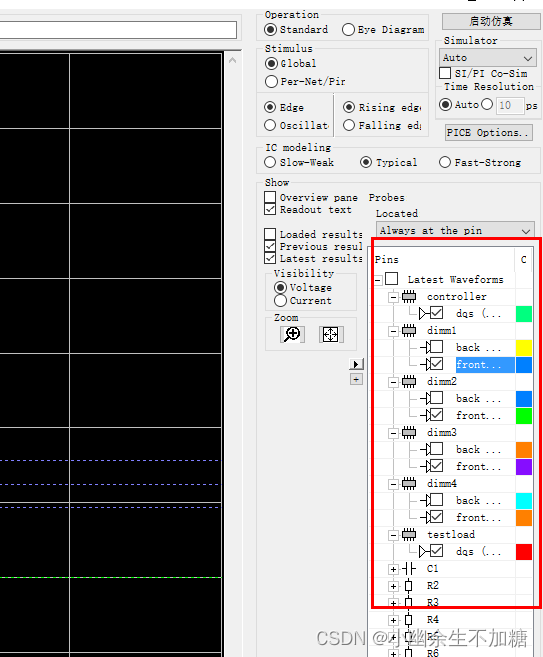

(1)打开示波器,进行总线设计的仿真。

(2)选择附加探针按钮,如图所示,并用探针添加以下引脚:

controller.dqs

dimml.front

dimm2.front

dimm3.front

dimm4.front

Testload.dqs

(3)单击“确定”按钮退出,回到示波器探针对话框。

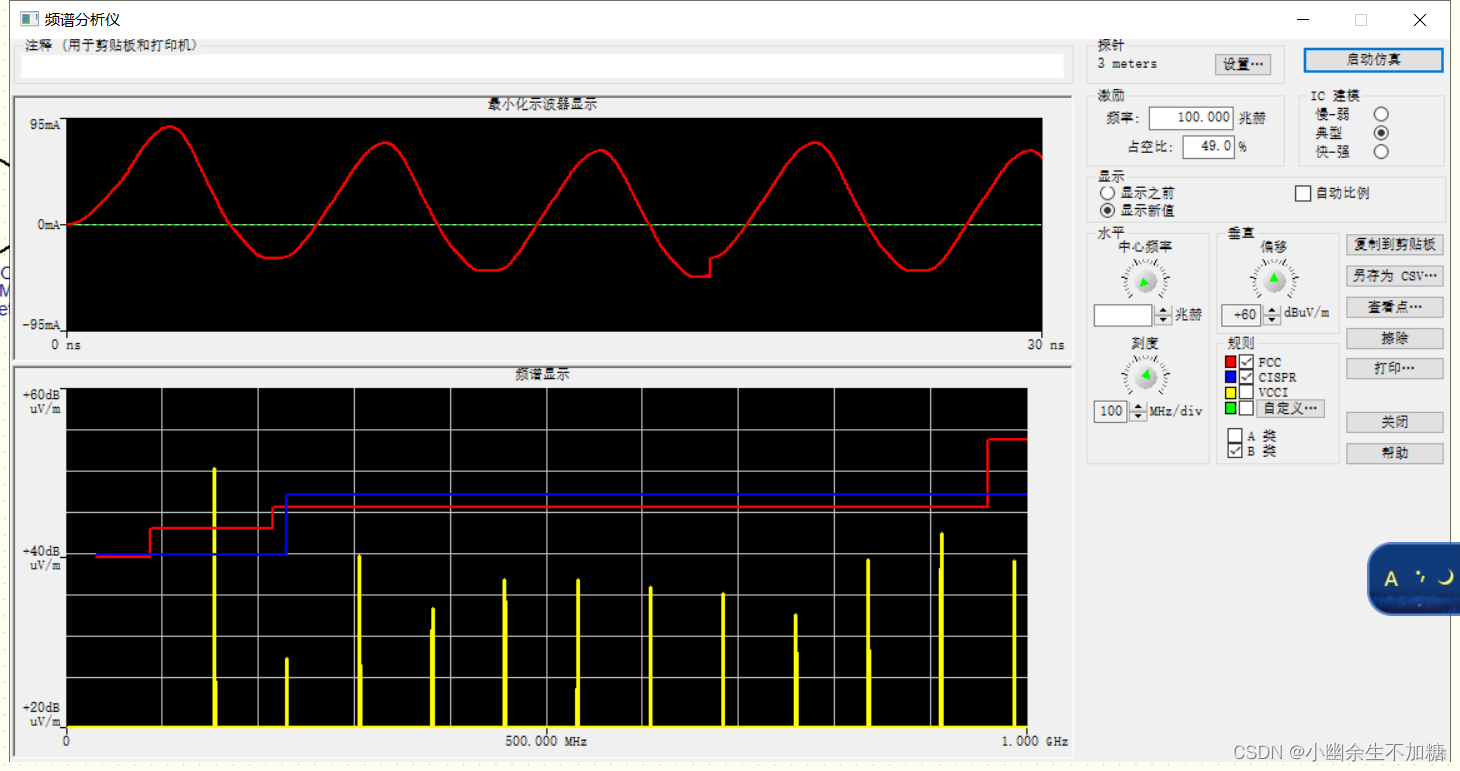

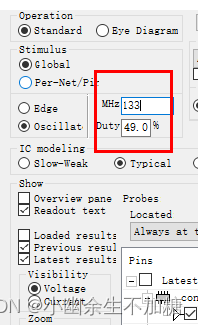

(4)在示波器中选择振荡器,并设置49%的占空比,频率为133MHz。

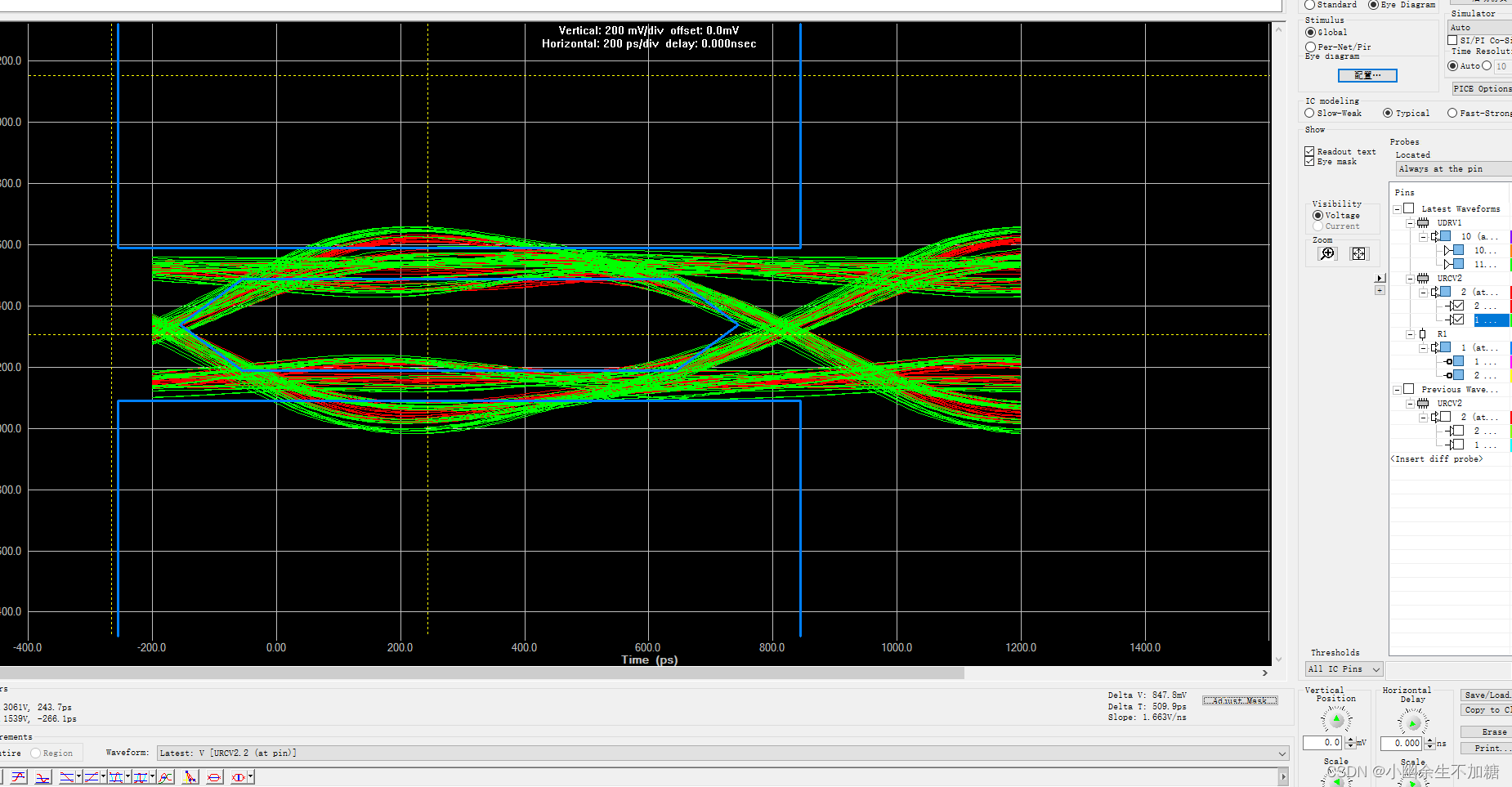

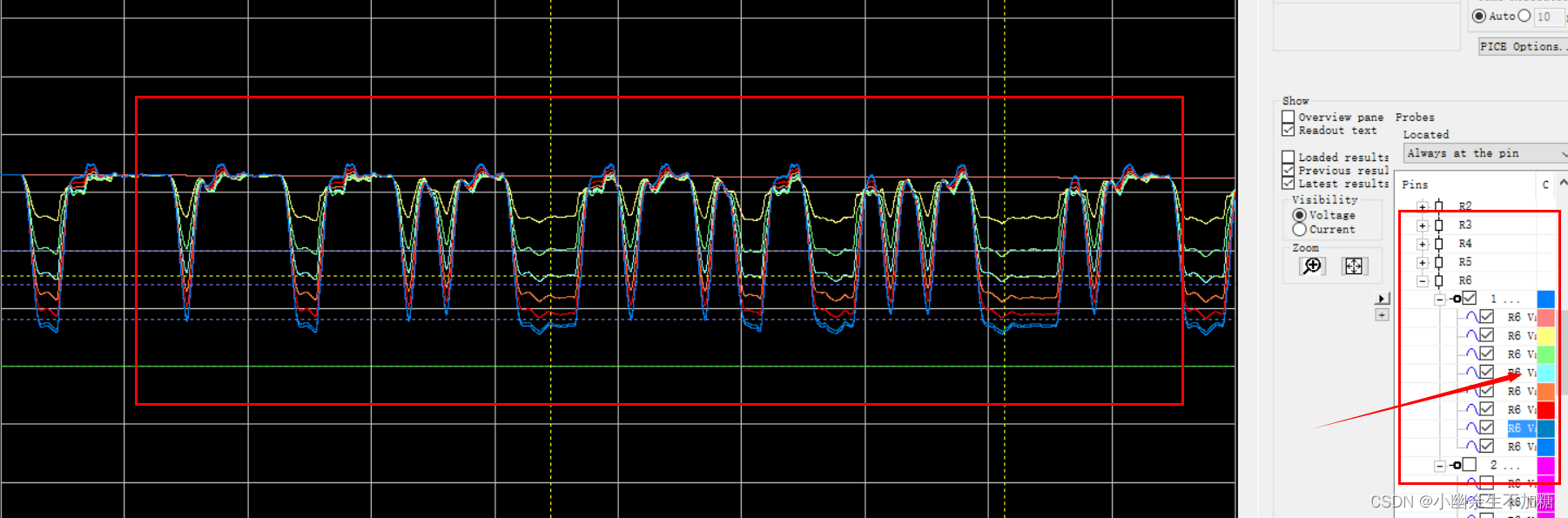

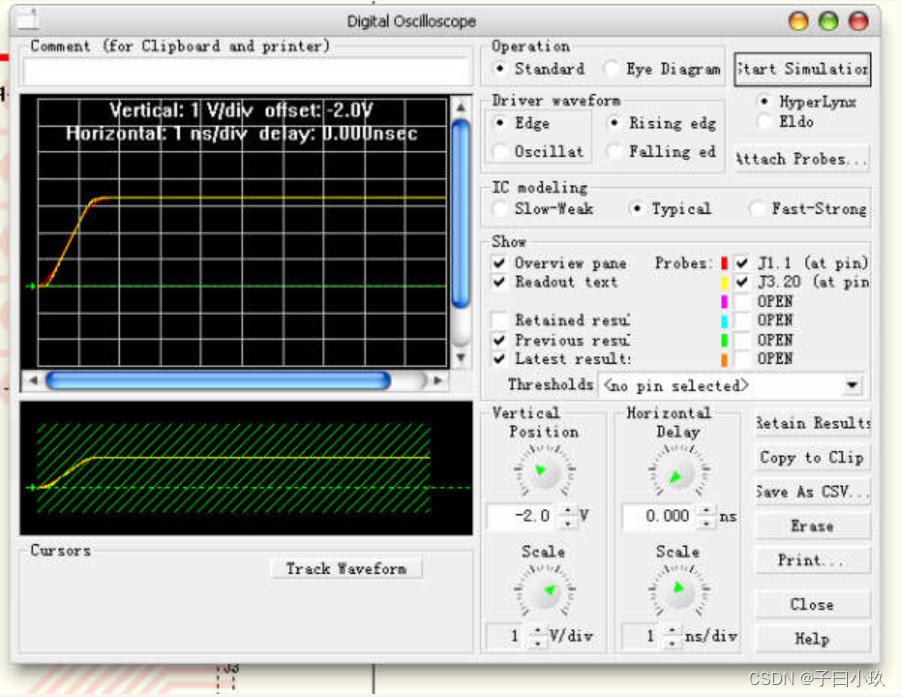

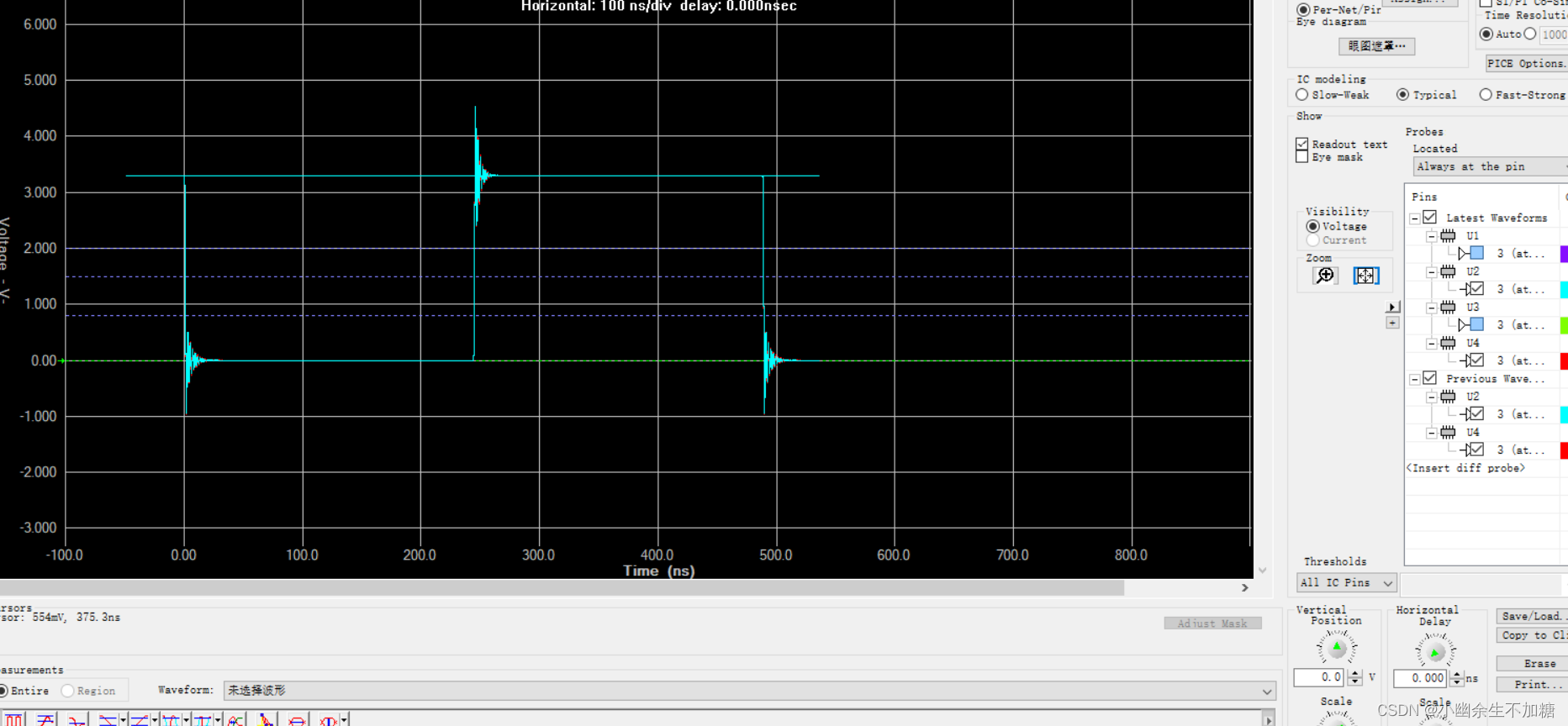

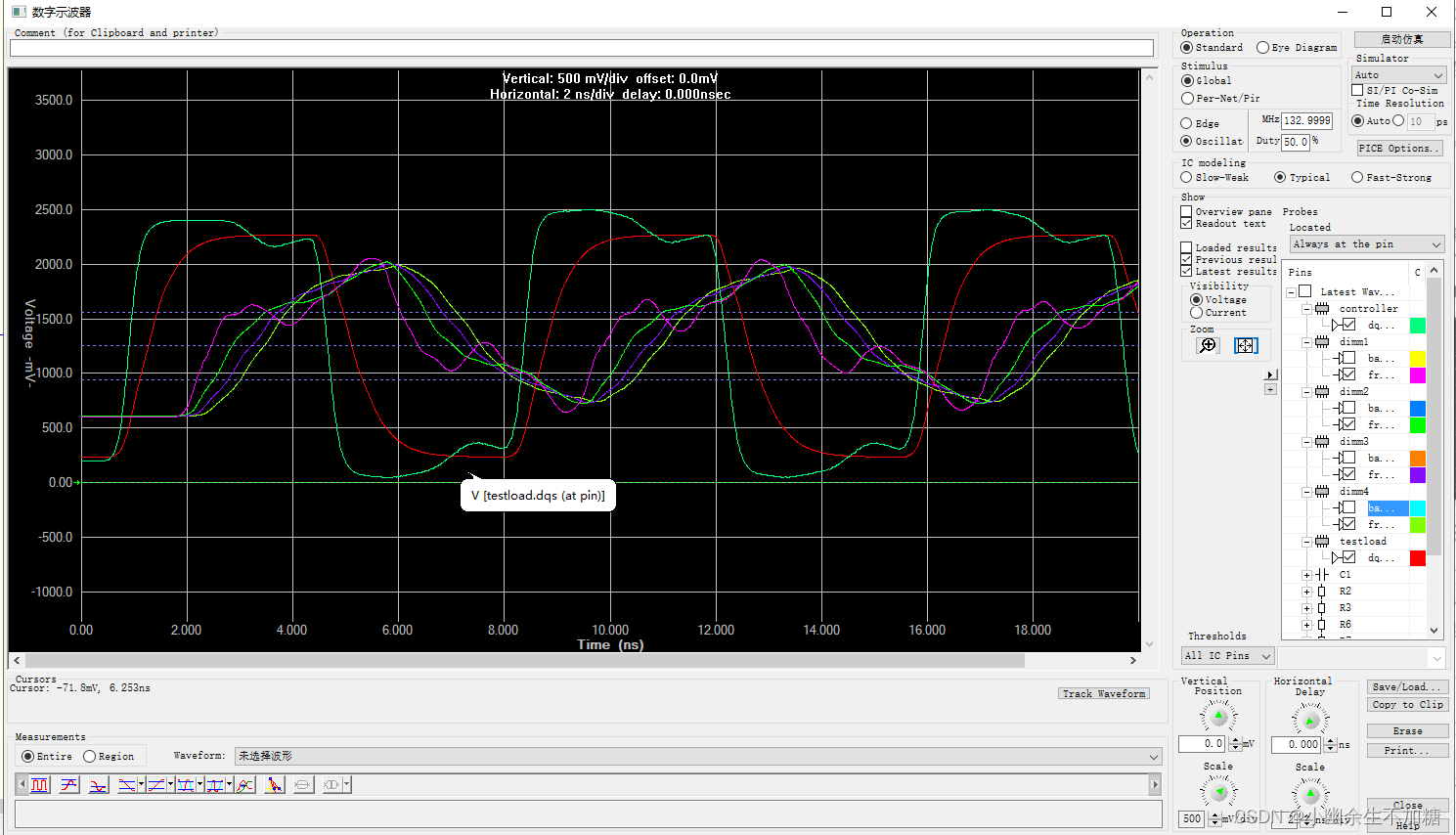

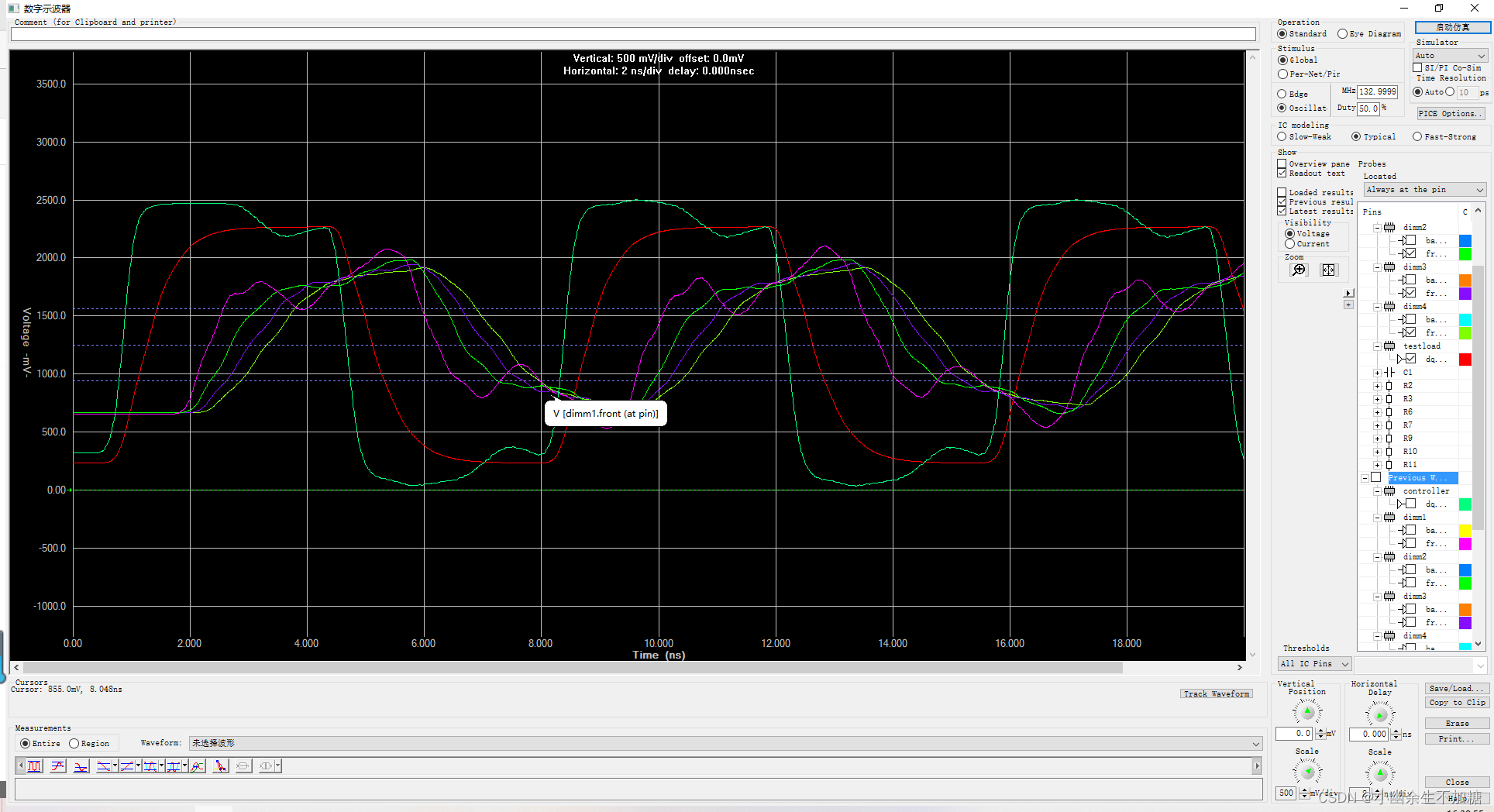

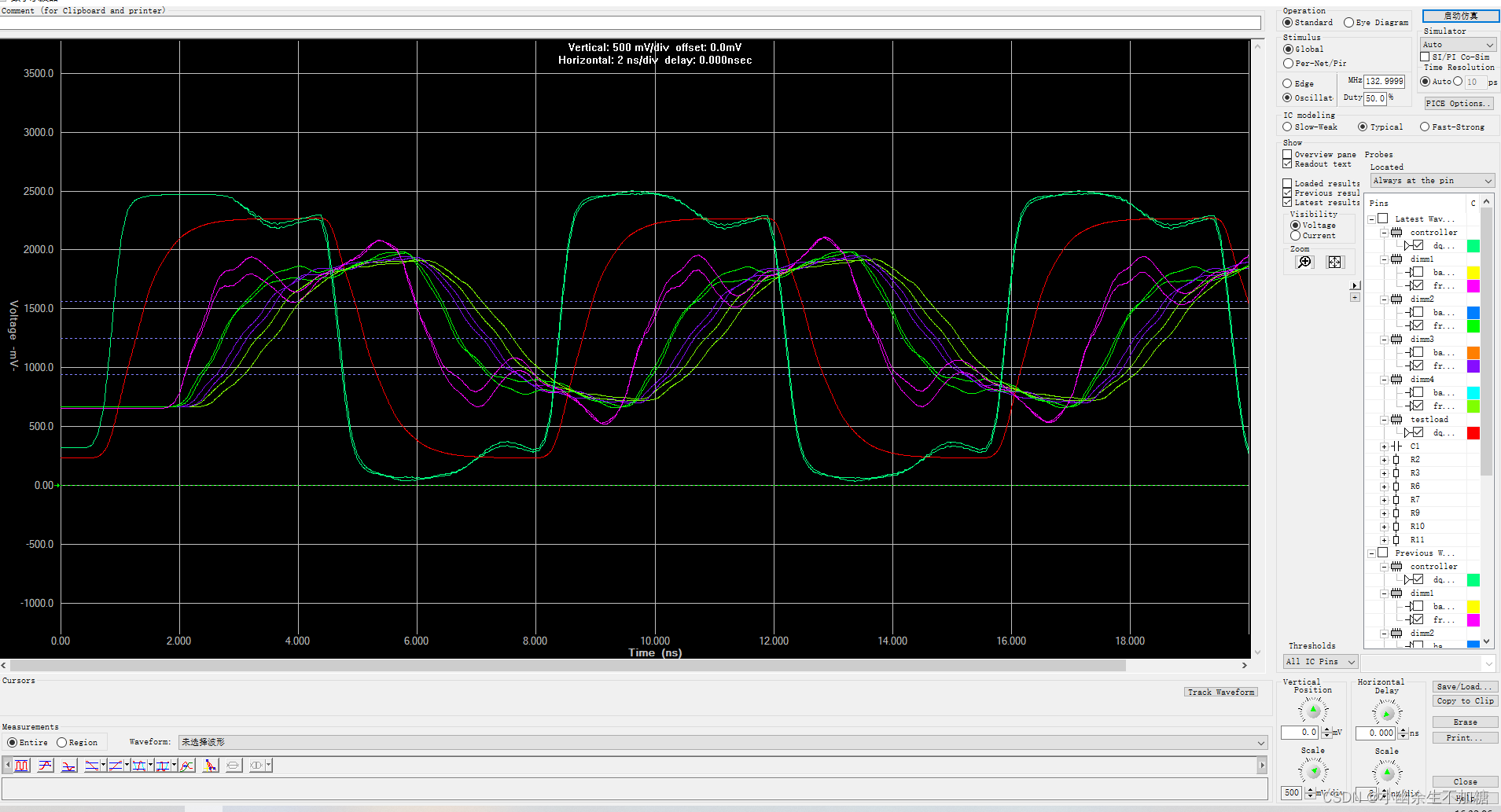

(5)单击开始仿真按钮,并查看结果,如图所示。

(6)设置水平标尺为2ns/div,垂直刻度为500mV/div。如果有必要,可以通过多次仿真,得到一个更加真实的结果。

从图中可以看出,和testload相关的DIMM1信号相对稳定,上升沿约为2.85ns。测量方法是从2.0V(VMEAS)“testloaddas”到2.04V(VIH)“dimml.front”为了增加时序余量,我们需要改变相应选项,从切换区域移除这一影响。

下面,我们将尝试改变一些端接电阻,以提高信号质量。

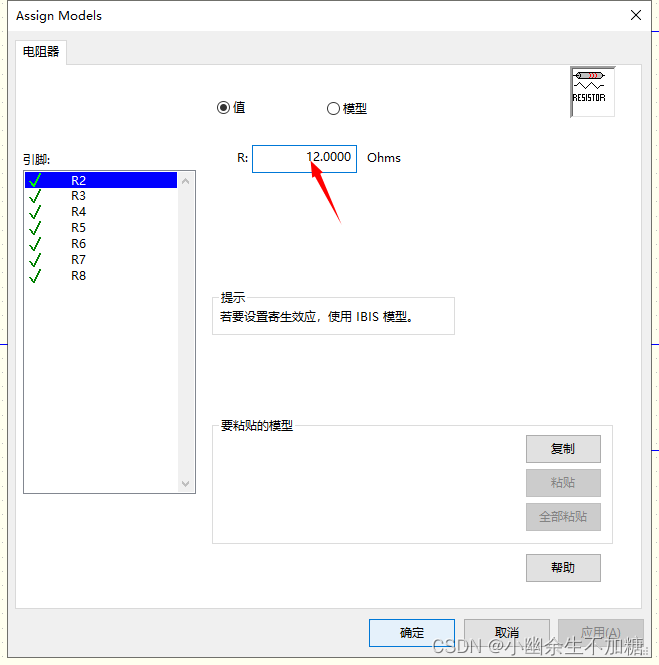

(7)在LineSim原理图编辑器中,双击位于驱动器右端的R2端接电阻。

(8)把电阻阻值改为12Ω,单击“确定”按钮,如图所示:

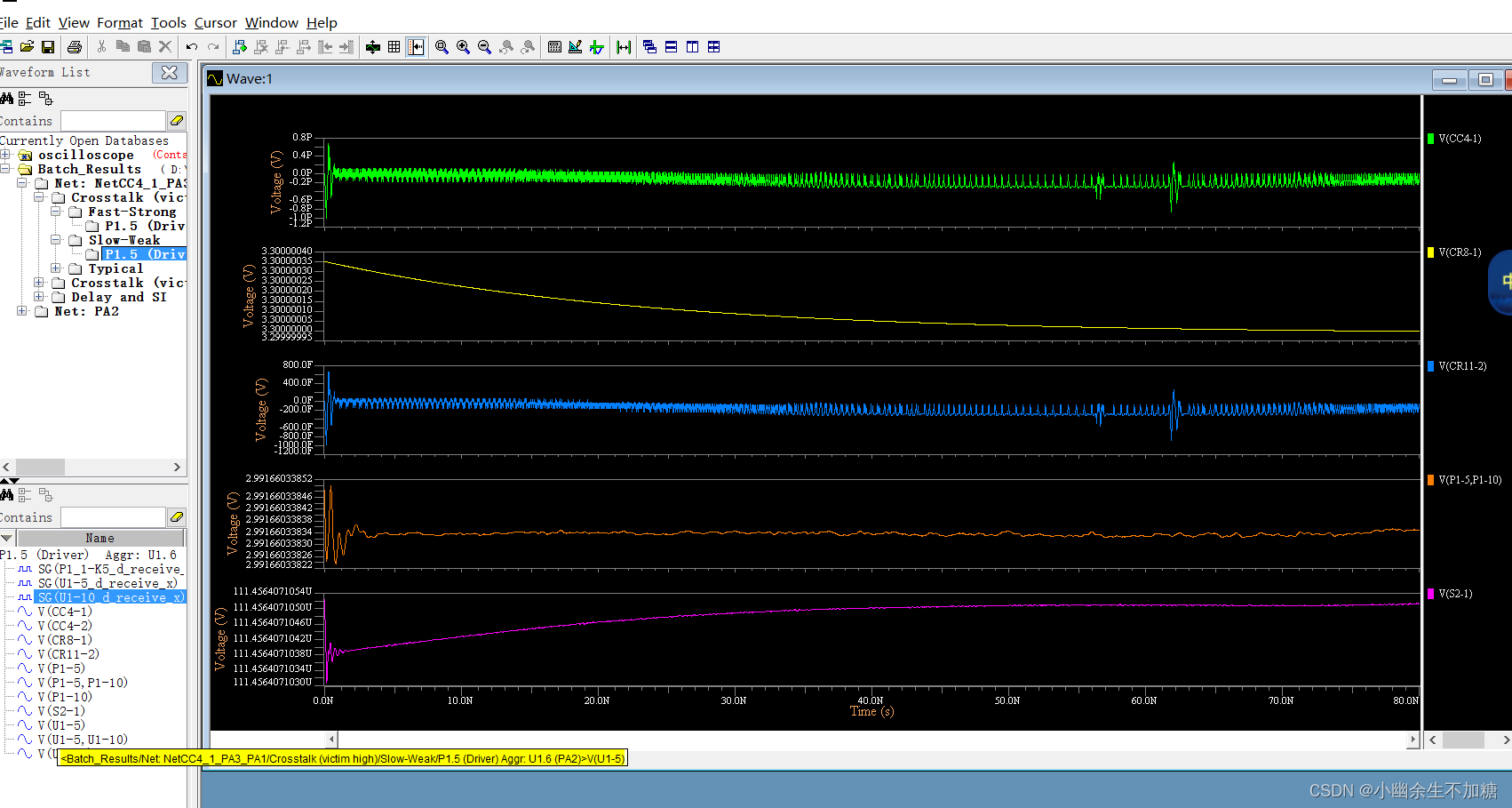

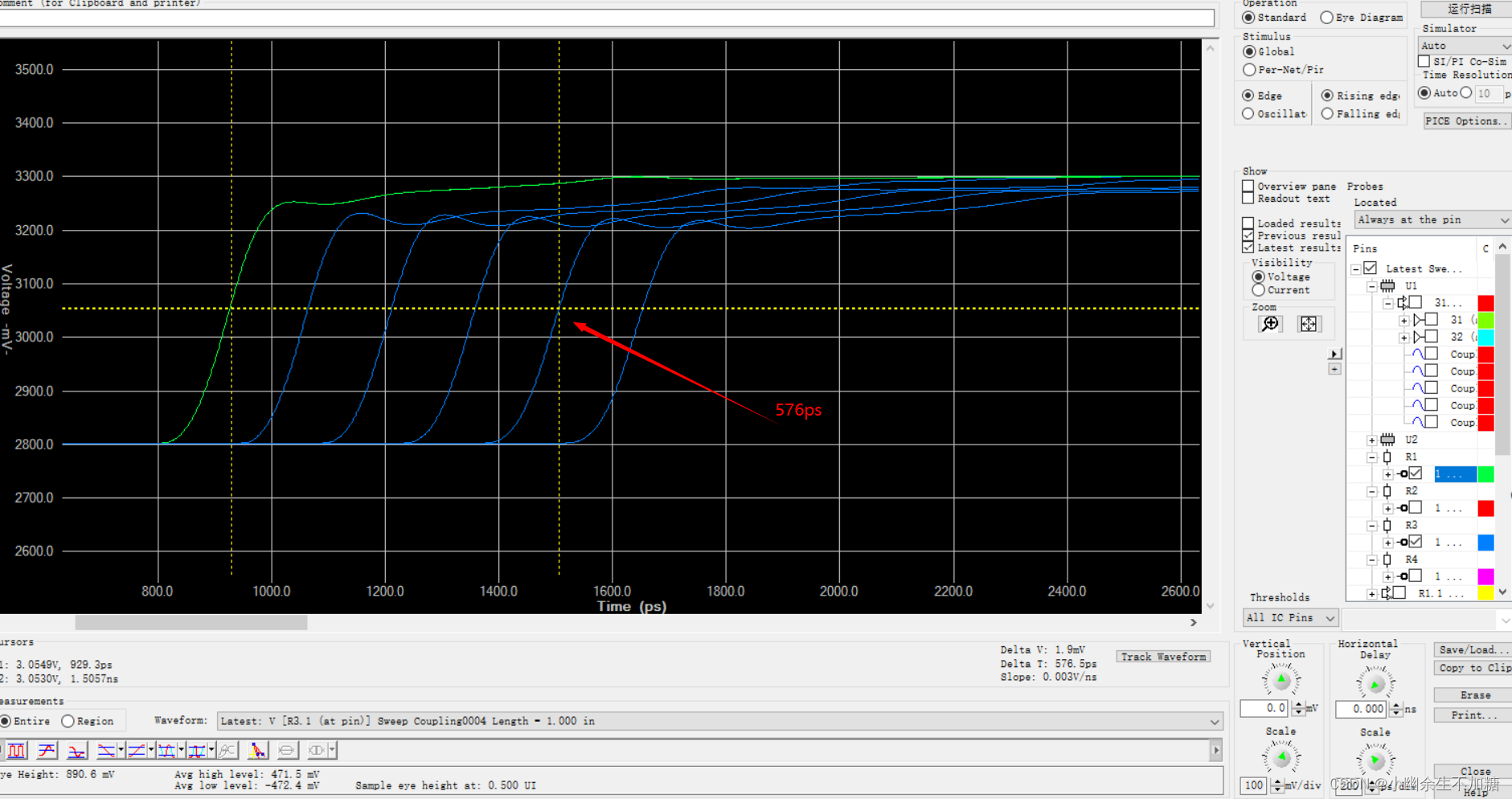

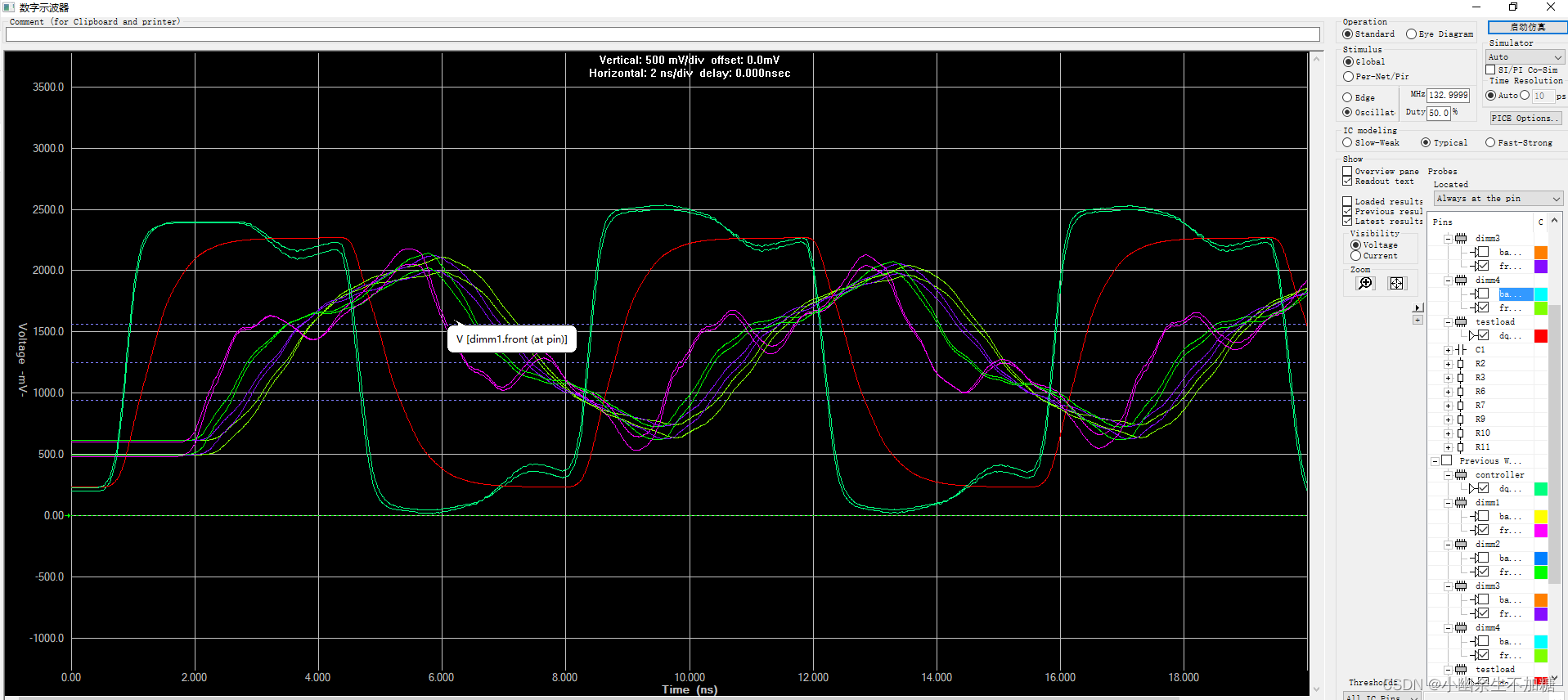

(9)对修改过参数的电路重新进行仿真,仿真结果如图所示:

由以上结果可以看出,减小串行端接电阻值对于高低电平切换区域上升沿和下降沿的反射波大规模起伏的影响微乎其微。由于该端接电路并没有帮助改善这种影响,我们将尝试改变电路上拉电阻,以确定改变哪些参数可以改善信号质量。

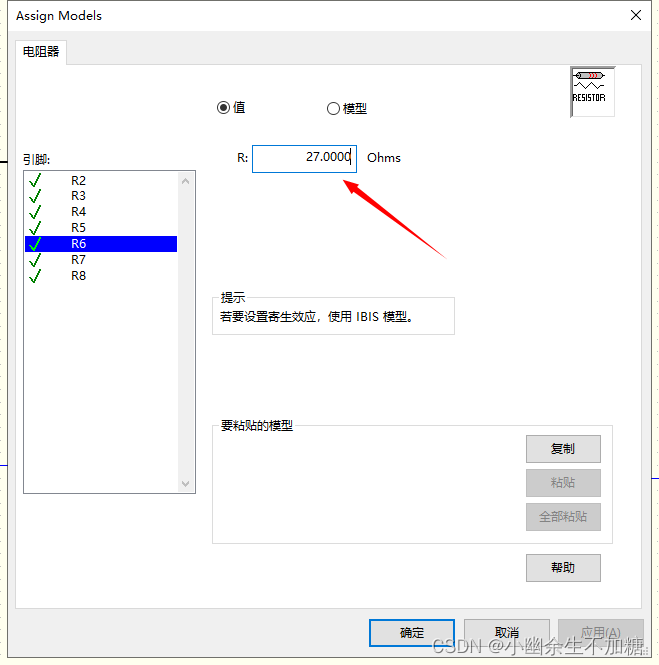

(10)在原理图编辑器中,右击拓扑结构右侧的上拉电阻R6。

(11)将电阻值从50改变到27Ω,如图所示,单击“确定”按钮。

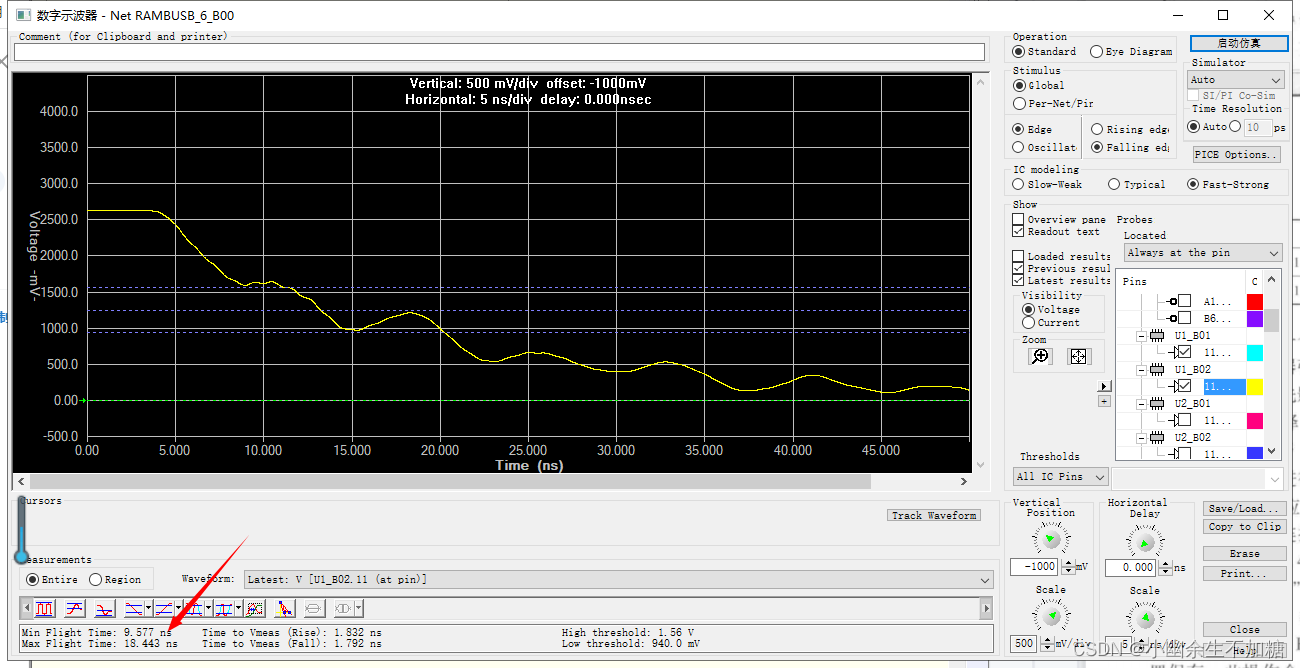

对改变后的电路重新进行仿真,结果如图所示。

由图中可知,**虽然在减小上拉电阻后,在高低电平的切换区域反射波的波动有所抑制,但是仍然可能遇到数据下降沿上的干扰。**如果继续减小上拉电阻阻值.虽然可以继续减小反射波的波动,但是上拉电阻阻值减小的同时会降低电路整体电压,进而影响到整个电路的运行,所以必须寻找更加全面的方法来解决这一问题。

下面,我们将调整部分线路长度,以此改善仿真结果。

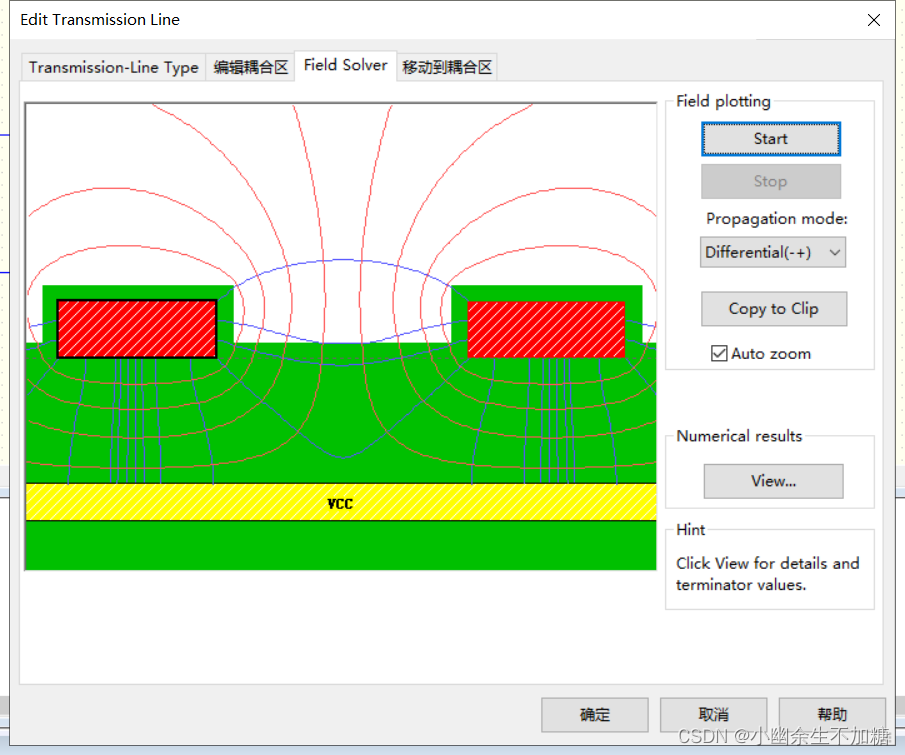

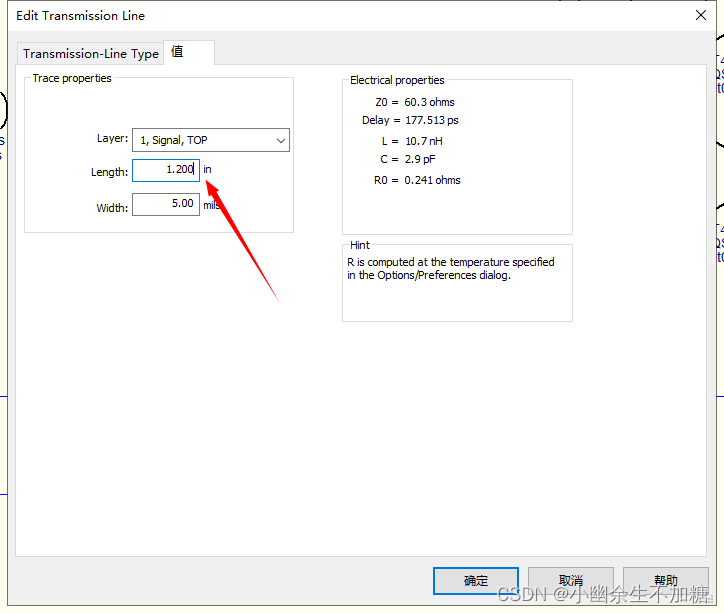

(12)在原理图编辑器中,调整DIMM连接器之间的间距。双击标有“DIMM1- DIMM2”的TL20。

(13)在编辑传输线对话框中,选择“Values”选项卡,改变传输线长度为1.2in,具体设置如图所示,然后单击“确定”按钮。

(14)重复上面的步骤,将传输线 DIMM2~DIMM3之间的TL26和DIMM3-DIMM4 之间的TL53 的长度均改为1.2in,进行仿真,结果如图所示:

重新模拟改变后的电路可以看到,现在的上升沿和下降沿都是没有变化的,在切换区域内基本没有发生太大的波动,因此基本达到了最佳效果。虽然传输线长度的改变在一定程度上可以改善信号质量,但是过分地要求走线长度而忽略了走线特性阻抗的匹配,同样会导致信号的失直。所以我们要在这两者之间权衡,选择最佳方案。

在讨论过走线长度对信号的影响后,对于走线宽度的研究也是有必要的。我们知道走线宽度的增加在有些情况下可以改良信号质量,并且可以增加空气流通,加大散热面积,从而

延长产品的使用寿命。

然而,走线过宽将会不可避免地改变走线的阻抗,导致发生反射,对信号产生影响。所以在对走线宽度的选择上,要根据实际的情况,做出细致的分析后,得出结论。由于篇幅关系,这里就不再讨论这一问题了。