1引言

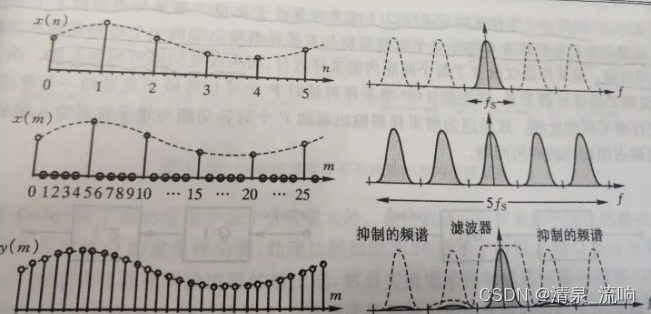

∑-△调制器与数字抽取滤波器是∑-△ADC实现16bit以上精度的关键电路模块。∑-△调制器依靠过采样与高阶闭环负反馈控制实现的噪声整形技术,将基带内的量化噪声搬移到高频段,而数字抽取滤波器则将带外高频段的噪声加以滤除,同时将输出频率降低到输入信号的奈奎斯特采样频率,最终实现对输入信号高精度的模数转换。

由于采用过采样技术,∑-△ADC对输入信号带宽有一定限制,比较适合低频信号的模数转换。

以音频信号44kHz的奈奎斯特采样频率为例,在64倍的过采样率下,即输入采样频率为2.816MHz,4阶∑-△调制器可实现16bit的转换精度;输出PDM信号经*倍降采样数字抽取滤波器的处理后恢复初始信号的奈奎斯特采样频率。为保持S-Δ调制器的精度性能,数字抽取滤波器的通带截止频率应为20kHz、阻带起始频率为24kHz、阻带衰减最小为80dB、通带纹波为±0.01dB、ADC有效位数大于15bit。

∑-△ADC的精度和转换速度由∑-△调制器决定,其中∑-△调制器的阶数、过采样率等参数直接决定了ADC的分辨率,一般只需小规模的数模混合电路即可实现,面积小且功耗低。用于滤除量化噪声的数字滤波器,为维持调制器的高分辨率就必须具有一定量的阻带衰减与很小的纹波,导致数字滤波器的阶数过大,并直接导致硬件消耗与功耗的显着增加。

本文针对高精度数字抽取滤波器IP电路,进行低成本与低功耗设计技术研究。在给定指标约束下,通过对CIC抽取滤波器结构的改进,同时将多相结构应用到补偿滤波器和半带滤波器中,获得比经典结构在硬件消耗与功耗上明显的降低。

2经典CIC滤波器结构

为确保数字滤波器信号的出路精度,采用单级抽取滤波器的阶数将与输入信号的采样频率成正比,而与过渡带宽成反比。对于输入频率2.816MHz、过渡带宽4kHz的设计指标,采用单级抽取结构的滤波器,由于频率高、过渡带窄而导致单级滤波器阶数过大,可实现性差,因此采用多级抽取结构成为必然。在多级结构中,第一级抽取结构的输入频率为系统最高的输入频率,但它的过渡带宽很大;最后一级虽然过渡带宽很窄,但输入频率降低;中间级的输入频率与过渡带宽均较为适中,这样的频率与过渡带分布配置,使得最终各级滤波器的总阶数远小于单级抽取的阶数,因此多级结构更具有实用价值。

CIC是由Hogenauer提出的一种无需使用乘法器的滤波器结构,结构简单,采样变换率高,可作为多级数字抽取滤波器中的输入级。阻带衰减为衡量CIC性能的一个重要指标,在Matlab下对抽取因子为64、32、…、2的最小阻带衰减进行仿真,确定当抽取因子最大为16时,阻带衰减仍满足设计要求,继续增大抽取率导致性能下降,则最大抽取倍率为16。

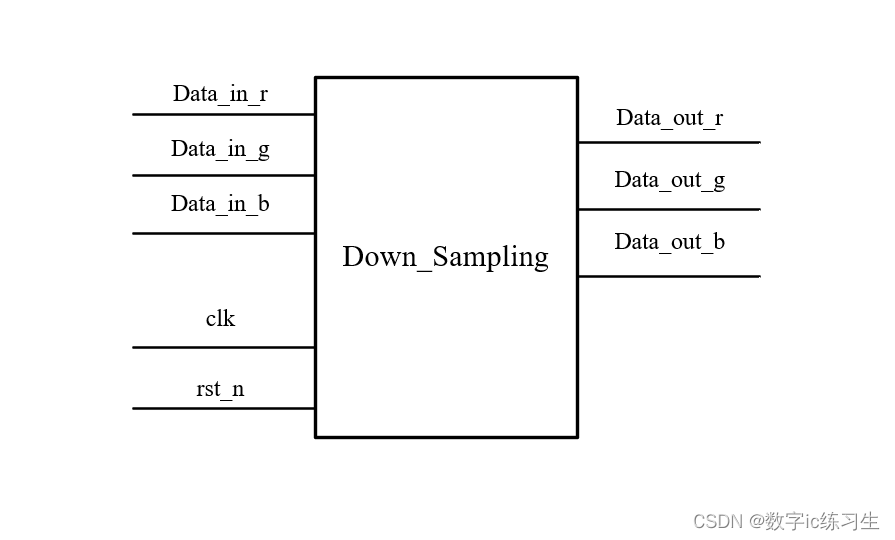

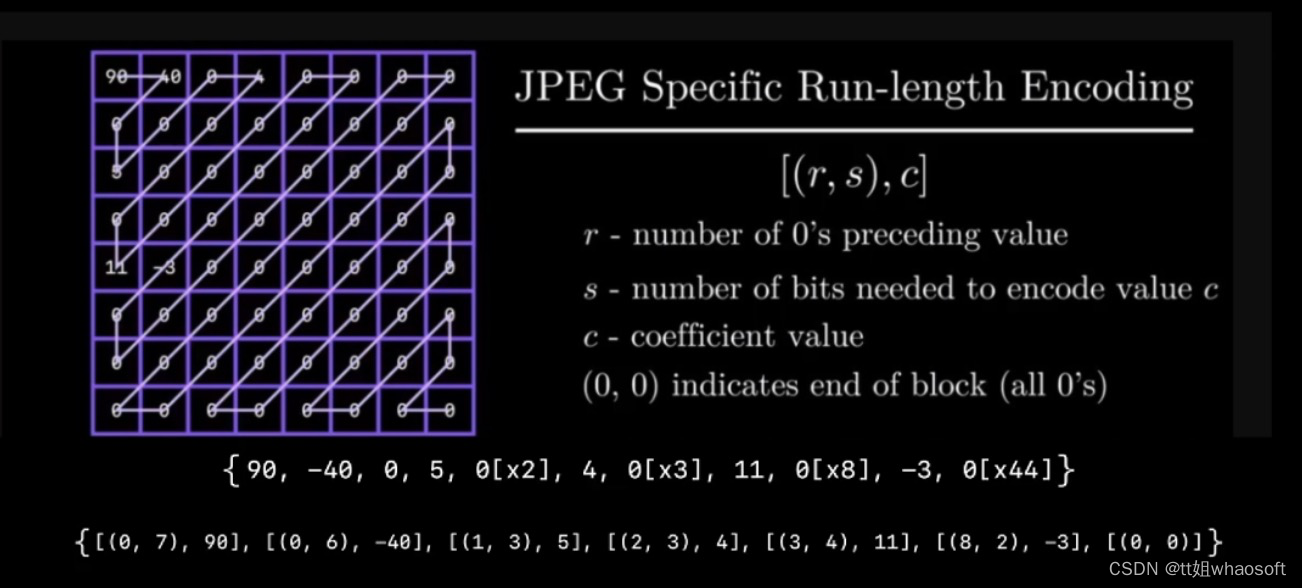

CIC滤波器的最大缺陷在于通带内的过多衰减,后面必须加一级补偿滤波器以确保补偿后的通带纹波仍满足指标要求,补偿滤波器同时还具备降采样抽取功率,可选择4倍抽取,也可先进行2倍抽取,然后用一级半带滤波器再完成2倍抽取。基于多级抽取有利于降低硬件资源与功耗的原则,64倍降采样数字抽取滤波器可采用如图1所示的三级结构。

图1系统结构框图

CIC降采样滤波器对系统性能的影响至关重要,其级联级数D与S-Δ调制器的阶数L之间存在D=L+1的关联,对于4阶∑-△调制器,D=5,在16倍降采样率下,CIC滤波器的系统函数为: