降采样FIR滤波器的设计与硬件实现

来源:luojiashao

作者:华仔

浏览:2051

时间:2016-08-10 14:18

标签:

摘要:

摘要:实现了一种全集成可变带宽中频宽带低通滤波器,讨论分析了跨导放大器-电容(OTA—C)连续时间型滤波器的结构、设计和具体实现,使用外部可编程电路对所设计滤波器带宽进行控制,并利用ADS软件进行电路设计和仿真验证。仿真结果表明,该滤波器带宽的可调范围为1~26 MHz,阻带抑制率大于35 dB,带内波纹小于0.5 dB,采用1.8 V电源,TSMC 0.18μm CMOS工艺库仿真,功耗小于21 mW,频响曲线接近理想状态。关键词:Butte

魏莉,林平分

(北京工业大学北京市嵌入式重点实验室,北京 100122)

0 引言

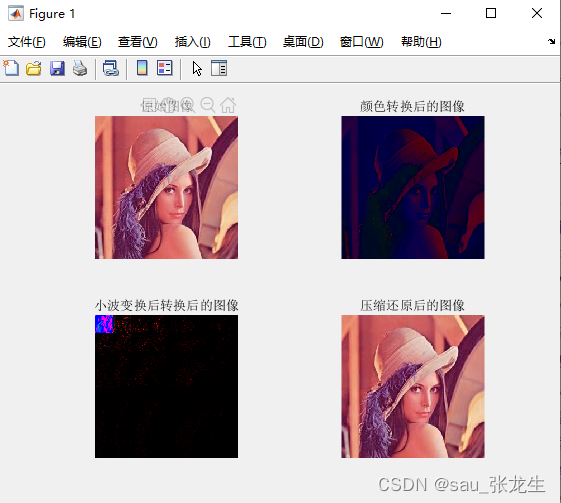

降采样数字滤波器可广泛应用于通信、声音和图像处理系统中。而当输入信号的带宽高于需处理的带宽时,对信号进行降采样处理可以大大减少数据量,提高数据率使实时处理容易实现。同时,为了克服在频域上的混叠,还需要先用低通滤波器过滤非处理带宽的信号能量,然后再降采样,以避免混叠。

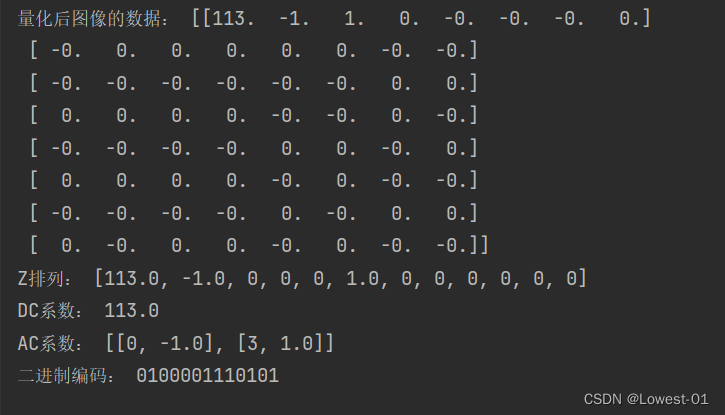

本文以LTE无线通信系统为例,提出了一种完整的降采样FIR滤波器的设计和硬件实现方案。该方案在利用FDAtool得到滤波器系数之后再进行定点化,并将各系数拆分成2的幂次方相加减的形式,以便进行移位相加。对于降采样,该设计没有使用传统的先滤波后采样的方案,而是在滤波过程中渗入了采样操作。这样就大大减少了硬件资源的消耗,并可将乘法器的使用数目降低到零。

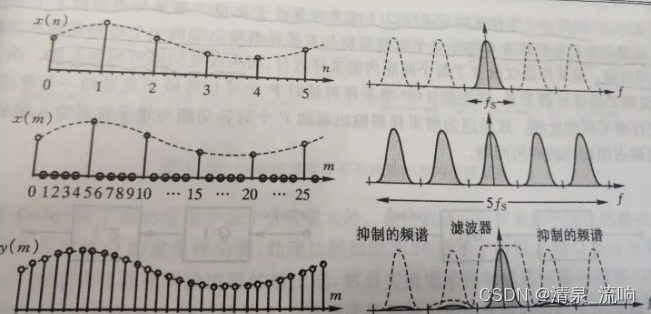

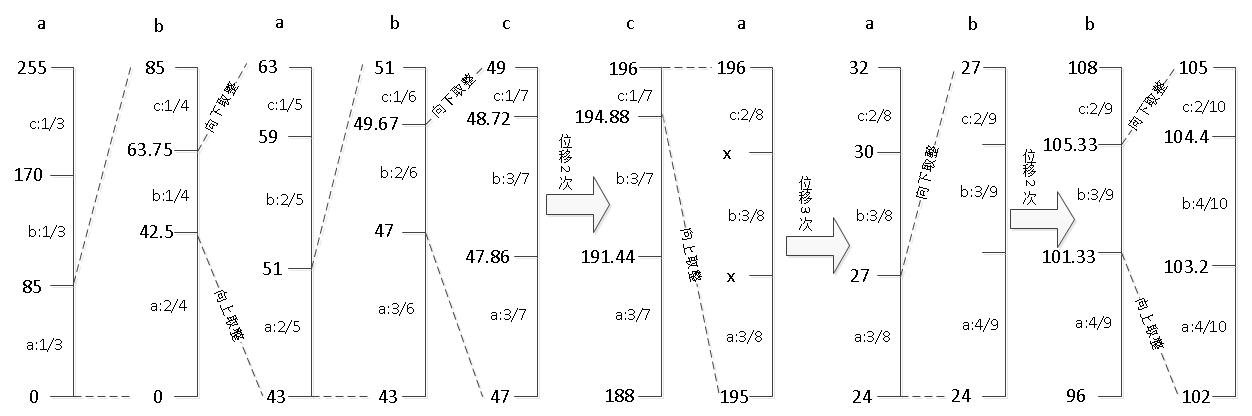

1 降采样滤波器的结构原理

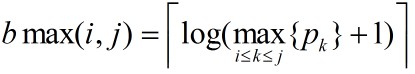

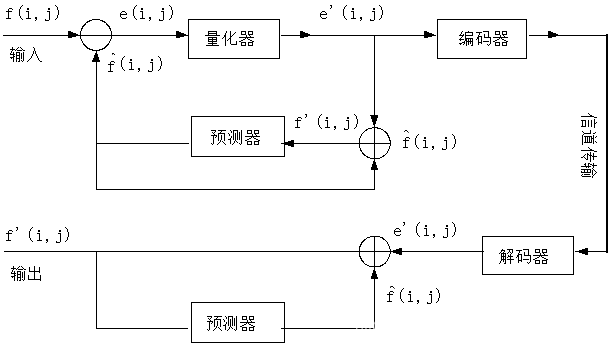

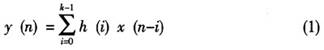

降采样滤波器的典型结构如图1所示,包括抗混叠滤波器和降采样器。其中D为降采样率,k表示滤波器阶数。从图1可以看出,抗混叠滤波器的输出y(n)是对输入序列x(n)加权求和的结果,即:

降