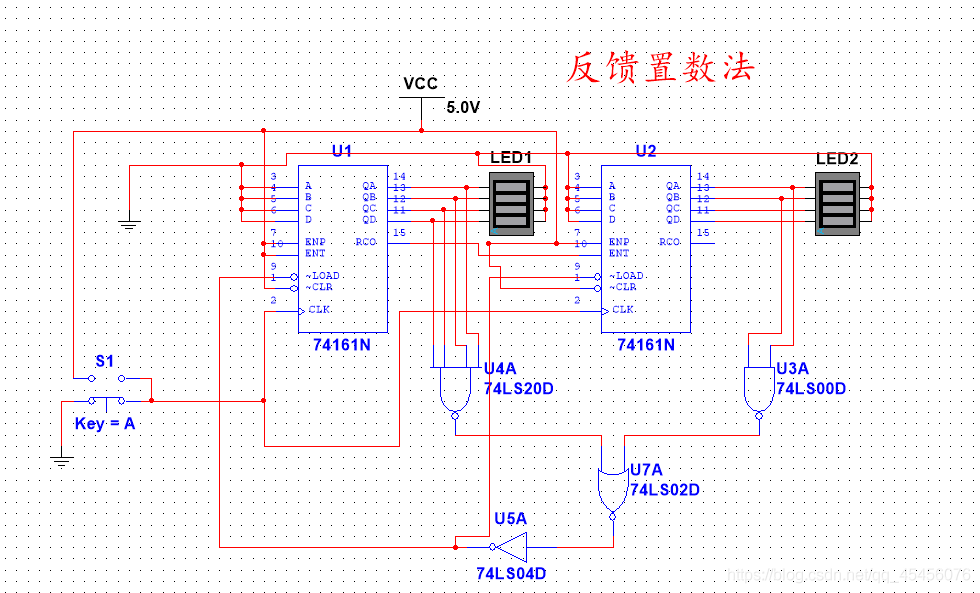

用74161计数器芯片设计一个20进制的计数器

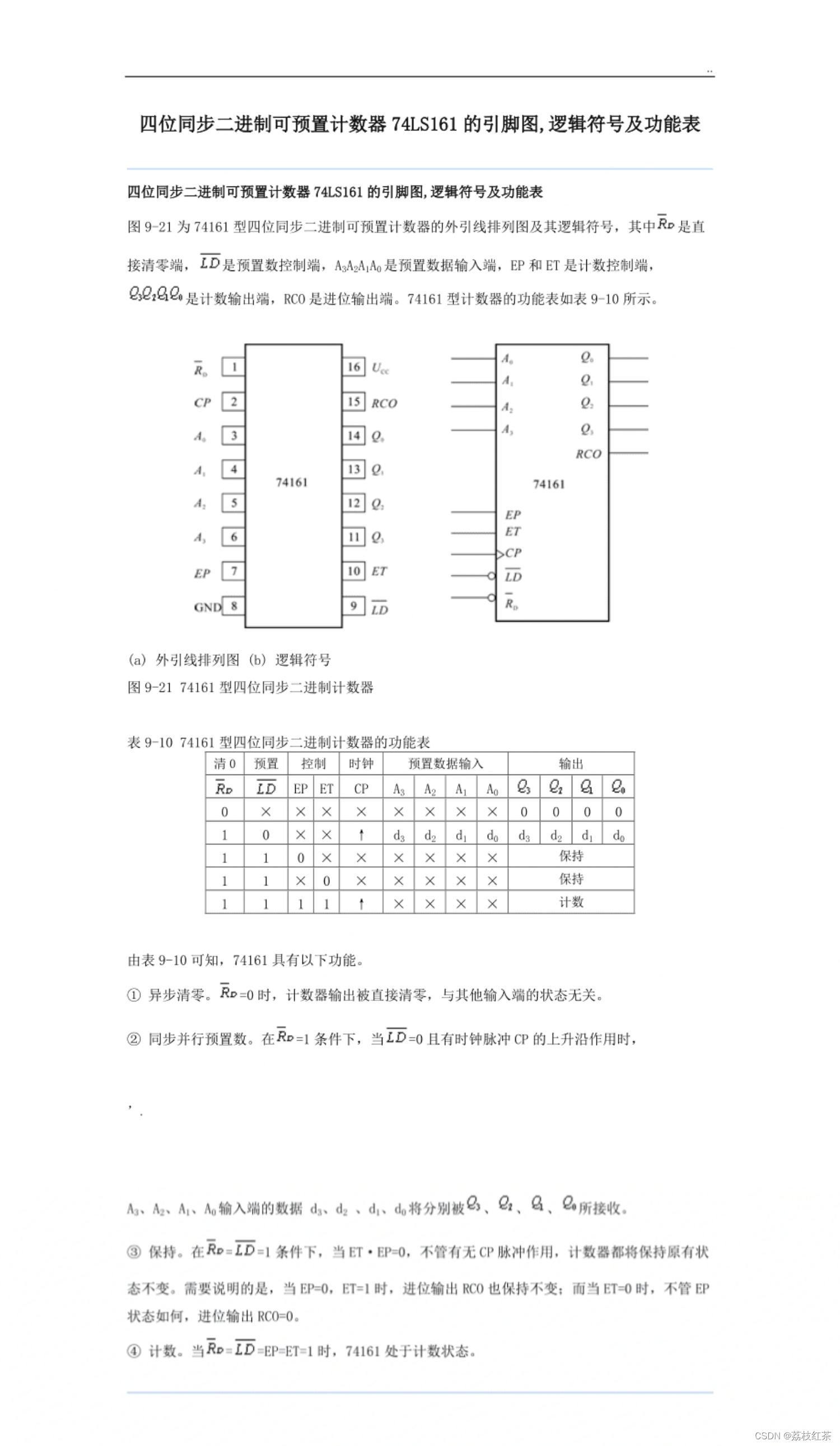

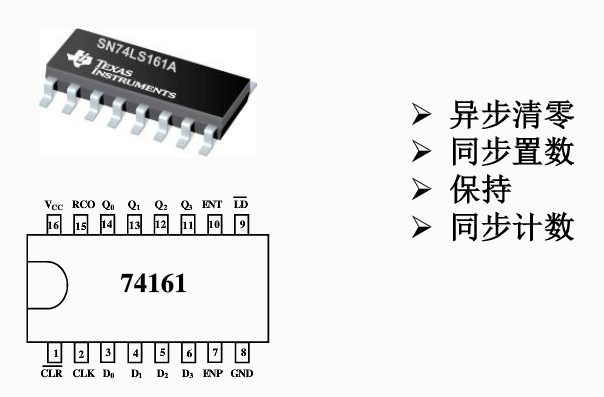

因为我们知道74161是16进制计数器,16<20,所以我们要用2个74161计数器,可以将一个74161变为二进制,一个74161变为10进制从而完成设计。事实上,采用74160计数器将更加方便,但这里我们采用的是74161计数器。

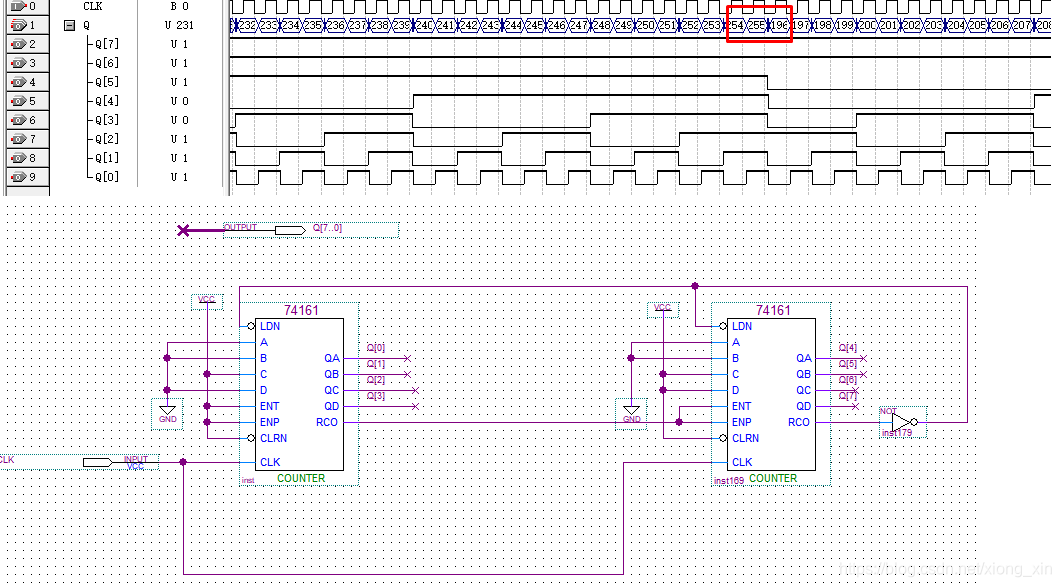

我们先建立一个project,然后新建一个Block Diagram文件双击BDF空白处,添加组件符号。如图所示。

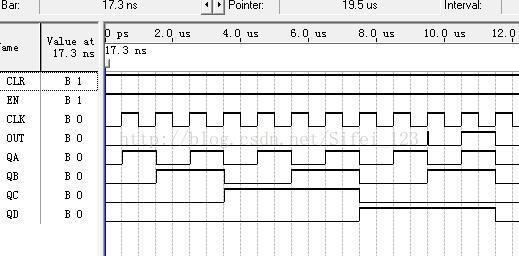

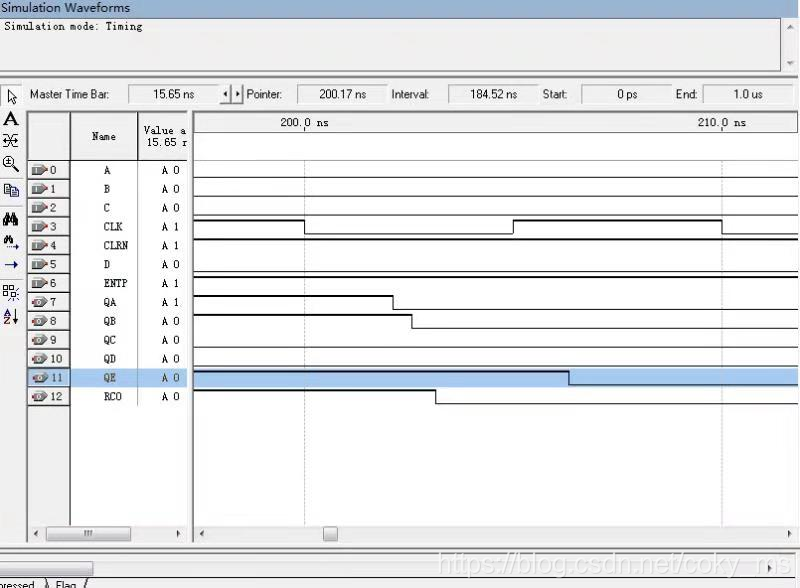

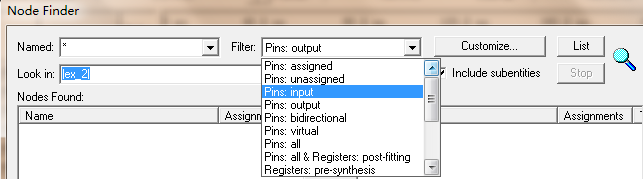

然后编译一次,新建一个vwf,矢量波形仿真文件,双击name下空白处,点击node finder然后对其添加 输入,输出管脚,可以根据pins:input或者pins:out点击list来选择输入输出引脚。切记在设置引脚前要先编译一次

接下来设置输入引脚的值,在这里我们设置D,C,B,A为0110,即在系统进入循环后第一片(上面那一片)74161将一直在0110到1111中循环,我们知道这是10个数,第二片芯片我们设置D,C,B,A为0000,ENT,ENP均为1,CLK为时钟脉冲,CLRN接1。

然后编译仿真得出仿真图

在这里要注意一开始计数器可能还没有进入循环,只有当输出输出过高电平后,计数器正式进入循环。由仿真结果图可知设计的正确性。