首发来自微信公众号:数字芯片设计

不定项选择

1.关于状态机编码,如下描述中正确的是()

【A】状态编码用parameter定义

【B】状态机必须有default态

【C】用组合逻辑和时序逻辑分离的风格描述FSM

【D】用case语句描述状态的转移

解析:状态机一般需要定义default态,但是对于case状态完全的状态机,可以不用default态,所以B错误;其他选项均正确。

正确答案:ACD

2.业界常用的验证方法学有()

【A】SystemC

【B】UVM

【C】SystemVerilog

【D】VMM

解析:业界常用的验证方法学有VMM(Verification Methodology Manual)、OVM(OpenVerification Methodology)和UVM(Universal Verification Methodology);SystemC和SystemVerilog不是验证方法学,是语言!

正确答案:BD

3.逻辑电路的动态功耗一般跟以下哪个因素相关()

【A】电压

【B】频率

【C】工艺

【D】工作温度

解析;动态功耗=开关功耗+短路功耗;开关功耗=CLVDD2f,其中CL为负载电容,VDD为电源电压,f为翻转频率(翻转率*频率),显然,电压、频率与开关功耗有关;短路功耗=tscVDDIpeakf,其中tsc代表短路状态的时间,Ipeak代表短路状态时的电流,工艺和工作温度会影响晶体管的性能,进而影响短路状态时的电流和短路状态的时间,所以会影响短路功耗。所以,电压、频率、工艺、工作温度都会影响动态功耗!

正确答案:ABCD

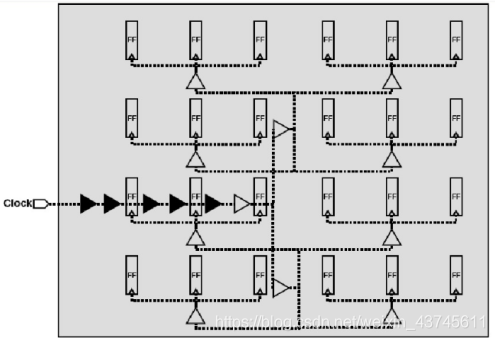

4.下列哪些项是异步处理需要考虑的因素()

【A】异步信号的电平或脉冲特性

【B】异步信号是不是总线

【C】两个异步时钟时间的频率关系

【D】异步信号是不是寄存器输出

解析:异步处理,对于单比特数据,如果是电平信号,可以用多级触发器来实现跨时钟域;如果是脉冲信号(必须由寄存器输出),则(1)慢时钟域到快时钟域,先用多级触发器进行同步,再用边沿检测电路即可得到相应的脉冲信号(2)快时钟域到慢时钟域,先将脉冲信号展宽,再同步到慢时钟域,再用边沿检测将信号转化为脉冲信号。

参考:

https://blog.csdn.net/moon9999/article/details/103657916

https://blog.csdn.net/wordwarwordwar/article/details/79894843

参考答案:ACD

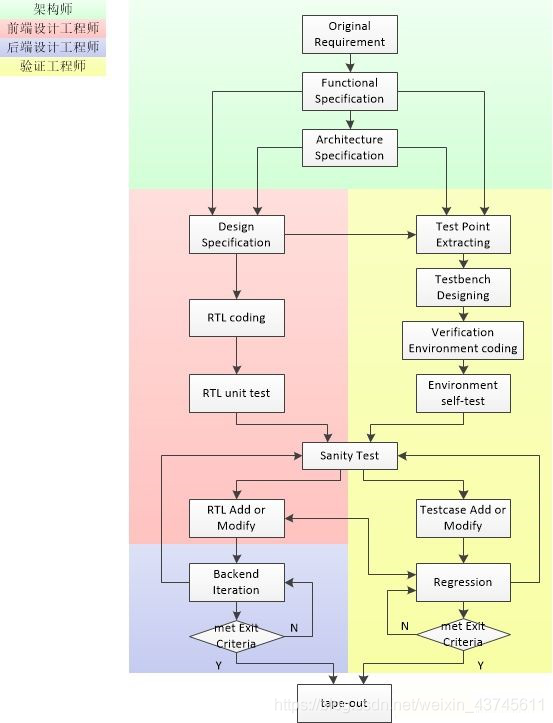

5.下列不属于分解测试点时的关注点的是()

【A】性能

【B】无充分理由的揣测

【C】偶然的设计失误

【D】可测性

【E】功能

解析:验证空间是一个无限集合,我们不可能细化到所有的元素,这就需要我们在分解时重视一些主要的关注点,同时忽略掉一些不必要的非关注点,测试点主要关注:

a)功能的正确;

b)功能、性能点的覆盖;

c)发现设计错误;

d)边界点,错误值;

e)对组合输入的处理考虑不周的地方;

f)根据经验普遍容易存在问题的地方:FIFO、状态机;

g)测试点需要关注各种条件的组合和条件序列;

测试点不关注:

a)偶然的设计失误;

b)无充分道理的揣测;

参考:基于System+VerilogVMM的仿真环境设计及其应用- 道客巴巴 (doc88.com)

正确答案:BC

以上答案是经过多人讨论分析,并且查阅了大量资料得出来的参考答案!欢迎大家多多参与讨论~(最近读者讨论不能用了,有问题的可以直接在公众号留言)