转载自:

数字电路:常见的锁存器浅析(S-R,S‘-R‘,使能端的S-R,D)_李嘉祎的博客-CSDN博客_锁存器

转载是怕万一博主删除,侵删。

锁存器是数字电路中基础的基础,本文将展现出常用的锁存器类型,便于读者的学习。

一、S-R锁存器

S-R锁存器由双或非原件组成

功能表如下:

①S,R均为0,S-R锁存器相当于双稳态元件,通过反馈回路维持电路之前的状态。

②仅R输出有效,易知Q端输出为0(低电位),Q'输出为1(高电位)

③仅S输出有效,易知Q'输出为0(低电位),Q输出为1(高电位)

④S,R输出均有效,易知Q和Q'输出均为0(低电位)

总之,我们可以发现S-R锁存器具有以下特性:

在双端输入信号均无效时(低信号),电路进入双稳态特性

在单端信号有效(高信号)时,S与Q,R与Q'输入输出信号相对应

在双端均有信号时(高信号),Q和Q'输出为0

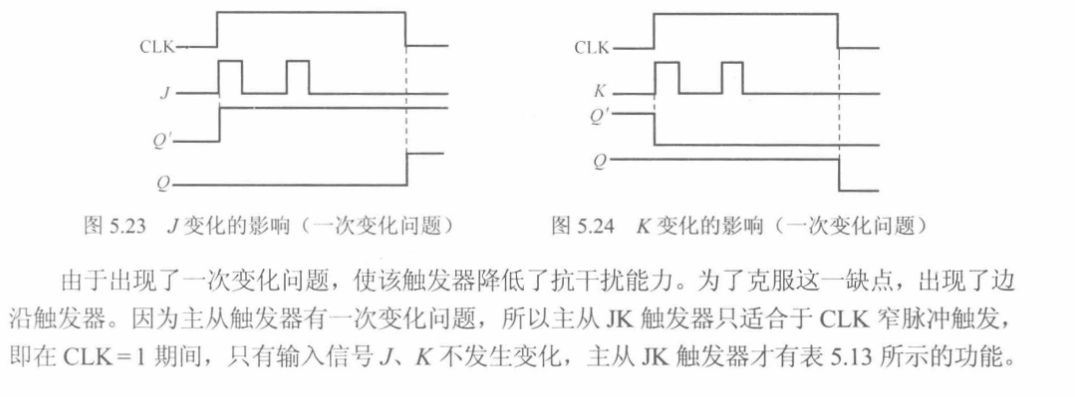

S/R端同时输入取消时,锁存器状态将无法预测(进入亚稳态/振荡状态)

二、S'-R'锁存器

对于S'-R'锁存器(双非或=双与非),相较于S-R锁存器(双或非门)使用性能更好

功能表如下:

①S',R'均为0,易知Q和Q'输出均为1(高电位)

②仅R输出有效,易知Q端输出为1(高电位),Q'输出为0(低电位)

③仅S输出有效,易知Q'输出为1(高电位),Q输出为0(低电位)

④S,R输出均有效,S-R锁存器相当于双稳态元件,通过反馈回路维持电路之前的状态

我们可以容易地发现,S'-R'锁存器与S-R锁存器的根本不同在于,S',R'端输入后取了相反的信号位/电位,导致输出相反。

其值得注意的不同处在于

①是S'/R'输入均为1时,锁存器保持其前一状态

②是当S'/R'均起作用(输入为低电平)时,锁存器输出均为1

总之,作者认为,只要掌握了S-R锁存器,S'-R'锁存器只不过是将输入信号进行反转,我们通过相应的分析即可得出S'-R'锁存器的输出

三、具有使能端的S'-R'锁存器

由于S-R/S'-R'锁存器在所有时间内对输入都是敏感的,我们期望有一种器件,它只有在使能输入C有效时,才对输入敏感,具有使能端的S-R锁存器(S-R latch with enable)应运而生。其结构为左侧SCR与非门结构+S'-R'锁存器。其电路结构和功能表如下图所示:

具有使能端的S'-R'锁存器具有如下特点

①当该锁存器处于双稳态原件有两种情况,C≠0输入均为0/C=0

②当该锁存器处于非双稳态时,S与Q,R与QN电位(信号)高低一致

四、D锁存器

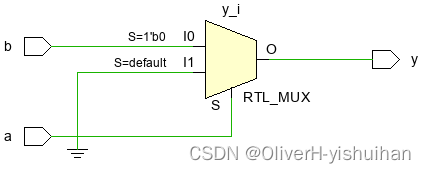

我们在运算中,常常希望有一些锁存器能够存储一些信息位串,D锁存器便应运而生,D锁存器有着能够避免S,R同时为0造成锁存器输出存在不可预测性的特性,其电路结构图和功能表如下:

其有如下几点特性:

①其具有使能端的S-R锁存器,S,R端输入信号永远相反。

②当C=1时(器件处于非双稳态特性),S,R与Q,QN一致。当C=0时,器件处于双稳态特性。

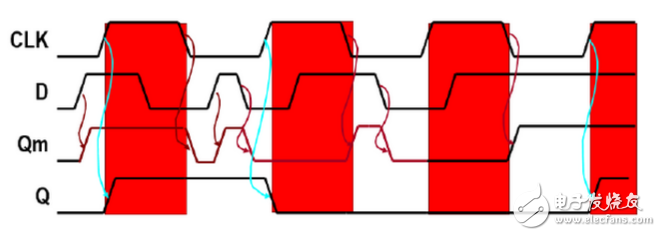

③D锁存器仍存在输出不可预测的情况:在C信号的下降沿附近往往有一个时间窗,在这段时间内D输入一定不能变化,否则D锁存器输出将进入不可预测状态(亚稳态/振荡态)。(如下图)

总结,本次我们介绍了S-R锁存器,S'-R'锁存器,具有使能端的S'-R'锁存器,D锁存器。

S-R锁存器(或非)

S,R为0时,锁存器表现双稳态原件特性。其他条件下,锁存器输入与输出相同。

S'-R'锁存器(非或)

S,R为1时,锁存器表现双稳态原件特性。其他条件下,锁存器输入与输出相反。

具有使能端的S'-R'锁存器(SCR与非+非或)

S,R与Q,QN信号态对应。C控制输入是否一定为0。(双稳态)

D锁存器

S,R端输入信号相反避免信号同时为0。

C控制输入是否为0。(双稳态)

D锁存器时间窗。(亚稳态)

锁存器进入亚稳态/振荡态的情况

在S-R系列的三种电路结构内,进入亚稳态情况为S,R同时为0/C突然=0。在D系列中,进入亚稳态为C信号时间窗内D信号变化。

在此,我们为避免读者疑惑,再次强调一下,双稳态≠亚稳态=双稳态+输出无法确定

————————————————

版权声明:本文为CSDN博主「李嘉祎」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/m0_66654182/article/details/122753394