目录

锁存器

1、简介

2、实验任务

3、程序设计

3.1、缺少 else 分支的锁存器代码

3.2、补齐 else 分支

3.3、缺少 default 的 case 语句的锁存器代码

3.3、补齐 default 的 case 语句

4、本章总结

锁存器

锁存器(俗称 Latch)是数字电路中的一种具有记忆功能的逻辑元件。锁存器对脉冲电平敏感的存储单元电路,它只在输入脉冲的高电平(或低电平)期间对输入信号敏感并改变状态。在数字电路中可以记录二进制数字信号“0”和“1”。

1、简介

锁存器(latch)是电平触发的存储单元,数据存储的动作取决于输入时钟(或者使能)信号的电平值,尽当锁存器处于使能状态时,输出才会随着数据输入发生变化。

锁存器不同于触发器,锁存器在不锁存数据时,输出端的信号随输入信号变化,就像信号通过一个缓存器一样;一旦锁存信号起锁存作用,则数据被锁住,输入信号不起作用。因此锁存器也称为透明锁存器,指的是不锁存时输出对输入是透明的。

锁存器的分类包括 RS 锁存器、门控 RS 锁存器和 D 锁存器,此处我们详细介绍下 D 锁存器。

那么什么是 D 锁存器呢?

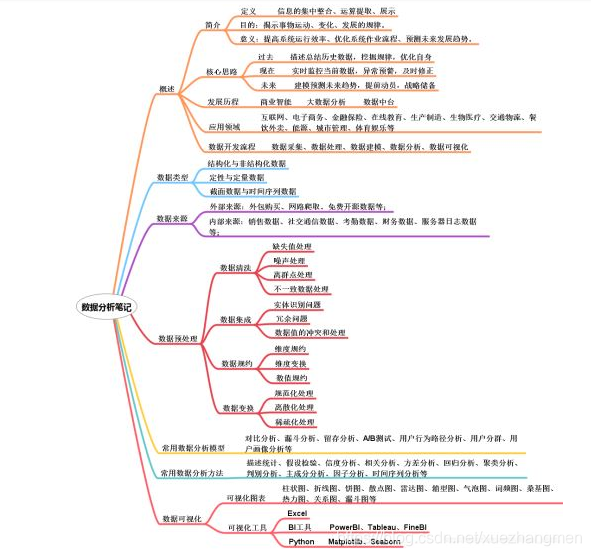

所谓的 D 锁存器,就是能够将输入的单路数据 D 存入到锁存器中的电路,下面是我们给出 D 锁存器的电路图,如下图所示。

从 D 锁存器的电路图中我们可以看出,该电路主要是由两个部分组成,第一个部分是由 G1、G2两个与非门组成的 RS 锁存器,第二个部分是由 G3、G4 两个与非门组成的控制电路。C 为控制信号,用来控制 G3 和 G4 的激励输入。

下面我们来分析下 D 锁存器的工作原理,当控制信号 C=0 时,根据与非门的逻辑定律,无论 D 输入什么信号,RD 和 SD 信号同时为 1。根据由与非门组成的 RS 锁存器的逻辑定律,RD 和 SD 都同时等于 1 的话,锁存器的输出端 Q 将维持原状态不变。那么,当控制端 C=1 时,如果此时 D=0,SD 就等于 1,RD 就等于 0,根据 RS 锁存器的逻辑规律,电路的结果就为 0 状态;如果 D =1,那么 RD 就等于 1,SD 也就等于 0,锁存器的结果就为 1 状态,也就是说,此时锁存器的状态是由激励输入端 D 来确定的,并且 D 等于什么,锁存器的状态就是什么,这就是我们前面所说的,将单路数据 D 存入到锁存器之中。

根据上面的描述,我们可以推出 D 锁存器的特性表,Qn 是指触发器当前逻辑状态也即触发前的状态,Qn+1 是指触发后的状态。

通过这个表格,我们可以看出,当 C 为 1 时,D 的状态和 Qn+1 的状态完全一样,当 D=0 时,Qn+1=0,当 D=1 时,Qn+1=1。

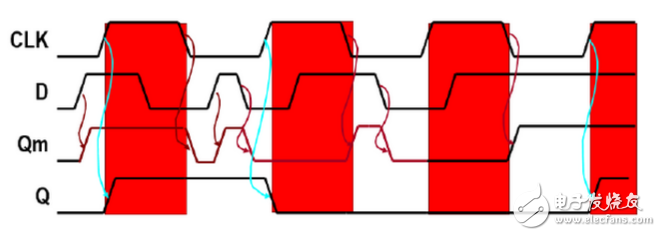

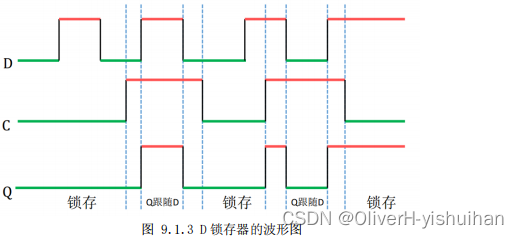

我们还可以进一步画出 D 锁存器的波形图。

从 D 锁存器的波形图图中我们可以看出,D 是锁存器的输入信号,C 是锁存器的控制信号,Q 是锁存器的输出信号,当控制信号 C 为高电平时,输出信号 Q 将跟随输入信号 D 的变化而变化,大家看虚线内,Q 的波形等于 D 的波形。当控制信号 C 从高电平变为低电平时,输入信号 D 的状态将会决定锁存器将要锁存的状态。大家可以看到,C 由高变低的那两条虚线内,所对应的输入信号 D 为低电平,那么输出信号 Q 也将会锁存低电平。最后面的那两条虚线也同理,D 为高电平,Q 锁存高电平。

D 锁存器的介绍就到这里,下面我们来从实际的逻辑设计里面看下锁存器的坏处。

在绝大多数设计中我们要避免产生锁存器。它会让您设计的时序出问题,并且它的隐蔽性很强,新人很难查出问题。锁存器最大的危害在于不能过滤毛刺和影响工具进行时序分析。这对于下一级电路是极其危险的。所以,只要能用触发器的地方,就不用锁存器。

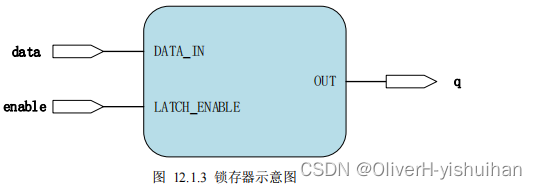

由上图示意图我们可以看到,锁存器没有时钟信号,只有数据输入和使能以及输出 q 端,没有时钟信号也就说明我们没有办法对这种器件进行时序分析,这个在时序电路里面是非常危险的行为,因为可能引起时序不满足导致电路功能实现有问题。

2、实验任务

设计一个锁存器电路。

3、程序设计

代码里面出现 latch 的两个原因:在组合逻辑中,if 或者 case 语句不完整的描述,比如 if 缺少 else 分支,case 缺少 default 分支,导致代码在综合过程中出现了 latch。解决办法就是 if 必须带 else 分支,case 必须带 default 分支。

大家需要注意下,只有不带时钟的 always 语句的 if 或者 case 语句不完整才会产生 latch,带时钟的语句 if 或者 case 语句不完整描述不会产生 latch。

3.1、缺少 else 分支的锁存器代码

根据程序设计的思路,我们来设计一个 if 语句,但缺少 else 分支的锁存器代码(latch.v),代码编写如下:

//实验任务:设计一个锁存器电路

//程序设计:

//代码里面出现 latch 的两个原因:在组合逻辑中,if 或者 case 语句不完整的描述,

//比如 if 缺少 else 分支,case 缺少 default 分支,导致代码在综合过程中出现了 latch。

//解决办法就是 if 必须带 else 分支,case 必须带 default 分支。

//大家需要注意下,只有不带时钟的 always 语句的 if 或者 case 语句不完整才会产生 latch,

//带时钟的语句 if 或者 case 语句不完整描述不会产生 latch。module latch(//input clk, //system clkinput a,input b,output reg y // output signal);//*******************************************

//** main code

//*******************************************always @(*) beginif(a==1)y=b;//else// y=0;

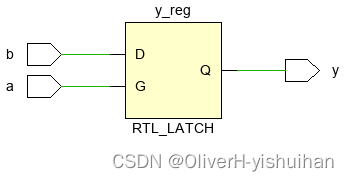

endendmodule程序中的一个组合逻辑电路使用了 if 语句,但是这个语句没有 else 分支,我们可以使用 Vivado查看 RTL 视图。

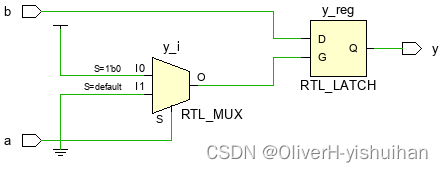

从 RTL ANALSIS 视图中可以看出,模块下面显示了 RTL_LATCH,可以看出这个电路就是 latch。

3.2、补齐 else 分支

下面我们把 else 补充完整再来看下电路结构,代码如下:

//实验任务:设计一个锁存器电路

//程序设计:

//代码里面出现 latch 的两个原因:在组合逻辑中,if 或者 case 语句不完整的描述,

//比如 if 缺少 else 分支,case 缺少 default 分支,导致代码在综合过程中出现了 latch。

//解决办法就是 if 必须带 else 分支,case 必须带 default 分支。

//大家需要注意下,只有不带时钟的 always 语句的 if 或者 case 语句不完整才会产生 latch,

//带时钟的语句 if 或者 case 语句不完整描述不会产生 latch。module latch(//input clk, //system clkinput a,input b,output reg y // output signal);//*******************************************

//** main code

//*******************************************always @(*) beginif(a==1)y=b;elsey=0;

endendmodule

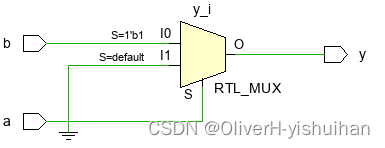

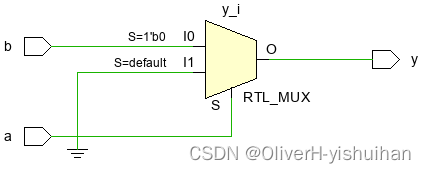

这个代码中,添加了 else 分支,我们可以使用 RTL ANALSIS 视图再看一下综合的电路结构。

上图所示的电路结构是一个 mux 选择电路,可以看出,加了 else 分支的电路就不会有 latch 电路。

3.3、缺少 default 的 case 语句的锁存器代码

下面我们来写一个不带 default 的 case 语句,代码如下:

//

//实验任务:设计一个锁存器电路

//程序设计:

//代码里面出现 latch 的两个原因:在组合逻辑中,if 或者 case 语句不完整的描述,

//比如 if 缺少 else 分支,case 缺少 default 分支,导致代码在综合过程中出现了 latch。

//解决办法就是 if 必须带 else 分支,case 必须带 default 分支。

//大家需要注意下,只有不带时钟的 always 语句的 if 或者 case 语句不完整才会产生 latch,

//带时钟的语句 if 或者 case 语句不完整描述不会产生 latch。module latch(//input clk, //system clkinput a,input b,output reg y // output signal);//*******************************************

//** main code

//*******************************************always @(*) begin

// if(a==1)

// y=b;

// //else

// // y=0;case(a)0:y = b;endcase

endendmodule

从 RTL ANALSIS 视图中可以看出,模块下面显示了 RTL_LATCH,可以看出这个电路就是 latch。

3.3、补齐 default 的 case 语句

下面我们把 case 语句的 default 补充完整再来看下电路结构,代码如下:

//

//实验任务:设计一个锁存器电路

//程序设计:

//代码里面出现 latch 的两个原因:在组合逻辑中,if 或者 case 语句不完整的描述,

//比如 if 缺少 else 分支,case 缺少 default 分支,导致代码在综合过程中出现了 latch。

//解决办法就是 if 必须带 else 分支,case 必须带 default 分支。

//大家需要注意下,只有不带时钟的 always 语句的 if 或者 case 语句不完整才会产生 latch,

//带时钟的语句 if 或者 case 语句不完整描述不会产生 latch。module latch(//input clk, //system clkinput a,input b,output reg y // output signal);//*******************************************

//** main code

//*******************************************always @(*) begin

// if(a==1)

// y=b;

// //else

// // y=0;case(a)0:y = b;default:y = 0;endcase

endendmodule

可以看出,这个语句有 case 的 default 分支,我们使用 vivado 的 RTL ANALSIS 来看下综合的电路结构。

上图所示的电路结构是一个 mux 选择电路,可以看出,加了 case 的 default 分支的电路就不会有 latch电路。

4、本章总结

本章需要掌握的重点是代码里面出现 latch 在组合逻辑中出现的原因:if 语句或者 case 语句不完整的描述,比如 if 缺少 else 分支,case 缺少 default 分支,导致代码在综合过程中出现了latch。解决办法就是 if 必须带 else 分支,case 必须带 default 分支。

大家需要注意下,只有不带时钟的 always 语句的 if 或者 case 语句不完整才会产生 latch,带时钟的语句 if 或者 case 语句不完整描述不会产生 latch。