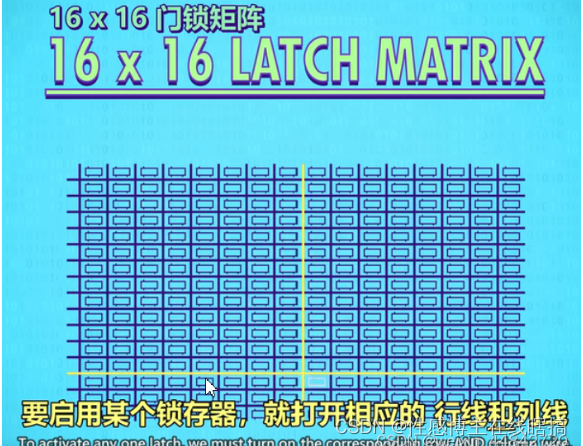

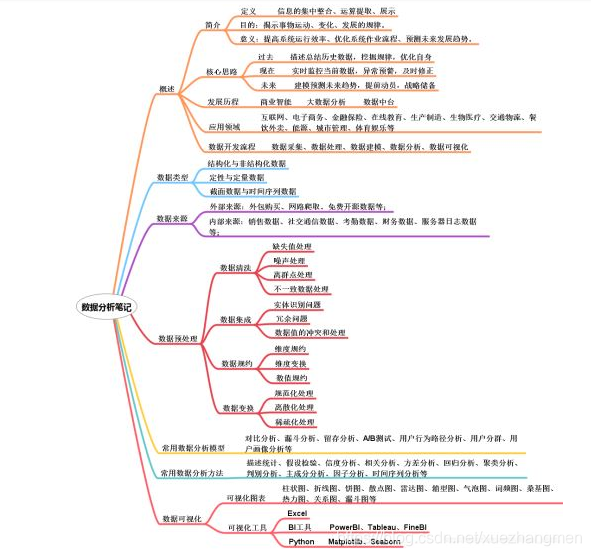

1.锁存器(Latch)

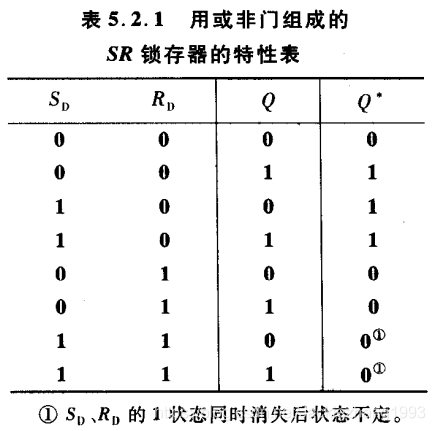

1.1.SR锁存器(基本锁存器)

由两个或非门或者两个与非门组成,电路结构、图形符号和特性表如下所示。

此时,输出状态(次态)与输入状态、锁存器初态都有关。

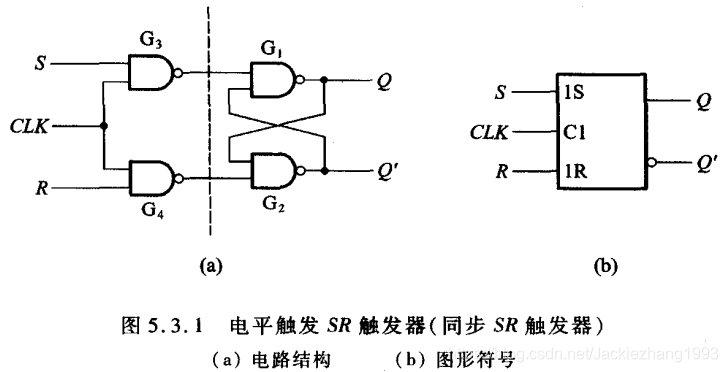

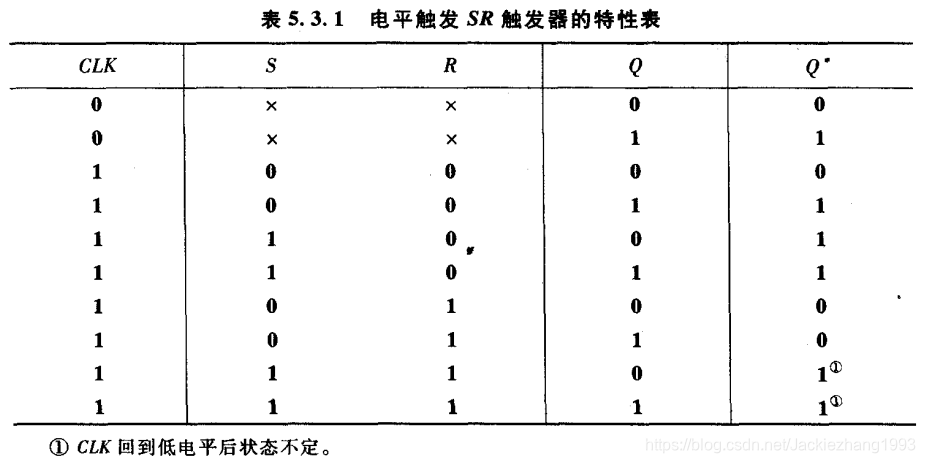

1.2.电平触发SR触发器(门控SR锁存器)

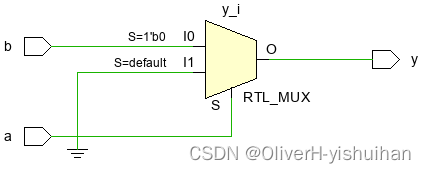

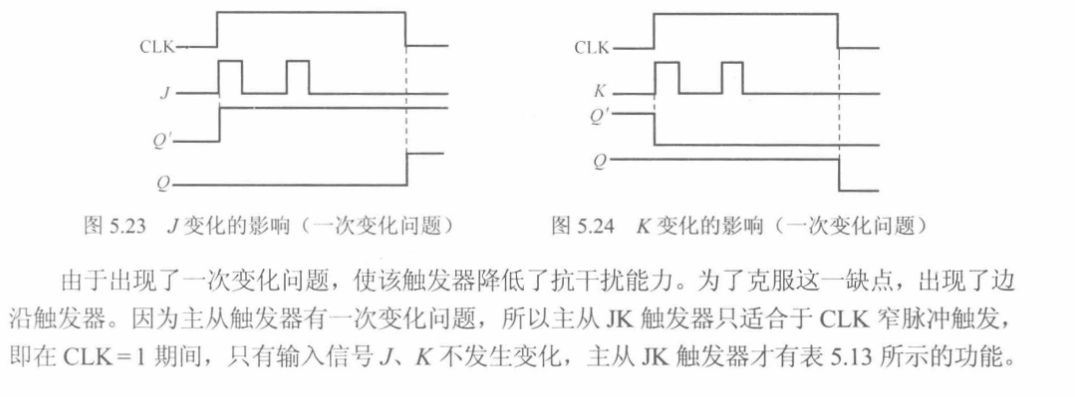

当CLK=0时(无效),输出状态(次态)保持不变;只有当CLK=1时(有效),输出状态才随输入、初态的不同而改变,且与SR锁存器的特性一样。

当门控锁存器的控制信号有效时,锁存器就变成了一个组合电路,若此时输入信号发生多次变化,输出状态也可能发生多次变化,这一现象称为锁存器的空翻。此时,时序逻辑电路的模型就等效为两个各组合电路互为反馈的反馈系统,因此,系统有可能会因为瞬态特性不稳定而产生振荡现象,抗干扰能力差。

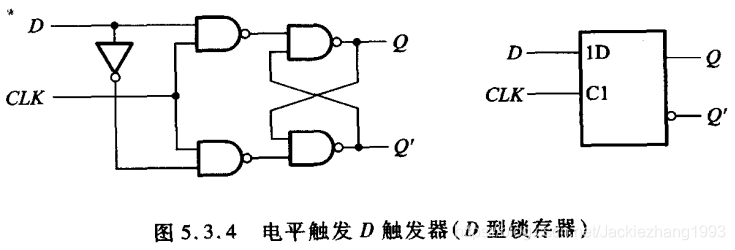

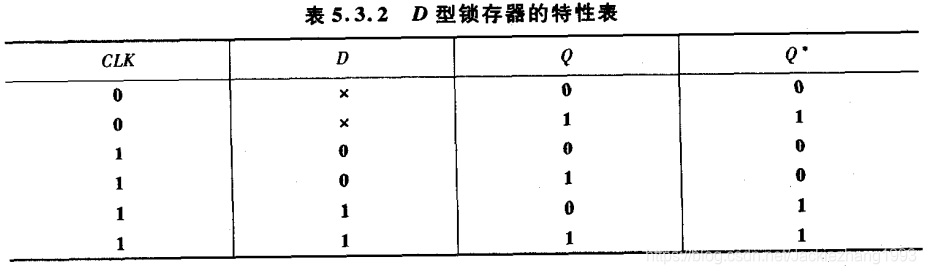

1.3.电平触发D触发器(D型锁存器)

在CLK的有效电平期间,输出状态始终随输入状态变化,输出与输入状态保持相同,所以这个电路又叫“透明的D型锁存器”。

2.触发器(flip-floph)

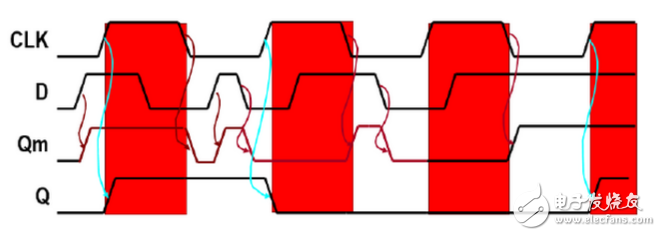

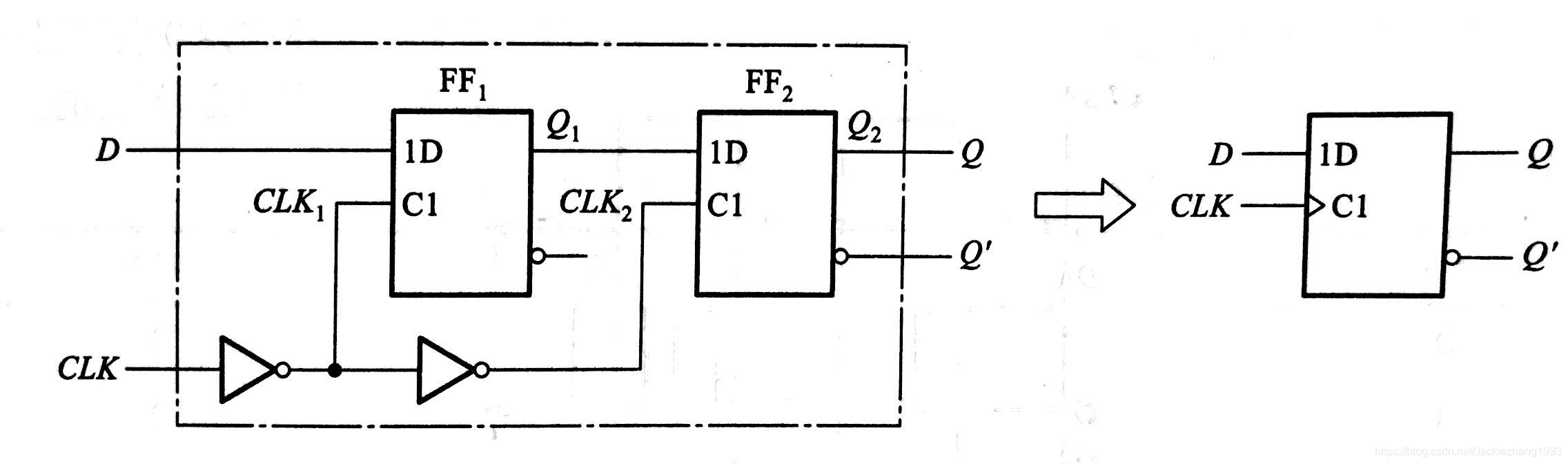

2.1.边沿触发D触发器

由两个D型锁存器组成,次态仅取决时钟有效边沿到达时输入的逻辑状态,且值保持不变到下次触发到达时(保持n个时钟周期)。

电路抗干扰能力强,工作可靠性更高。

3.寄存器(Register)

寄存器能够存寄一组二值代码,即由N个触发器组成。

另外,可以参考FPGA 中的latch 锁存器。