第六章

数据总线

本章描述了数据总线。它包含以下部分:

– 数据总线 on page 6-60.

– 大小端 on page 6-61.

– 数据总线宽度 on page 6-65.

6.1 Data buses

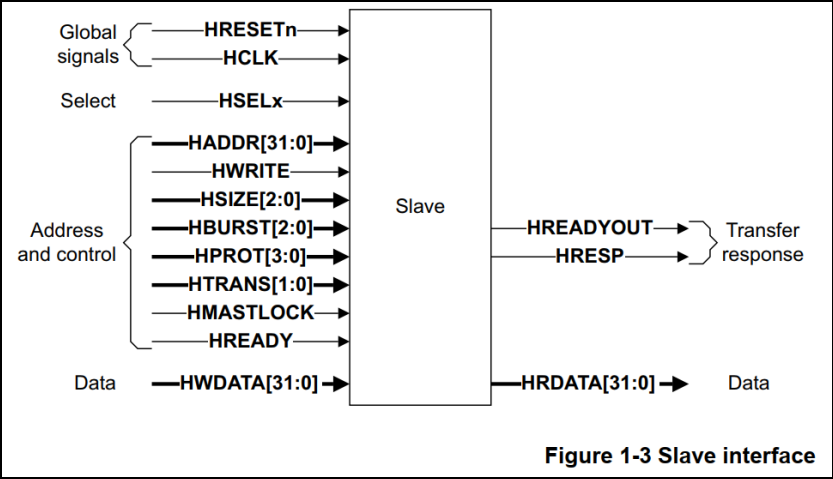

实现AHB系统需要独立的读写数据总线。虽然推荐的最小数据总线宽度被指定为32位,但可以按照第6-65页的数据总线宽度进行更改。

数据总线描述如下:

– HWDATA.

– HRDATA.

– Endianness on page 6-61.

6.1.1 HWDATA

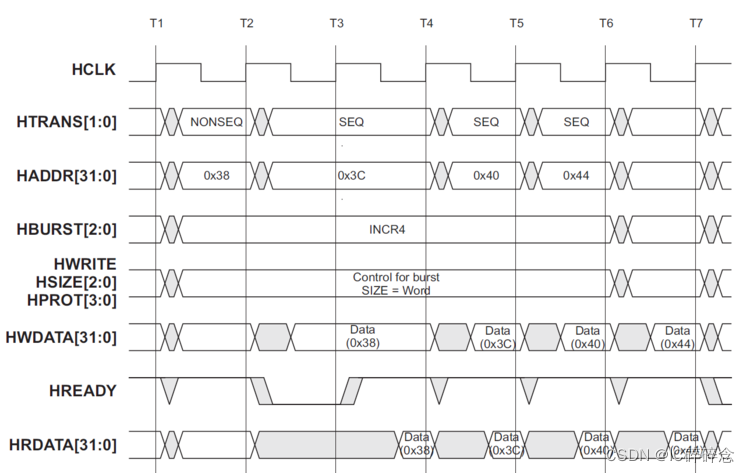

在写传输过程中,主机驱动写数据总线。如果传输被扩展,那么主机必须保持数据有效,直到传输完成,传输完成用HREADY HIGH表示。关于保持信号在多个周期内有效的详细信息,请参见7-68页的时钟。

对于小于总线宽度的传输,例如32位总线上的16位传输,主机只需要驱动适当的字节通道。从机从正确的字节通道中选择写数据。关于小端和大端系统中活跃的字节通道的详细信息,请参见第6-61页的Endianness。

6.1.2 HRDATA

在读传输期间,合适的从机驱动读数据总线。如果从机通过保持HREADY LOW来扩展读传输,那么从机只需要在传输的最后一个周期中提供有效的数据,用HREADY HIGH表示。

对于小于总线宽度的传输,从机只需要在活跃字节通道上提供有效的数据。主机从正确的字节通道中选择数据。

当传输以OKAY响应完成时,从机只需要提供有效的数据。错误响应不需要有效的读数据。

6.2 Endianness

AHB同时支持大端和小端系统。支持两种大端数据存储方法。

AHB5引入了Endian属性来定义支持哪种形式的大端数据访问。

BE8–字节不变量大端格式. 这个词语,字节不变量的大端字节,源于字节访问(8位)使用相同的数据总线位作为小端访问相同的地址。

BE32–字不符变量大端格式。术语“字不变大端格式”源于一个事实,即字访问(32位)使用相同的数据总线位来访问最重要(MS)和最不重要(LS)字节,就像访问相同地址的小端序访问一样。

关于字节不变的大端字节数的更多信息可以在第6-63页的字节不变一节中找到。

下面的方程组定义了哪些数据位用于小端、字节不变的大端和字不变的大端访问。

方程使用以下变量:

Address–传输的地址.

Data_Bus_Bytes --8位数据总线字节通道的数量。

INT(x) --向下舍入x的整数值。

6.2.1 Little endian

当一个小端组件访问一个字节时,下面的公式显示使用哪些数据总线位:

Byte_Lane=Address–(INT(Address / Data_bus_Bytes))×Data_Bus_Bytes

数据在DATA[(8 × Byte_Lane) + 7 : (8 × Byte_Lane)]上传输。

当发生较大的小端传输时,数据的传输是这样的:

– LS字节被传输到传输地址。

– 增长的高位字节被传输到顺序递增的地址。

6.2.2 Byte-invariant big-endian

当一个字节不变的大端格式组件访问一个字节时,下面的公式显示使用哪些数据总线位:

Byte_Lane=Address–(INT(Address / Data_bus_Bytes))×Data_Bus_Bytes

数据在DATA[(8 × Byte_lane) + 7 : (8 × Byte_lane)]上传输。

Note

这些方程与小端格式的方程是相同的。因为大端和小端访问对于字节传输是相同的,所以术语字节不变量被用于这些传输。

当发生较大的字节不变的大端字节传输时,数据的传输是这样的:

– MS字节被传输到传输地址

– 递减的高位字节被传输到顺序递增的地址。

Note

这是字节不变的大端和小端组件之间的关键区别。

6.2.3 Word-invariant big-endian

当一个字不变的大端格式元件访问一个字节时,下面的公式显示使用哪些数据总线位:

Address_Offset=Address–(INT(Address/Data_Bus_Bytes))× Data_bus_Bytes

Word_Offset=(INT(Address_Offset/4)) × 4

Byte_Offset = Address_Offset – Word_Offset

数据在DATA[(8 × (Word_Offset + 3 – Byte_Offset)) + 7 : 8 × (Word_Offset + 3 – Byte_Offset)]上传输。

对于32位总线,Word_Offset总是0,因此方程简化为:

DATA[(8 × (3 – Byte_Offset)) + 7 : 8 × (3 – Byte_Offset)]

Note

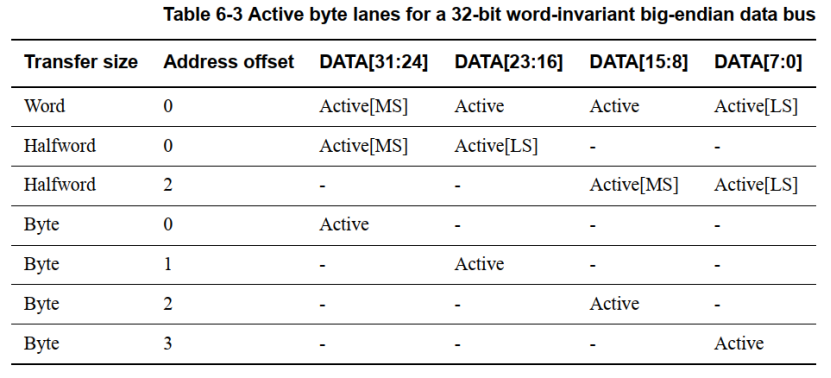

这显示了字不变的大端和小端格式组件之间的关键区别。与小端和字节不变的大端组件相比,字不变的大端组件使用不同的数据总线位来传输字节数。

对于使用字不变大端格式的半字和字传输,数据的传输是这样的:

– 最高字节位被传送到传送地址。

– 递减的高位字节被转移到顺序递增的地址。

对于使用字不变大端格式的大于一个字的传输,数据被分割成字大小的块:

– 最低位字节被传输到传输地址。

– 递增的字位被传输到递增的地址。

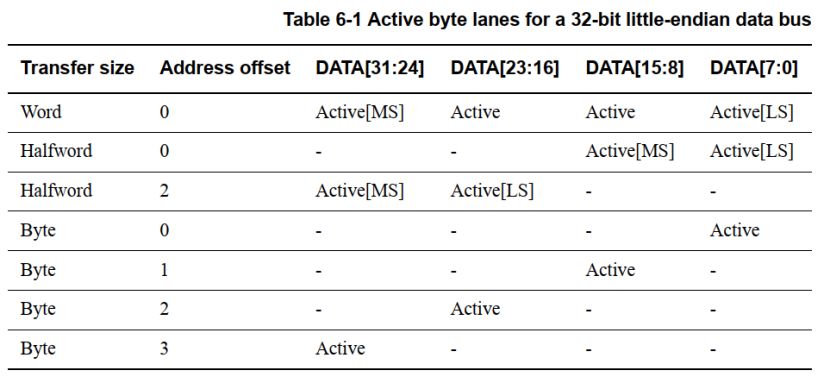

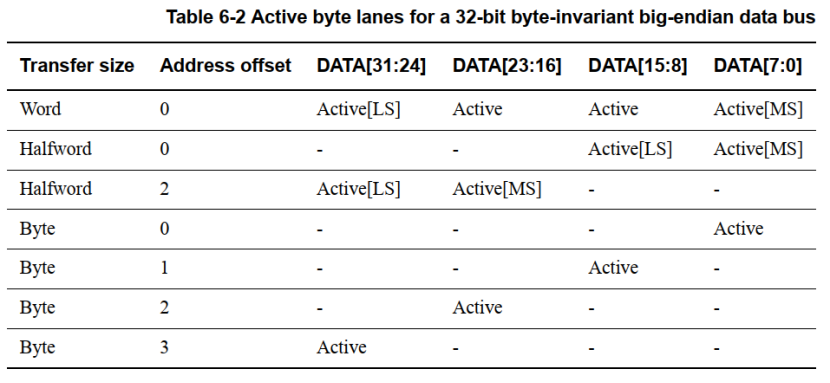

表6-1、6-63页的表6-2和6-63页的表6-3中的32位数据总线可以扩展为更宽的数据总线实现。

传输大小小于数据总线宽度的突发传输对于突发的每个节拍有不同的有效字节通道。

第6-63页的表6-1和表6-2显示了在小端或字节不变的大端系统中有效的32位总线上的字节通道。在这两种情况下,有效的字节通道是相同的,但最高有效字节和最低有效字节的位置不同。

表6-3显示了32位总线上有效的字不变大端系统的字节通道。

6.2.4 Byte invariance

字节不变大端数据结构的使用简化了对单一内存空间中混合端数据结构的访问。

使用字节不变的大端和小端格式意味着,对于数据结构中的任何多字节元素:

– 该元素使用相同的连续内存字节,而不考虑数据的大小端。

– 大小端决定了这些字节在内存中的顺序,这意味着它决定了内存中的第一个字节是元素的MS字节还是LS字节。

– 到给定地址的任何字节传输都将同一数据总线上的8位数据传递到相同的地址位置,而不考虑字节所在的数据元素的字节顺序。

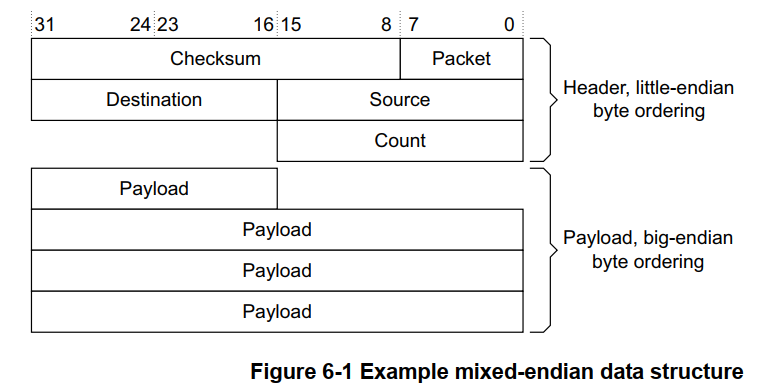

图6-1展示了一个需要字节不变访问的数据结构示例。在这个例子中,报头字段使用小端顺序,而数据负载使用大端顺序。

例如,在这个结构中,Count是一个两字节的小端元素,这意味着它的最低地址是它的LS字节。字节不变性的使用确保了对负载的大端访问不会破坏小端元素。

6.3 Data bus width

在不增加操作频率的情况下提高总线带宽的一种方法是使片上总线的数据路径更宽。 金属层的增加和嵌入式DRAM等大型片上内存块的使用是鼓励更宽片上总线使用的驱动因素。

指定总线的固定宽度意味着,在许多情况下,总线的宽度对应用程序来说不是最佳的。因此,采用了一种方法,使总线宽度具有灵活性,但仍然确保模块在设计之间具有高度可移植性。

该协议允许数据总线宽度为8、16、32、64、128、256、512或1024位。 但是,建议使用最小32位的总线宽度。 256位的最大总线宽度对于几乎所有的应用都是足够的。

对于读和写传输,接收模块必须从总线上正确的字节通道中选择数据。不需要跨所有字节通道复制数据。

以下部分将介绍:

– 在宽总线上实现窄从从机.

– 在6–66页上在窄总线上实现一个宽从机

– 在6-66页实现宽总线上的主机

6.3.1 Implementing a narrow slave on a wide bus

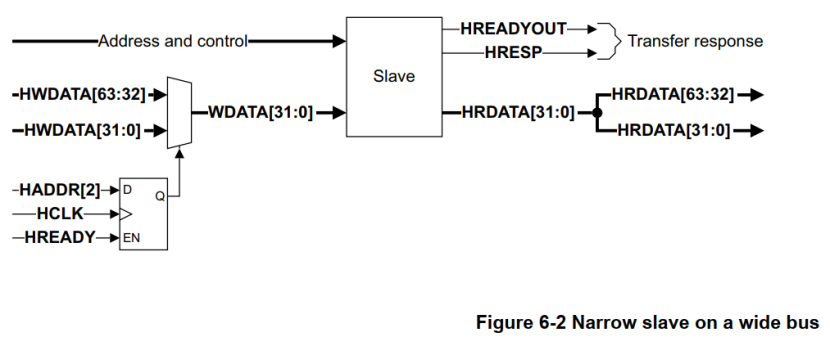

图6-2显示了原本设计用于32位数据总线的从机模块如何转换到64位总线上操作。这只需要添加外部逻辑,而不需要进行任何内部设计更改,因此该技术适用于硬宏单元格。

对于输出,当将窄总线转换为宽总线时,请执行以下操作之一:

– 在宽总线的两个半宽总线复制数据,如图6-2所示。

– 使用附加逻辑确保只更改适当的一半总线部分。这导致了电力消耗的减少。

从机只能接受与其自然接口一样宽的传输。如果主机尝试的传输宽度超过了从机的支持范围,那么从机可以使用ERROR传输响应。

6.3.2 Implementing a wide slave on a narrow bus

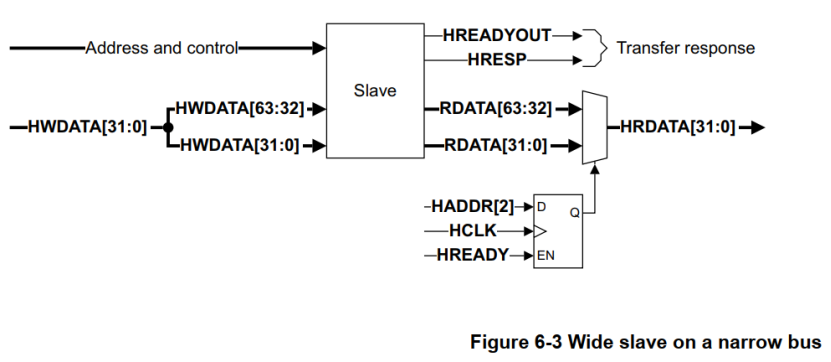

通过使用外部逻辑,预先设计或导入的从机可以适应在较窄的数据总线上工作。图6-3是在窄总线上实现的宽从机。

6.3.3 Implementing a master on a wide bus

主机可以被修改为工作在比原来更宽的总线上,就像从机被修改为工作在更宽的总线上一样。通过:

– 输入总线复用。

– 复制输出总线。

Note

主机不能在比最初计划的更窄的总线上工作,除非在主机中包含某种机制来限制主机尝试的传输宽度。主机绝不能尝试在HSIZE指示的宽度比它连接的数据总线宽的地方进行传输。

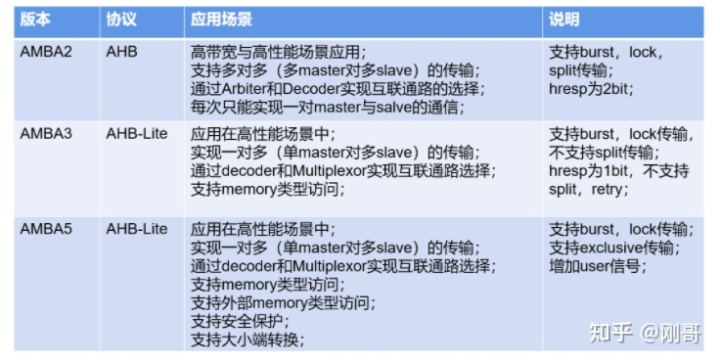

![[接口-AMBA-AHB] AHB总线协议](https://img-blog.csdnimg.cn/img_convert/e098d2c6dcdb7f04841794c7238d79d0.png)