AHB协议总结

- AHB协议学习

- 1. AHB简介

- 2. AHB的接口信号

- 2.1 Global signals

- 2.2 Master signals

- 2.3 slave signals

- 2.4 decoder signals

- 2.5 multiplexor signals

- 3. 传输

- 4. Decoder

- 5. Multiplexor

- 6. 大小端Endianness:

- 7. Exclusive transfer

AHB协议学习

1. AHB简介

AHB(Advanced Hight-performance Bus)是AMBA(Advanced Microcontroller Bus Architecture)协议中的一个。下面对AHB5/AHB-Lite协议进行简单介绍。

AHB总线为高速,高性能总线。具有以下特点:流水线操作;可支持最多16个总线主设备;支持burst传输;总线带宽为8/16/32/64/128bits(建议最小总线宽度为32位);上升沿出发操作。对于一个新的设计建议使用AHB总线接口。

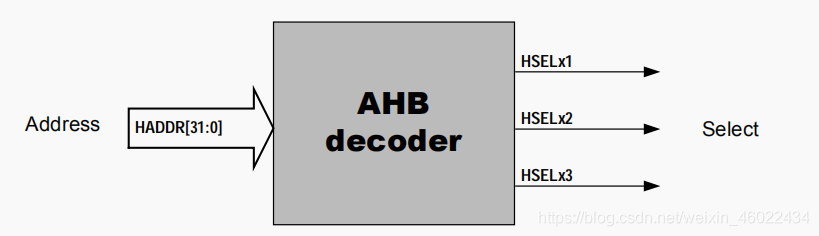

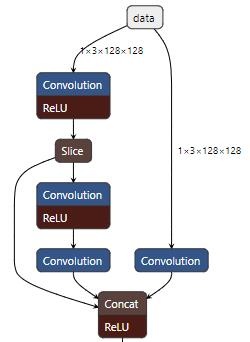

AHB的组成部分有:主设备master,从设备slave,译码器decoder,多路转换器multiplexor。Master,用来初始化一次读/写操作,某一时刻只允许一个主设备使用总线;slave,响应一次读/写操作,通过地址映射来选择使用哪一个从设备; decoder,通过地址译码来决定选择哪一个从设备;multiplexor,由decoder提供控制,选择将那个从设备的response信号送给master。如下图为AHB的结构图。

每次传输包括两个阶段:Address phase,只有一个cycle; Data phase,一个或者更多cycles,由HREADY信号决定需要几个cycle。AHB是流水线传输,先是地址周期,然后是数据周期。

2. AHB的接口信号

将AHB信号分为五类:global信号,master interface,slave interface, decoder signals,multiplexor signals。AHB信号的前缀为“H”。

2.1 Global signals

| 名称 | 来源 | 描述 |

|---|---|---|

| HCLK | clock source | PCLK上升沿,进行传输 |

| HRESETn | reset | 复位信号,低有效,直接接系统总线的reset信号 |

2.2 Master signals

| 名称 | 来源 | 描述 |

|---|---|---|

| HADDR[31:0] | Slave & Decoder | 32位系统地址总线 |

| HBURST[2:0] | Slave | Burst类型。 3’b000: SINGLE (单个传输burst) 3’b001: INCR (未定义长度的incrementing burst) 3’b010: WRAP4 (4拍wrapping burst) 3’b011: INCR4 (4拍incrementing burst) 3’b100: WRAP8 (4拍wrapping burst) 3’b101: INCR8 (4拍incrementing burst 3’b110: WRAP16 (4拍wrapping burst) 3’b111: INCR16 (16拍incrementing burst) |

| HMASTLOCK | Slave | 当为高的时候,表示当前的传输为locked sequence的一部分,该sequence不可分割,slave不能在sequence中间插入任何操作。它与地址和控制信号同步的。 |

| HPROT[3:0] | Slave | Memory types HPROT[0] data/inst (1:data access , 0:instruction fetch) HPROT[1] privileged特权位 (1: privileged access,0 :user access) HPROT[2] bufferable位 (1:write响应可以在中间点给出,0 :write响应必须在终点给出) HPROT[3] modifiable位 (1:传输特性可以被修改,0 :传输特性不能修改) HPROT[6:4] Slave HPROT[4] lookup位 (1: 传输必须在cache中查找,0 :传输不需要再cache中查找) HPROT[5] allocate位,性能相关 (1:传输被分配到cache,0 :传输没有被分配到cache) HPROT[6] shareable位 (1:传输与系统中其他masters共享,0 :传输没有与系统中其他masters共享) |

| HSIZE[2:0] | Slave | 数据传输的大小。(注意:transfer size必须小于等于数据总线的宽度) 3’b000: 8bits ; 3’b001: 16bits ; 3’b010: 32bits ; 3’b011: 64bits ; 3’b100: 128bits ; 3’b101: 256bits ; 3’b110: 512bits ; 3’b111: 1024bits |

| HNONSEC | Slave & Decoder | 安全传输相关。1:表示非安全传输 ,0:表示安全传输 |

| HEXCL | 独占访问monitor | 独占访问。。。 |

| HMASTER[3:0] | Slave & 独占访问monitor | Master标识符。。。 |

| HTRANS[1:0] | Slave | 传输类型。 2’b00 : IDLE 空闲 2’b01 : BUSY 忙 2’b10 : NONSEQ 非连续 2’b11 : SEQ 连续 |

| HWDATA[31:0] | Slave | 写数据总线,建议最小宽度为32bits |

| HWRITE | Slave | 传输方向。为高表示写传输,为低表示读传输 |

2.3 slave signals

| 名称 | 接收方 | 描述 |

|---|---|---|

| HRDATA[31:0] | Multiplexor | Slave的读数据总线 |

| HREADYOUT | Multiplexor | 为高,表示一次传输在总线上已经完成 |

| HRESP | Multiplexor | Slave提供给master的传输响应。0:传输状态为OKAY ,1:传输状态为ERROR |

| HEXOKAY | Multiplexor | 独占访问OKAY |

2.4 decoder signals

| 名称 | 接收方 | 描述 |

|---|---|---|

| HSELx | Slave | Slave选择信号,表示选择哪个slave |

2.5 multiplexor signals

| 名称 | 接收方 | 描述 |

|---|---|---|

| HRDATA[31:0] | Master | 读数据总线,从decoder中选择的。 |

| HREADY | Master & Slave | 当为高,表示先前的传输已经完成。HREADY为高并且HRESP是OKAY(HRESP=0),表示成功的完成一次传输。一般不建议slave插入超过16个wait状态,否则影响性能,但是对于boot ROM,系统启动时,性能可以忽略,此时可以使用大于16个wait状态。 |

| HRESP | Master | 传输响应 |

| HEXOKAY | Master | 独占访问OKAY |

3. 传输

读传输过程:

写传输过程

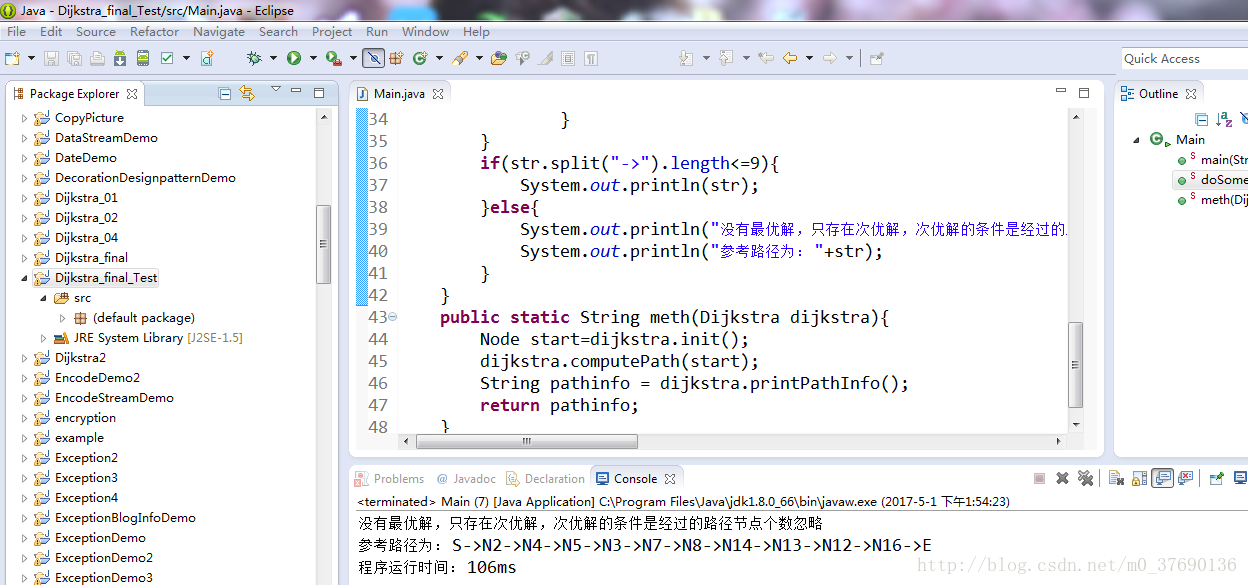

下图为三次不相关的传输

下面为一个4拍的incr读操作,第一拍传输类型为NONSEQ,如果期间master busy,则等到不busy时继续进行后面的传输,且后面的传输均为SEQ类型。

注:一次addr phase必须在成功检测到HREADY为高才能完成;

Wrap4

固定长度burst,busy后重新传输

未定义长度的burst,busy后,busy当拍丢掉

T3-T4,在HREADY为低的情况下slave返回ERROR,下一拍T4-T5,master将传输类型改为IDLE,在这一拍HREADY为高并返回ERROR。Slave返回ERROR时,允许地址在HREADY为低的情况下改变。

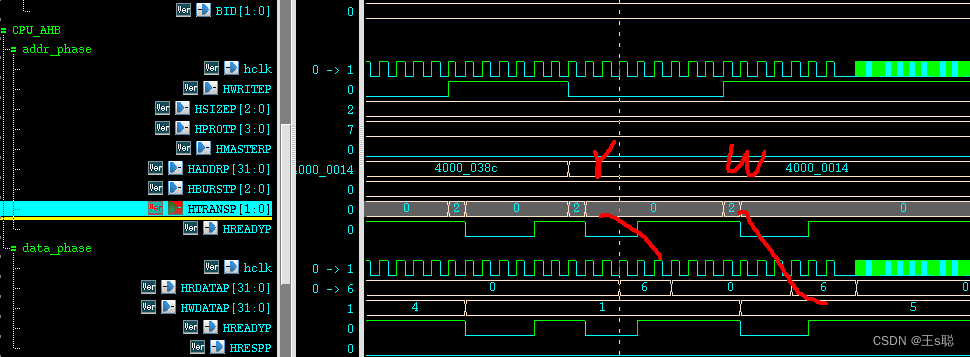

典型波形如下:

Addr=40000014, HTRANSP=NSEQ, 先读出数据为6,再写入数据为5,无论是addr phase还是dataphase, 都需看到HREADYP有效

4. Decoder

Decoder解码器用于产生HSELx信号到各个slave,decoder只负责解码,是纯粹的组合电路。

每个slave最小的地址空间有1KB,decoder最多只需要对22位地址进行解码,当master发burst传输时,address不可以跨越1KB边界,当需要跨越时,则需要将该transfer分为两次发。

5. Multiplexor

读数据和响应多路转换器

6. 大小端Endianness:

BE8 : Byte-invariant big-endian (字节不变大端,8bits)

BE32: Word-invariant big-endian (字不变大端,32bits)

Little endian ()

the Most Significant (MS) and the Least Significant (LS)

下面是大端小端的存储形式,

7. Exclusive transfer

HEXCL信号,表示独占传输

对于一个独占传输,有如下约束:

必须有一个single数据传输;

burst类型(HBURST)必须为SINGLE或INCR;

必须不能包含BUSY传输;

地址与数据大小对齐;

HPROT信号必须满足,独占访问monitor对该transfer有可见性。

HNONSEC 为non-secure

注意:如果exclusive access monitor在系统cache之后,传输必须为non-cacheable;如果在系统cache之前,则允许传输为cacheable。