文章目录

- 概述

- 特点

- AHB的组成

- 单个master的AHB lite结构

- 多个master的AHB lite结构

- 结构1

- 结构2

- AHB lite基本信号

- 1.系统信号

- 2.master

- 3.slave信号

- 4.译码器信号

- 5.多路器

- 信号详细解释

- HSIZE[2:0]

- HTRANS[1:0]

- HBURST[2:0]

- HREADY与HREADYOUT

- HRESP

- AHB基本传输

- 1.没有等待状态的单个传输

- 2.有等待状态的单个传输

- 3.多个传输的流水线操作

- 4.Burst传输

- 4.1增量Burst传输

- 4.2 回环Burst传输

- 什么是burst传输?

- 补充:

- 1.locked transfer

- 2.Exclusive transfer

- 3.HPROT

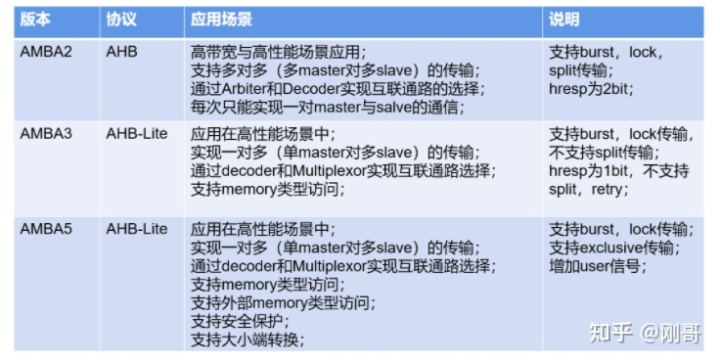

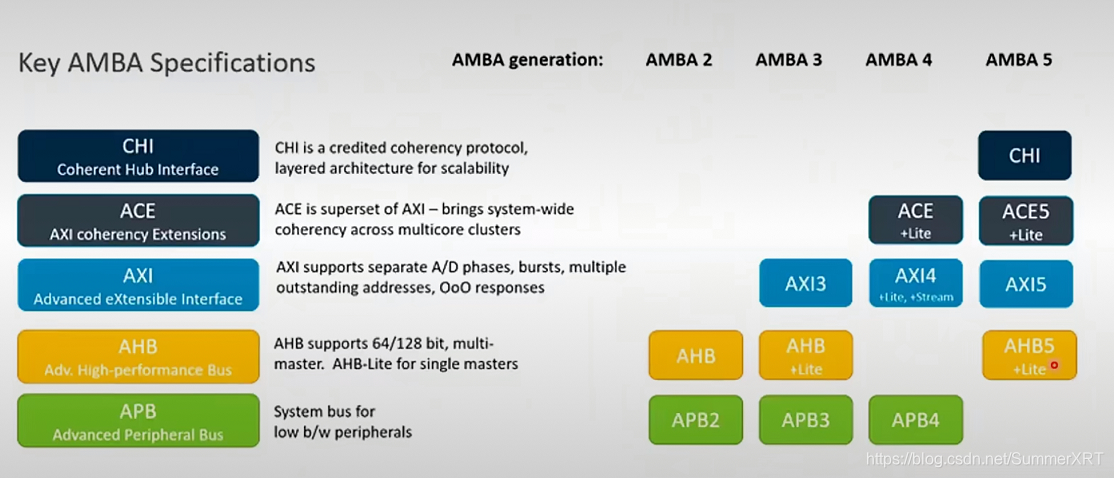

注:本文是基于讲解APB 5+ lite(轻量化的)版本,下图是AMBA的版本更新。

概述

AMBA高级处理器总线架构,不同的速率要求构成了高性能SOC设计的通信标准:

- AHB高级高性能总线

- APB高级外围总线

- AXI高级可拓展接口

AHB:主要是针对高速率、高频宽及快速系统模块所设计的总线,可以连接在如微处理器、芯片上或芯片外的内存模块和DMA等高效率总线;

APB:主要应用在低速且低频率的外围,可针对外围设备做功率消耗及复杂接口的最佳化;APB在AHB和低带宽的外围设备之间提供了通信桥梁,所以APB是AHB的耳机拓展总线;

AXI:高速度、高带宽、管道化互联、单向通道,只需要首地址、读写并行、支持乱序、支持非对齐操作、

特点

- 支持流水线操作(pipeline)

- 支持分裂传输

- 支持burst传输

- 支持多个master/slave设备连接

其他的可以看上图中的总结。

AHB的组成

- Maste(总线主机):能够发起读写操作,提供地址和控制信号。同一时间只有1个Master可以处于有效状态并能使用总线;

- Slave(总线从机):在给定的地址范围内对读写操作作响应,并对Master返回成功、失败或者等待等状态;

- Arbiter(仲裁器):负责保证总线上一次只有一个Master工作。仲裁协议是规定的,但是仲裁算法可以依据应用决定;

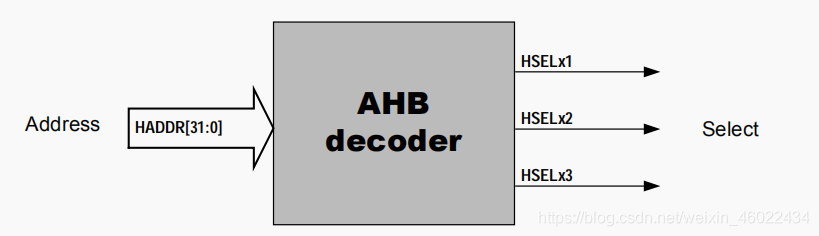

- Decoder(解码器):负责对地址进行解码,并提供片选信号到个Slave;

- 每个AHB都需要一个仲裁器和一个译码器。

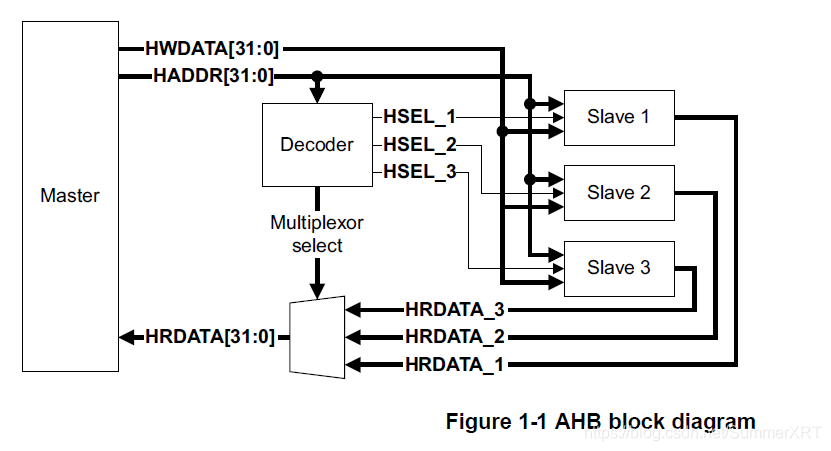

单个master的AHB lite结构

AHB是一个多master多slave的组成,而AHB lite(轻量化的)则是针对单个master对多个slave的设计。如下所示:

要注意的是:

- salve的地址空间要以1 KB为单位,地址空间最好要1 KB对齐。

- AHB lite虽然是针对单个master的,所以设计时可以省去arbiter。但这并不是说整个系统不可以存在多个master的情况。如下所示。

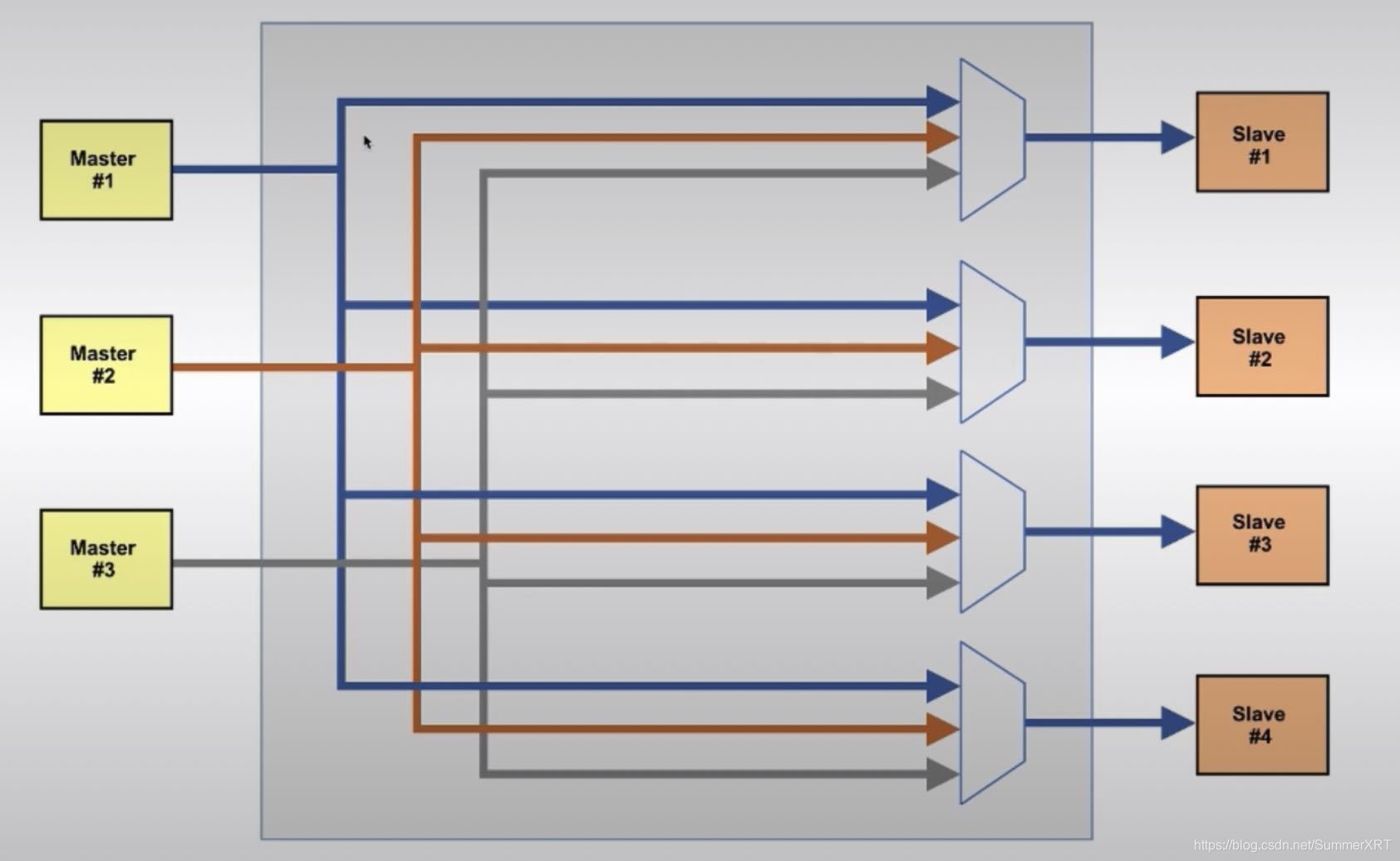

多个master的AHB lite结构

AHB 的结构比较灵活,以下是介绍的两种多master多slave的AHB lite扩展情况。

结构1

- 3个master,用3组对应的BUS去访问slave

- 每个slave的结构上都做一个 MUX (或者arbiter也行)对3个master发起的传输做一个选择

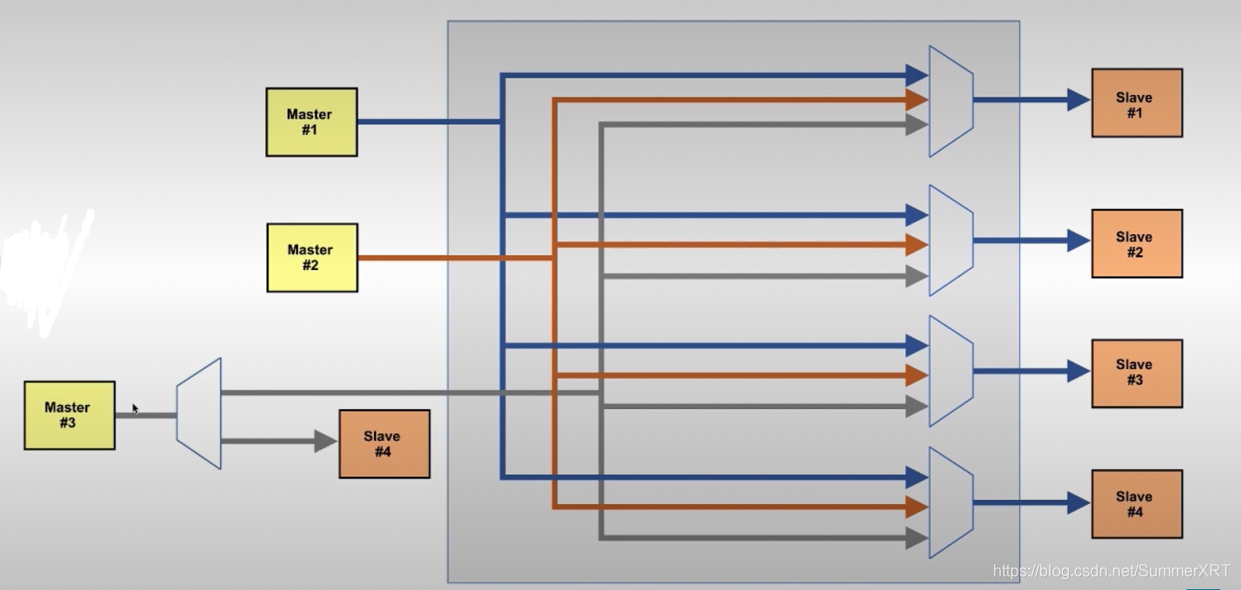

结构2

- 相对结构1 的变化就是,可以让一个slave4 独属于master3去访问,而master1和master2不能访问,那么这个slave4的访问速度就会比其他slave要快很多。

- 同理也可以在右测进行slave的扩展。

AHB lite基本信号

PS:这里只解释常用的信号。

1.系统信号

| 信号 | 来源 | 描述 |

|---|---|---|

| HCLK | 时钟源 | 时钟信号,上升沿采样 |

| HRESETn | 系统总线 | 复位信号,低有效 |

2.master

| 信号 | 目标处 | 描述 |

|---|---|---|

| HADDR[31:0] | slave和译码器 | 32位系统地址总线 |

| HTRANS[1:0] | slave | 传输类型。包括类型有 , NONSEQ:连续传输的首个数据传输类型;SEQ:连续传输的中间数据);IDLE:空闲周期;BUSY:准备发送数据,但是master还没准备好发,歇一歇,但是busy很少用 |

| HWRITE | slave | 传输方向,信号为高(1)时为写操作,为低(0)时表示读操作 |

| HSIZE[2:0] | slave | 单次传输的数据位宽,000~111分别对应不同的数据包大小,000对应8位(1 Byte),010对应1 word(4 Byte),111对应1024位 |

| HBURST[2:0] | slave | 传输的burst(突发)类型,包括SINGLE(单个)、递增突发(如INCR4为连续发起4个数据)和 回环突发(WRAP4、WRAP8和WRAP16) |

| HWDATA[31:0] | slave | 写数据总线,从Master到Slave |

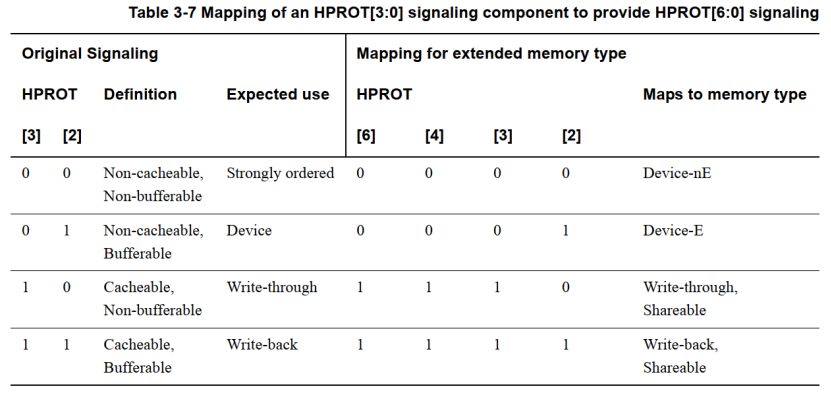

| HPROT[3:0] | slave | 保护控制信号 ,指示传输是操作码获取还是数据访问,以及传输是特权模式访问或用户模式访问。要求slave具有保护功能,一般不使用 |

注:ABMA5中新增一下信号:

- HMASTLOCK信号,若为高则开启lock 传输。

- HEXCL和HMASTER[3:0]信号,用以设置Exclusive Transfer,设计中需要有一个Exclusive Access Monitor。

- HNONSEC信号,指示当前传输是否是个secure或non_secure传输。

- HPROT[6:4] 用来增加扩展的memory type。

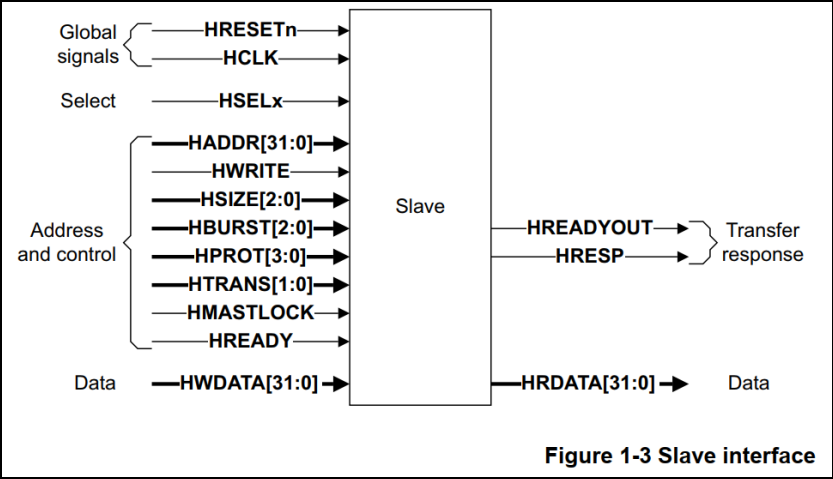

3.slave信号

| 信号 | 来源 | 描述 |

|---|---|---|

| HRDATA[31:0] | 多路器 | 读数据总线,从Slave读到Master |

| HREADYOUT | 多路器 | 为高时则结束传输,为低则延迟传输时间 |

| HRESP | 多路器 | 传输响应信号,经过多路器处理,给master反馈传输状态。为高时表示传输状态为ERROR,为低时则表示传输状态为OKAY |

注:AMBA5中增加了HEXOKAY信号,用来表示Exclusive Transfer的成功或失败状态,经过多路器处理,返回给master。

4.译码器信号

| 信号 | 来源 | 描述 |

|---|---|---|

| HSELx | slave | 从机选择信号。由译码器控制,每个Slave都有自己独立的从机控制信号,表示当前传输是否发送给选择的从机 |

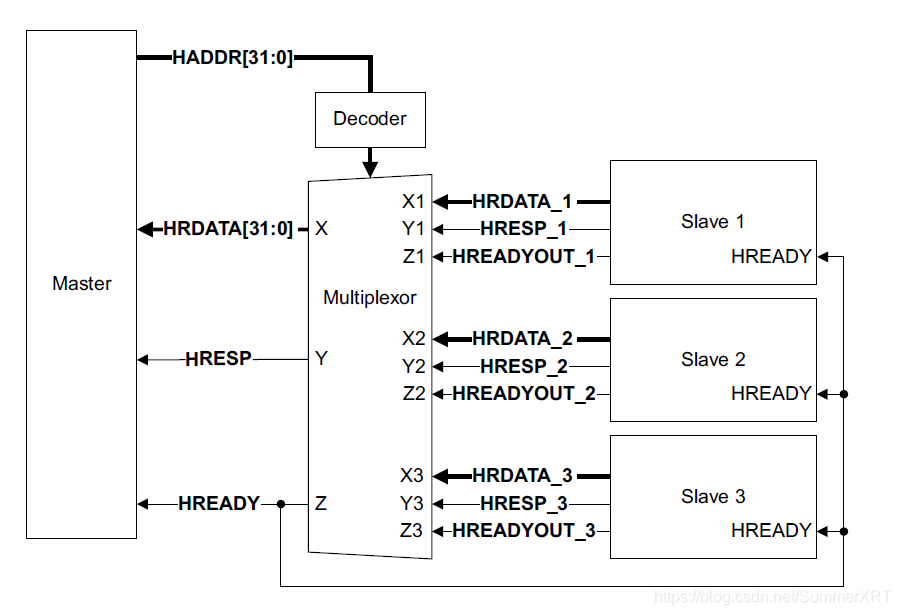

5.多路器

| 信号 | 来源 | 描述 |

|---|---|---|

| HREADY | master和slave | 为高时表示master和所有slave的当前传输结束 |

| HRDATA | master | 从slave读取的数据 |

| HRESP | master | slave的传输响应信号,经过MUX选择 |

注:AMBA 5中增加了HEXOKAY信号,返回给master。

信号详细解释

HSIZE[2:0]

- HSIZE的信号的所代表的每笔数据包的数据宽度,如下表:

| HSIZE[2:0] | 数据包长度 |

|---|---|

| 000 | 8 bit \ 1 Byte |

| 001 | 16 bit \ 2 Byte ,按半字传输 |

| 010 | 1 word \ 32 bit \ 4 Byte ,按字传输 |

| 011 | 2 word \ 64 bit |

| 100 | 128 bit |

| 101 | 256 bit |

| 110 | 512 bit |

| 111 | 1024 bit |

HTRANS[1:0]

- HTRANS[1:0] 包含传输类型的含义,包含:IDLE 、BUSY 、NONSEQ 和 SEQ。

| HBURST[2:0] | TRANS类型 | 描述 |

|---|---|---|

| 00 | IDLE | 空闲周期 |

| 001 | BUSY | 准备发送数据,但是master还没准备好发,歇一歇,但是busy很少用 |

| 10 | NONSEQ | 连续传输的首个数据传输类型 |

| 11 | SEQ | 连续传输的中间数据数据类型 |

HBURST[2:0]

| HBURST[2:0] | Burst类型 | 描述 |

|---|---|---|

| 000 | single transfer | 单个传输,HTRANS是NONSEQ或IDLE |

| 001 | INCR | 地址从开始地址开始递增,突发长度不固定 |

| 010 | WRAP4 | 突发4位,地址递增回环 |

| 011 | INCR4 | 突发4位,地址递增 |

| 100 | WRAP8 | 突发8位,地址递增回环 |

| 101 | INCR8 | 突发8位,地址递增 |

| 110 | WRAP16 | 突发16位,地址递增回环 |

| 111 | INCR16 | 突发16位,地址递增 |

注意:

- INCR类型(递增)和WRAP类型(回环)的Burst时,发送的地址值不能跨过1KB的地址空间。因为每个slave的地址值在设计时,都是以1 KB为单位,如果burst发送的地址空间跨过1KB边界时,有可能就导致地址译码出错,访问了另外一个slave。

- WRAP类型的Burst主要用于CPU中有cache line需要填充。

PS:WRAP起始地址位置的确定?

起始地址根据cache line的大小确定。每个cache line完全是在一个突发读操作周期中进行填充或者下载的,即使CPU只存取1bit的存储器数据,cache也会启动整个存取器访问周期并请求整个数据块。cache line的每条line的地址总是burst length的倍数。比如,cache line是由8个word组成,即4 x 8word = 32 Byte = 256 bit ,所cache line的各条line的起始地址是按加16’h20递增的,即 0x00 、0x20、0x40、0x60、0x80…,

HREADY与HREADYOUT

- 如果单个master对单个slave,那HREADYOUT要与HREADY相连,然后把HREADY接到master和slave上。

- 如果是单个master对多个slave,那就要把各个slave的HREADYOUT通过一个MUX,产生HREADY相连,然后把HREADY接到master和各个slave上。

注意:上图所示,如果slave1没完成transfer,slave2和slave3完成,那么此时slave2和slave3要等待slave1完成后,才能接收下一个transfer。

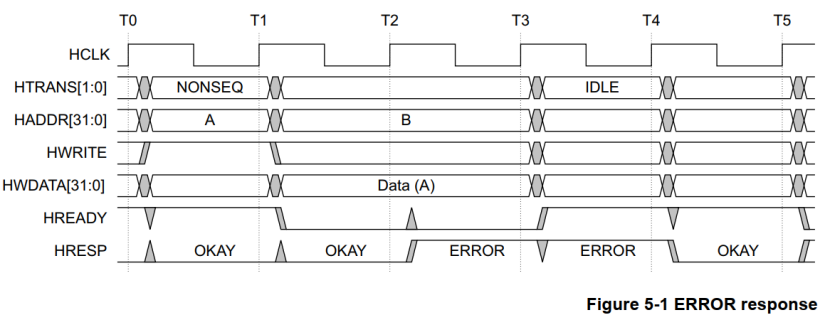

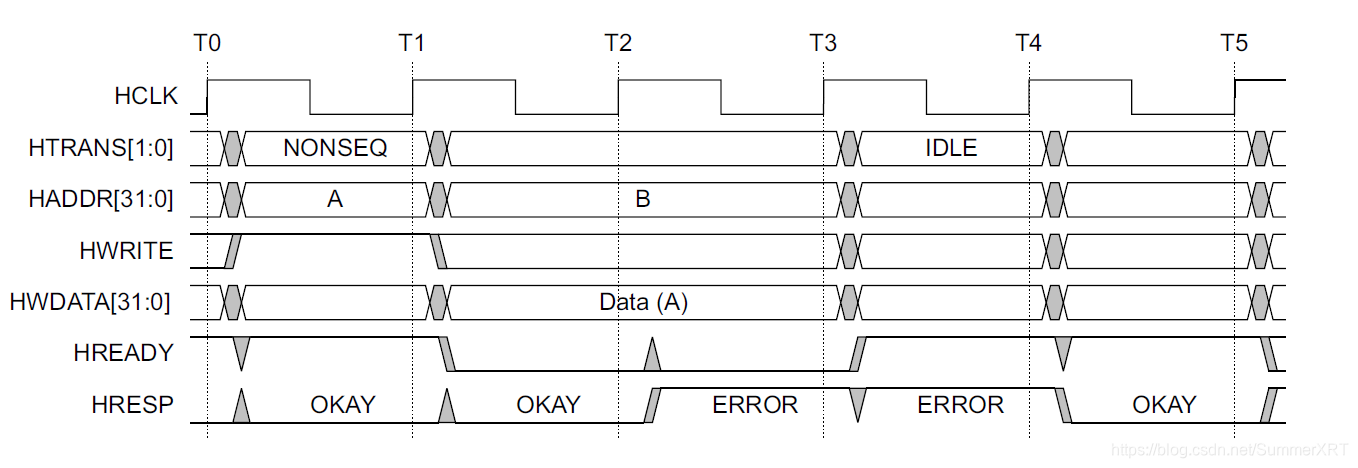

HRESP

1.为低时表示 OKAY 。传输完成(HREADY为高)

2. 为高时表示ERROR。但必须是两个clk周期完成,目的是给master来选择是否结束当前burst,还是在返回error的情况下继续进行传输。

注意:这里要与AHB 2版本区分,AHB 2中HRESP[1:0],有OKAY、ERROR、RETRY、SPLIT四种传输状态。

如果master收到error后,master要取消BURST传输,如下时序图,:

- T0 - T1:发送地址A

- T1 - T2:hready为低,发送地址A

- T2 - T3:地址A出错,HRESP拉高,发送一拍ERROR给master;

- T3 - T4:master决定结束当前burst,并舍弃当前传输A。然后把HREADY拉高,发送IDLE,继续维持HRESP为高一拍

- T4 - T5:结束当前burst传输。

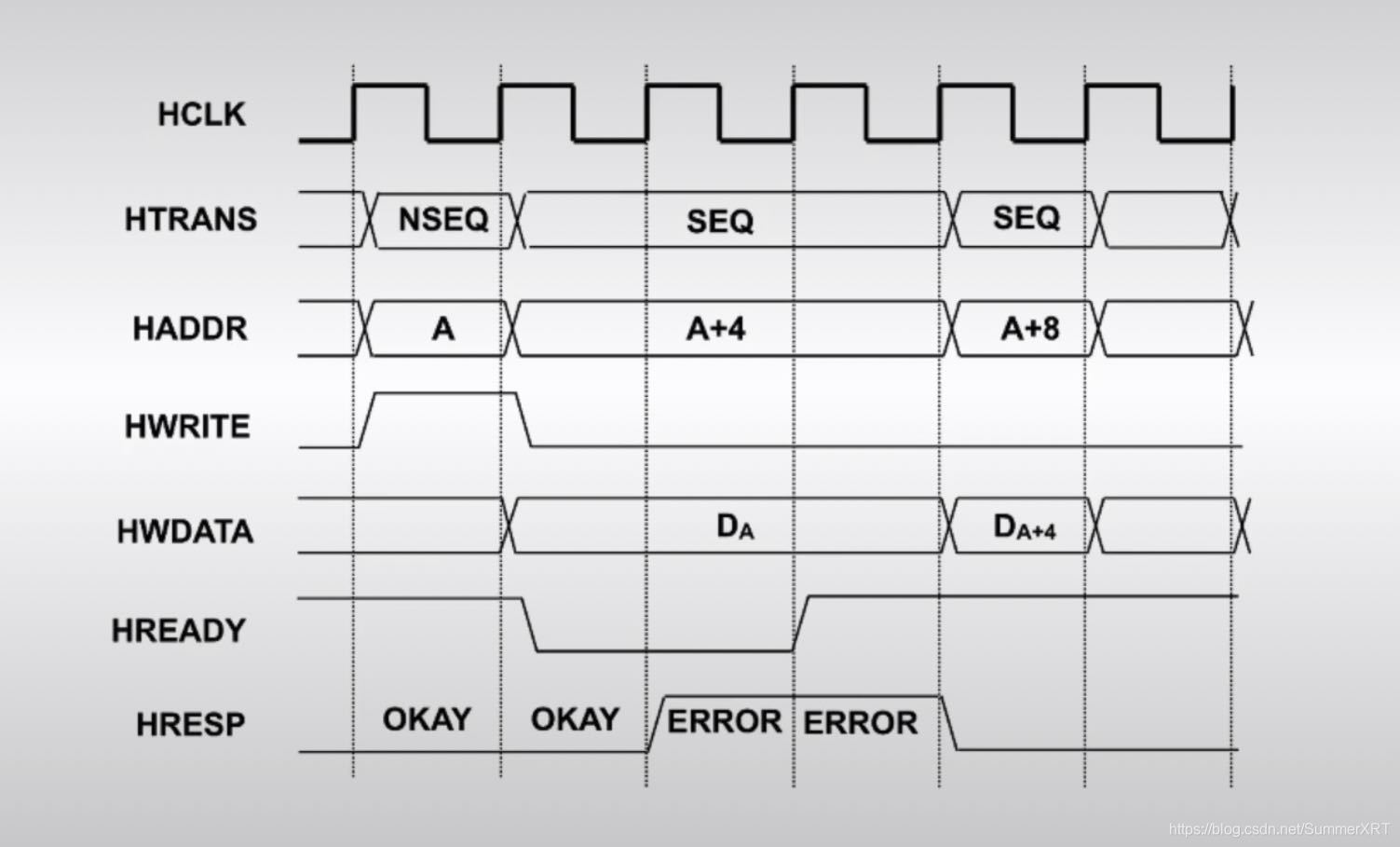

如果master收到error后,master仍然继续burst传输的时序图,时序如下:

- 跟上面不同的是,尽管传输A出错了,将传输A舍弃后,发送一个SEQ,继续后面的A+4、…的burst传输。

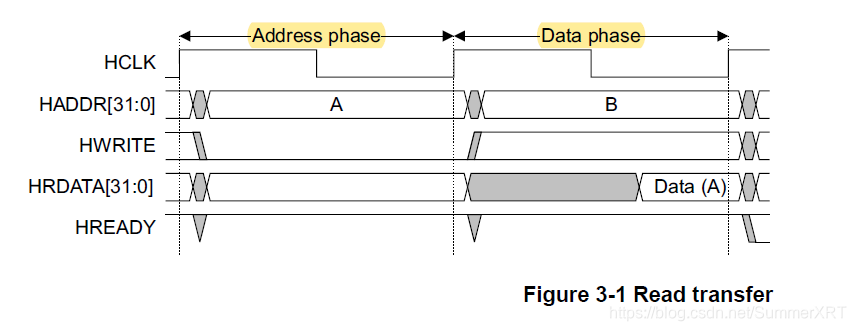

AHB基本传输

- 具有两个阶段:地址周期和数据周期;

- 地址周期(AP),只有一个周期;

- 数据周期(DP),由HREADY信号决定需要几个周期;

- 支持流水线传送;

- 遵循先是地址周期,然后是数据周期。

- 有效的写入和读出数据都发生在HREADY信号拉高的周期里。

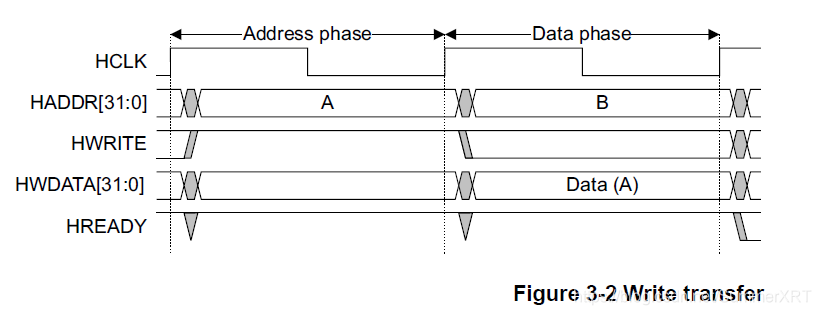

1.没有等待状态的单个传输

读操作:

写操作:

图解:HREADY信号在地址周期后拉高,开始数据传输。

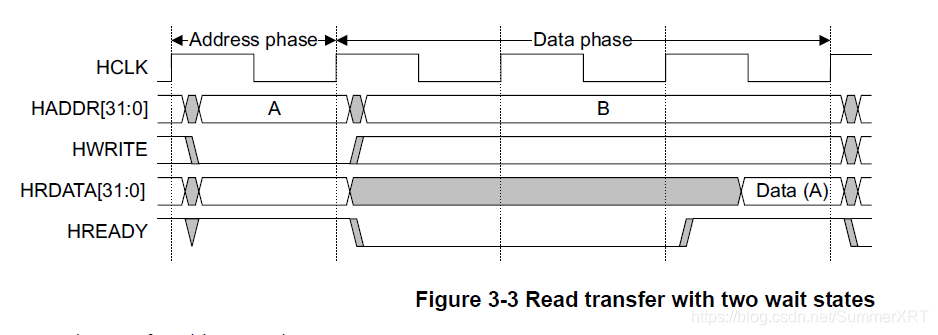

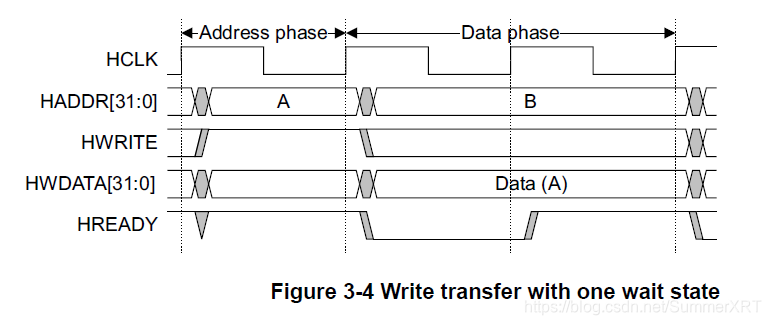

2.有等待状态的单个传输

slave可能存在不能及时处理master传输的数据,这时需要让master稍微等一等,需要slave插入一些等待的状态。

图解:HREADY信号在第二和第三周期拉低了,并没有直接拉高。因为传输只有在HREADY信号为高时才有效,所以此时master会等待2个周期。

注意:

- 如果是写入数据,那么些数据线在HREADY信号为低的阶段要保持不变,一直都传输完成

- 如果是读出数据,那么只有在HREADY信号拉高后,数据才会到总线上。

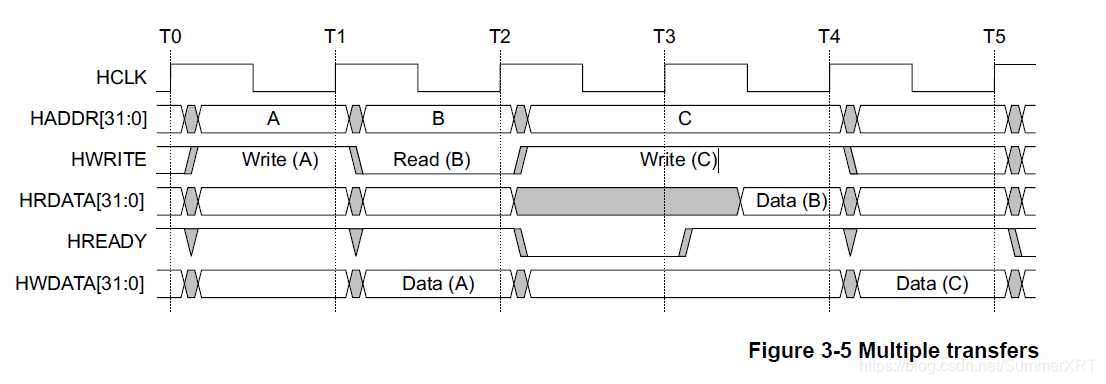

3.多个传输的流水线操作

当总线上有多个未处理完的请求时,也就是当A请求被master执行后,slave作响应期间,紧接着master又收到新的请求B,这是master就要执行流水线一样的操作,如下图所示:

图中的流水线操作:

- A和C是没有等待的写操作,B是有等待的读操作。

- 对地址B进行读操作时插入了等待,也影响了发送地址C的地址周期。

注意:

- AHB最多只允许总线上存在2个未处理完传输,因为AHB只有2个pipe。

4.Burst传输

AHB协议有两种突发模式:

-

增量突发(INCR):地址递增,在地址边界处不回环;

-

回环突发(WRAP):地址递增,但会在特定的地址边界上回环;一般在需要填充cache line的时候使用。

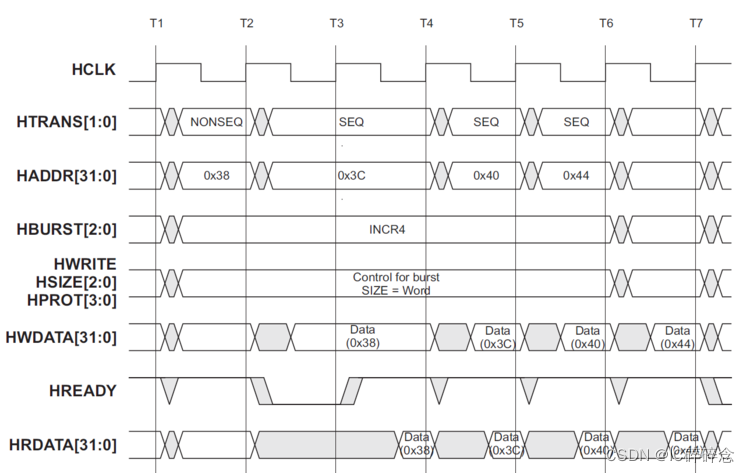

4.1增量Burst传输

有INCR、INCR4、INCR8和INCR16四种类型。

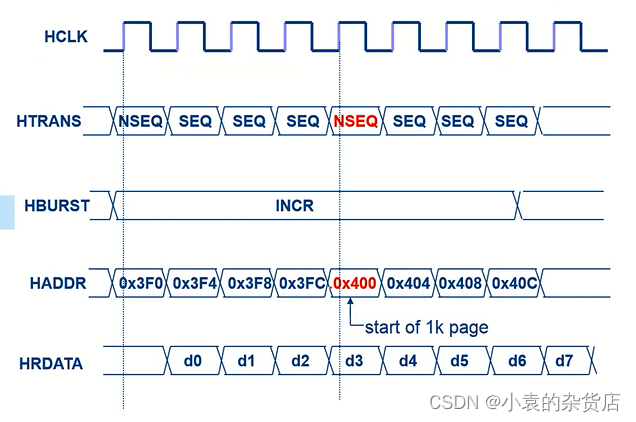

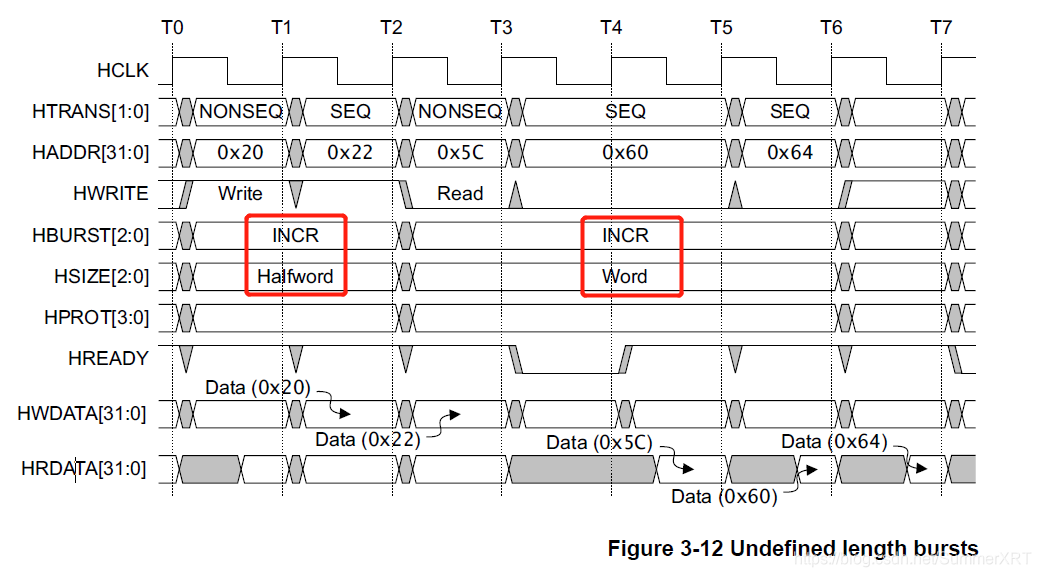

INCR类型如下:

图解:

- 图中HBURST指定的是INCR类型,地址连续递增,不指定突发长度;

- HTRANS中指定了NONSEQ(表示这是连续发送的数据里面的第一个数据)、BUSY(准备发送数据,但是还没准备好发)、SEQ(传输过程里面的数据);

- HTRANS信号指定为BUSY时,那一拍的数据就不会发送;

- 注意:地址的递增与HSIZE 有关,当HSIZE指定单个传输数据位宽为半字(16bit)时,地址是按每次加2递增。当HSIZE指定单个传输数据位宽为1个word(32bit)时,地址是按每次加4递增。

图解:地址在0x30并不回环,而是继续递增。

注意:

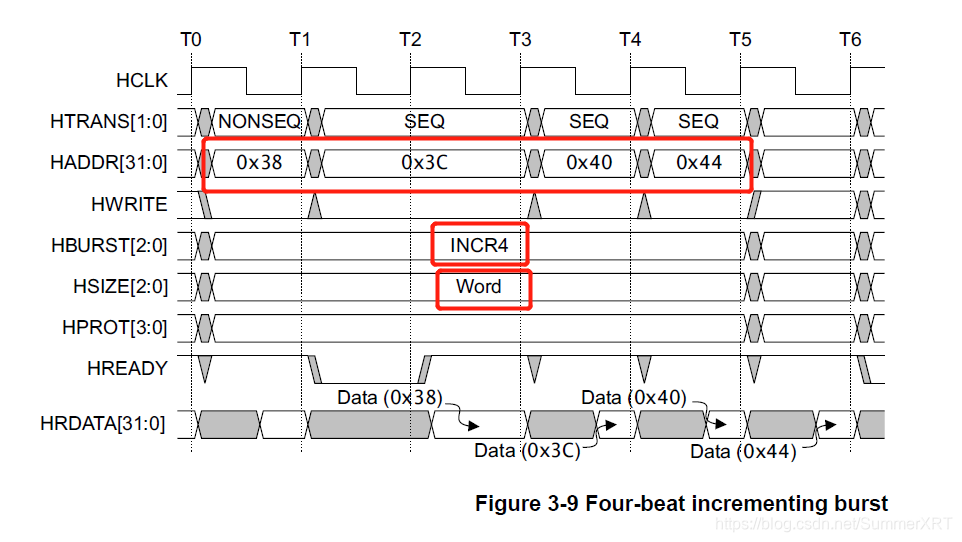

- HBURST指定的是INCR4类型,表示要连续发送4个数据;

- 地址的递增与HSIZE指定是有关的,因为HSIZE指定单次传输的位宽为1word,对应地址是每次加4.

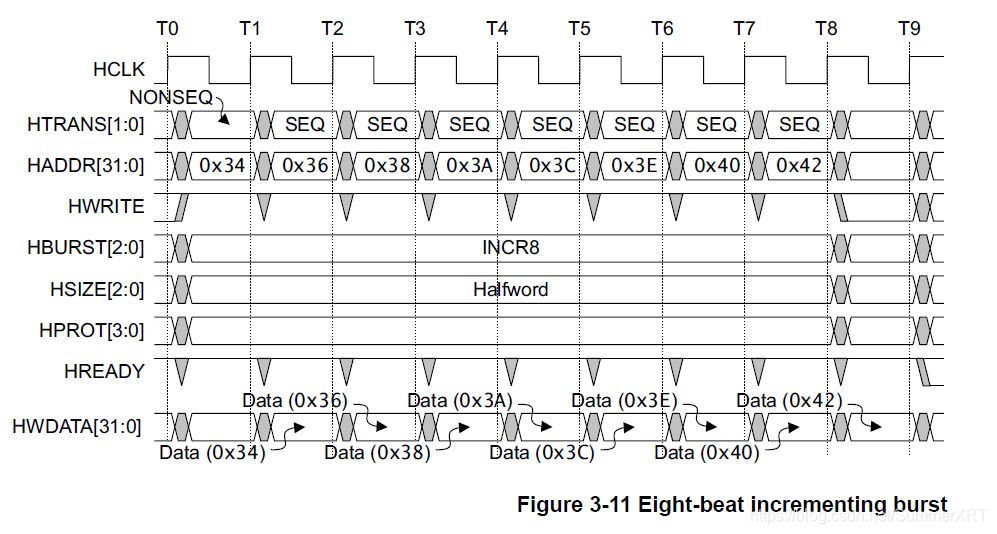

比如INCR8类型的burst传输,连续突发8个数据,地址递增,如下:

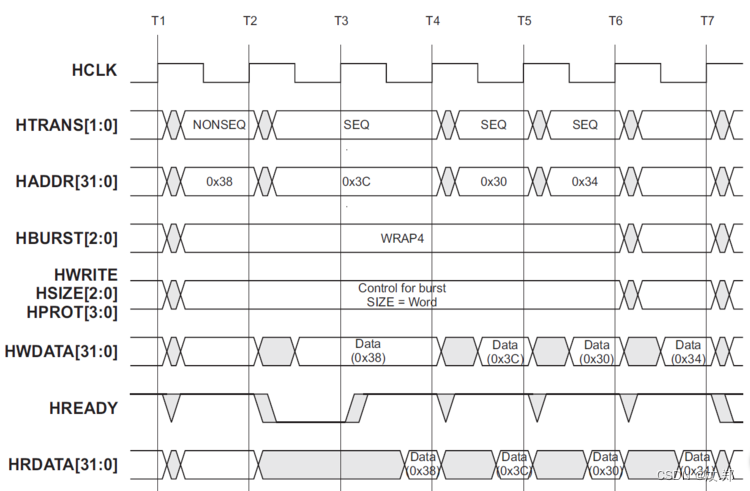

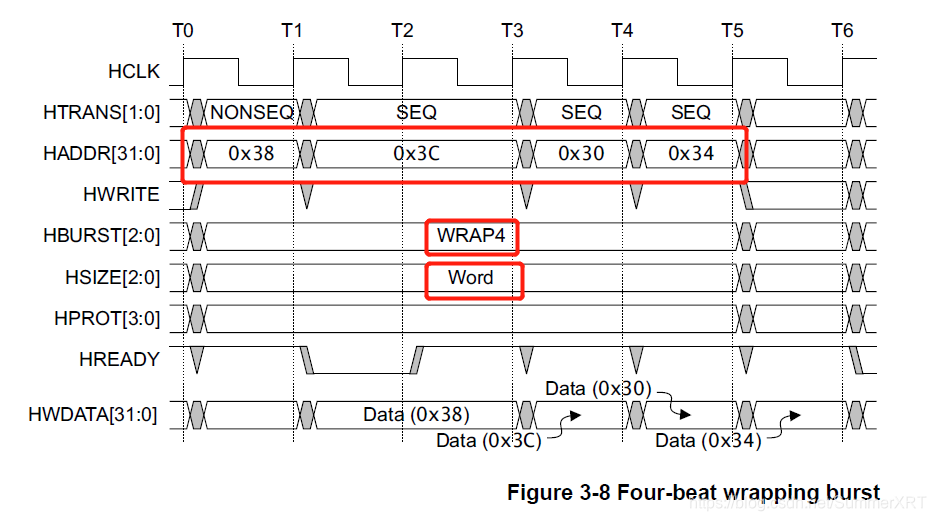

4.2 回环Burst传输

图解:

- 在0x3C地址之后,根据回环的地址边界,第四拍的地址变为0x30。4个地址(0x30、0x34、0x38和0x3c ),每个地址各不相同,这四个地址是一个回环范围。起始地址决定了回环操作的回环范围;

- 地址的递增与HSIZE指定是有关的,因为HSIZE指定单次传输的位宽为1word,对应地址是每次加4.

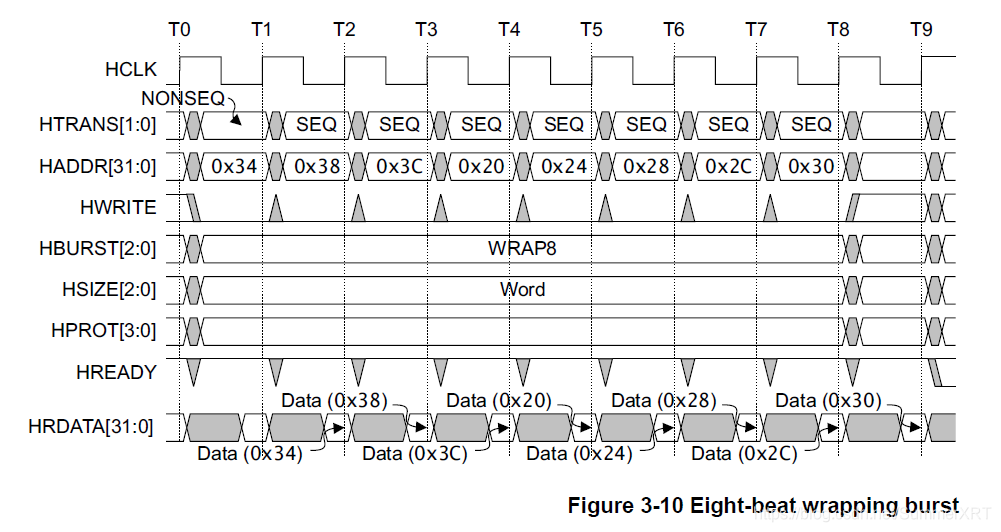

比如WRAP8类型的burst传输:

PS:解释一下什么是burst传输:

什么是burst传输?

突发(Burst):是指在同一行中相邻的存储单元连续进行数据传输的方式, 连续传输所涉及到存储单元(列)的数量就是突发长度 (Burst Lengths,简称BL)。 换成人能听懂的,就是地址只发一次,首个地址发出就决定了后面的地址是什么。而不是发送一个地址,再传一个数据的方式。

那么为什么要使用burst传输呢?

Burst传输就是提高了传输效率。如果不使用burst,普通访问模式下,主设备发出的传输命令到达从设备,由于仲裁等原因,传输会产生一定的延时。如果主设备读一个数据,处理一个数据的话,由于延时的存在,处理速度会极低。在进行突发传输时,只要发送一次地址,内存就会依次地自动对后面相应数量的存储单元进行读/写操作。而不再需要控制器连续地提供访问地址。所以,第一次数据的传输需要若干个周期,而其后每个数据只需一个周期的即可获得。

举例:

-

AHB协议需要一次突发传输的所有地址,地址与数据锁定对应关系,后一次突发传输必须在前次传输完成才能进行。

-

AXI只需要一次突发的首地址,可以连续发送多个突发传输首地址而无需等待前次突发传输完成,并且多个数据可以交错传递,此特征大大提高了总线的利用率。

补充:

1.locked transfer

- 也就是当某个master要执行一个原子操作(对同一个地址进行先读后写操作)时,如果有其他的master占用了总线,block住了原子操作,就会导致逻辑上的错误,读写不一致。这是为了返回有传输打断原子操作,就用一个locked transfer来保护。

- 但是这个操作会影响性能,用的比较少。

2.Exclusive transfer

AMBA5中新增的。

3.HPROT

AMBA5中HPROT信号由4位扩展到7位。