【2022.04西南交大数电实验】

【2022.04.17 更新修改了一个错误:

assign CO = (upd & (Q == 4'd9)) | (~upd & (Q == 4'd0) & ~clr);~clr改为了clr:

assign CO = (upd & (Q == 4'd9)) | (~upd & (Q == 4'd0) & clr);另外 ,把代码修得整齐好看了一点】

【代码参考博主weixin_49270464,已进行适当修改,符合实验要求。本代码及波形已通过老师验收。仅供参考。】

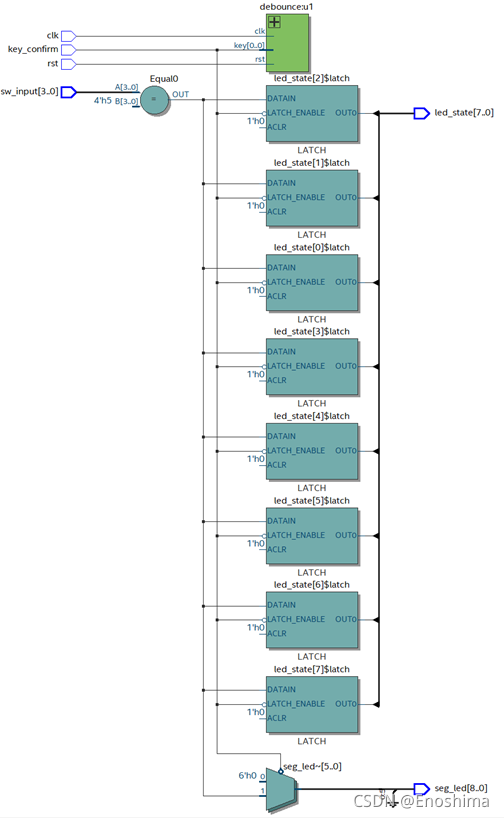

module yck_1716_3_1(codeout, Q, clkin, clr, CO, upd, en, load, data);input clkin, clr, upd, en, load;input [3: 0] data;output [6: 0] codeout;output [3: 0] Q;output CO; yck_1716_3_3(clkin, clr, Q, CO, upd, en, load, data);yck_1716_3_2(codeout, Q);

endmodule

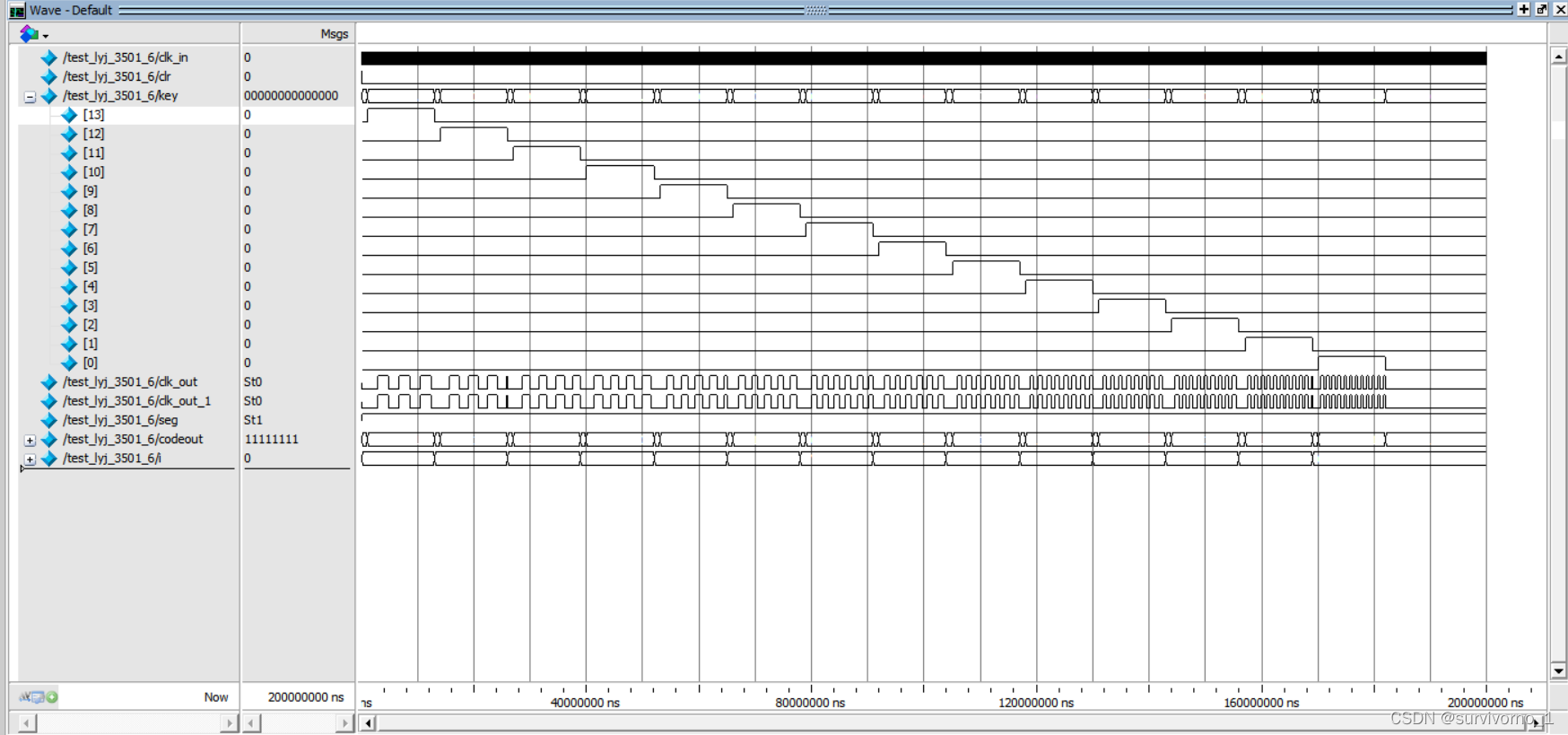

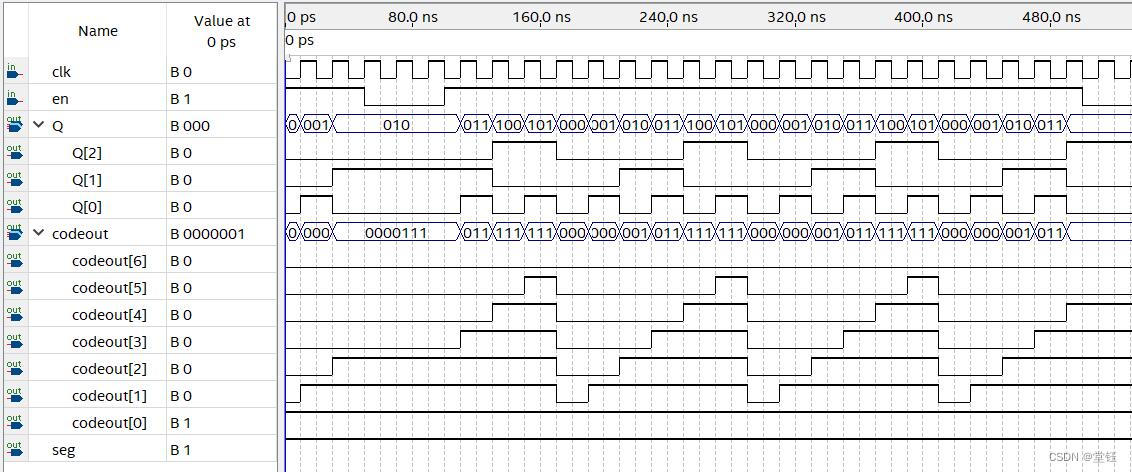

module yck_1716_3_3(clkin, clr, Q, CO, upd, en, load, data); //十进制计数器input clkin, clr, upd, en, load;input [3: 0] data;output [3: 0] Q;reg [3: 0] Q;output wire CO;always@(posedge clkin, negedge clr)if(!clr) //异步清零Q <= 4'd0;else if(!load) //同步置数(若为低电平则直接赋值,数码管显示本时刻数值)Q <= data;else if(en) //使能(en高电平)beginif(upd) //同步置数,加法计数(upd=1)beginif(Q == 4'd9)Q <= 4'd0;elseQ <= Q + 4'd1;endelse //同步置数,减法计数(upd=0)beginif(Q == 4'd0)Q <= 4'd9;elseQ <= Q - 4'd1;endendassign CO = (upd & (Q == 4'd9)) | (~upd & (Q == 4'd0) & clr); //(upd为高电平且Q为9)或者(upd为低电平且Q为0且clk为0)

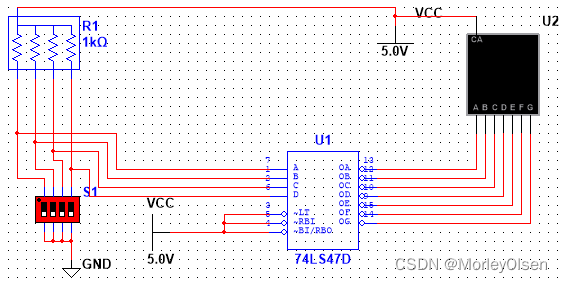

endmodulemodule yck_1716_3_2(codeout, Indec); //译码器input [3: 0] Indec;output [6: 0] codeout;reg [6: 0] codeout;always@(Indec)begincase(Indec) 4'b0000: codeout = 7'b1111110;4'b0001: codeout = 7'b0110000;4'b0010: codeout = 7'b1101101;4'b0011: codeout = 7'b1111001;4'b0100: codeout = 7'b0110011;4'b0101: codeout = 7'b1011011;4'b0110: codeout = 7'b1011111;4'b0111: codeout = 7'b1110000;4'b1000: codeout = 7'b1111111;4'b1001: codeout = 7'b1111011;default: codeout = 7'bx;endcaseend

endmodule

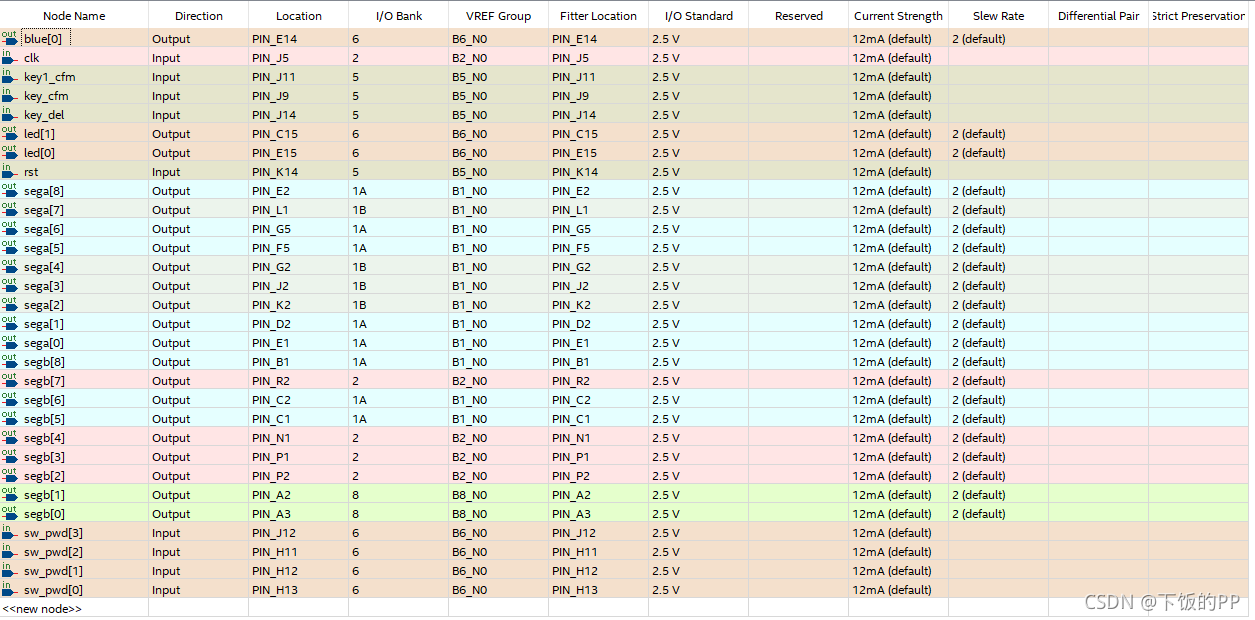

| 信号名 | 主板器件 | PIN | 信号名 | 主板器件 | PIN | |

| clr | SW0 | PIN_24 | codeout[3] | d | PIN_111 | |

| en | SW1 | PIN_31 | codeout[4] | c | PIN_104 | |

| upd | SW2 | PIN_30 | codeout[5] | b | PIN_100 | |

| load | SW3 | PIN_33 | codeout[6] | a | PIN_112 | |

| CO | IO4/LED4 | PIN_58 | clkin | CLK0 | PIN_88 | |

| q[0] | IO0/LED0 | PIN_46 | data[3] | SW7 | PIN_44 | |

| q[1] | IO1/LED1 | PIN_50 | data[2] | SW6 | PIN_39 | |

| q[2] | IO2/LED2 | PIN_52 | data[1] | SW5 | PIN_42 | |

| q[3] | IO3/LED3 | PIN_54 | data[0] | SW4 | PIN_32 | |

| codeout[0] | g | PIN_103 | ||||

| codeout[1] | f | PIN_110 | ||||

| codeout[2] | e | PIN_106 |

PS.注意实验箱是否故障,及时更换,不要浪费时间。