实验二 组合逻辑电路

一 实验目的

1 掌握组合逻辑电路的设计方法;

2 学习译码显示电路的应用。

二 实验内容

1 设计发电机控制电路

(1)逻辑抽象真值表

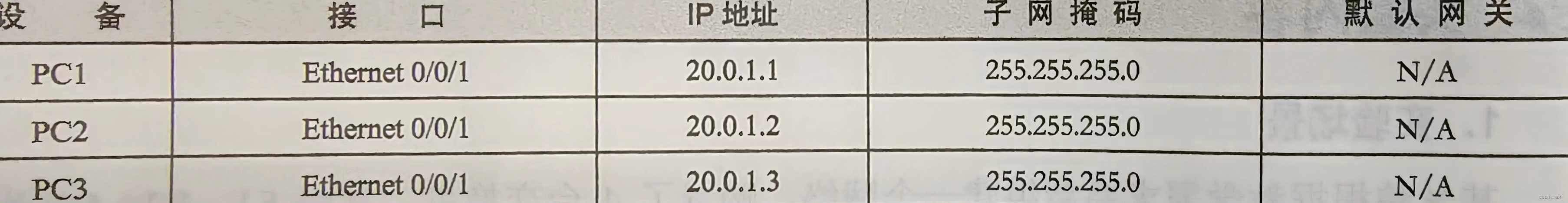

将3个车间设为A、B、C,2个发电机设为M、N。由题目可知车间开工数和启动电站的关系如下表所示:

| 车间开工数 | 启动电站 |

| 1 | M |

| 2 | N |

| 3 | M&N |

令1表示车间开工/发电机启动,0表示车间不开工/发电机不启动。通过分析,可得真值表如下表所示:

| A | B | C | M | N |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

(2)真值表写表达式

根据(1)的真值表可知M、N的表达式分别为:

M = A’B’C + A’BC’ + AB’C’ + ABC = A’B⊕![]() C + A(B⊕

C + A(B⊕![]() C)’ = A⊕

C)’ = A⊕![]() B⊕

B⊕![]() C

C

N = A’BC + AB’C + ABC’ + ABC = BC + AB + AC = (((A⊕![]() B)C)’ (AB)’ )’

B)C)’ (AB)’ )’

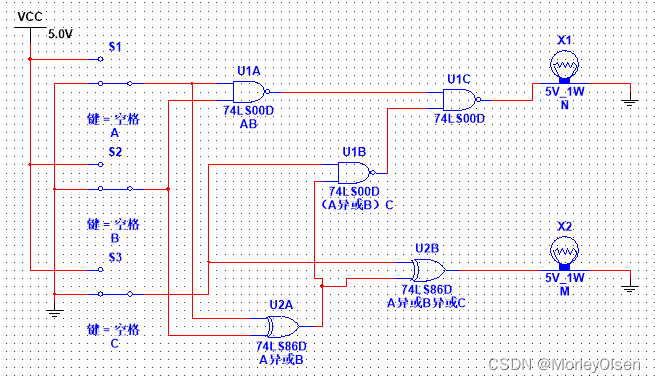

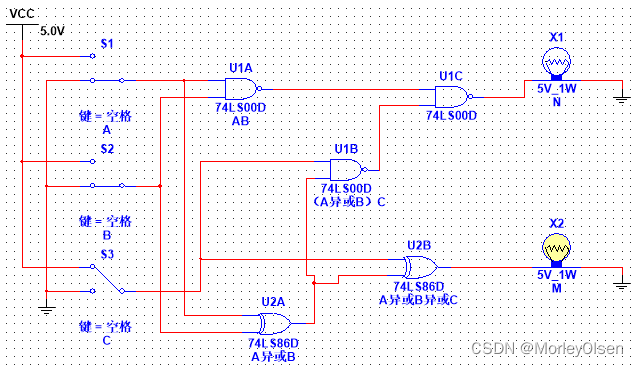

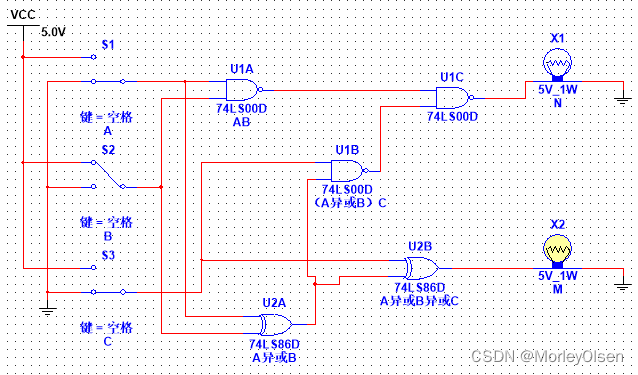

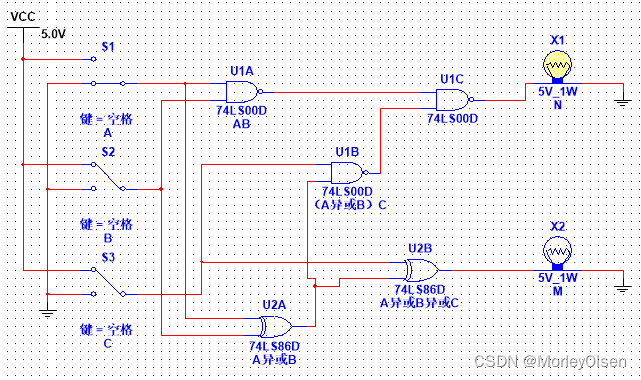

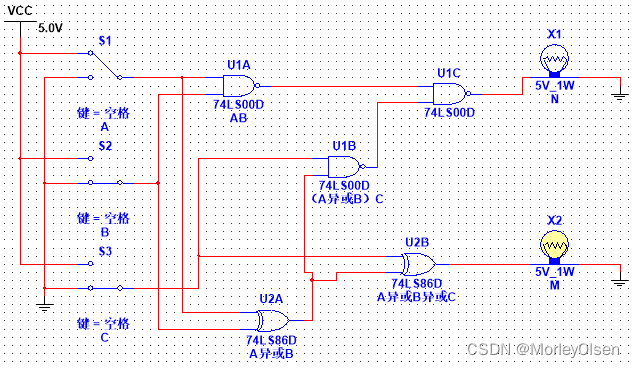

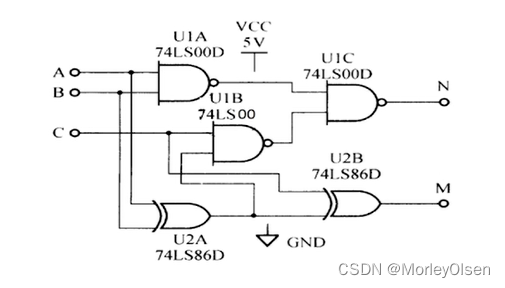

(3)表达式画电路图

理论电路图:

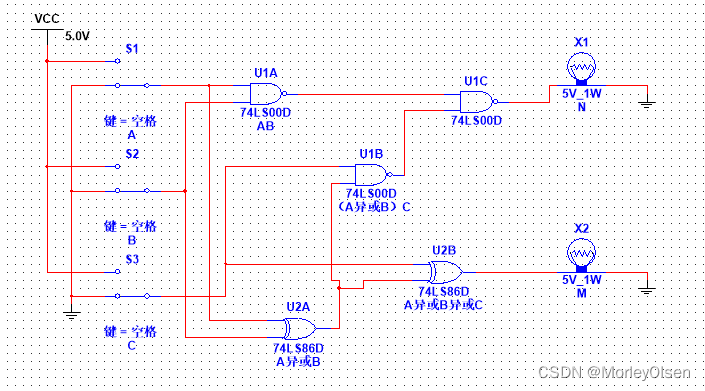

Multisim电路图:

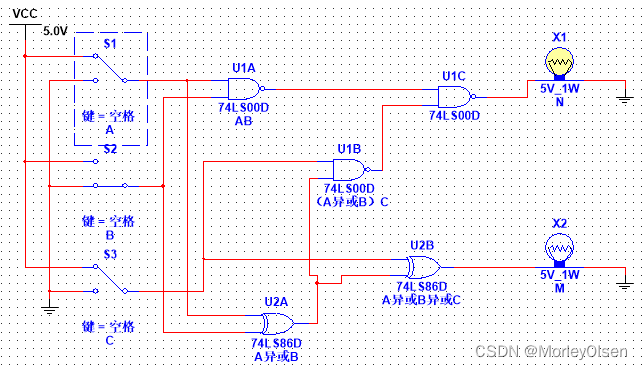

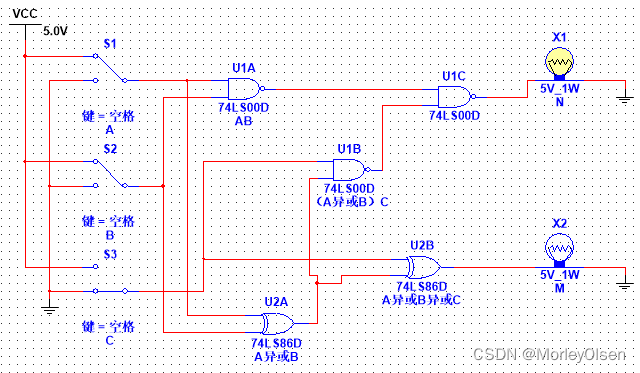

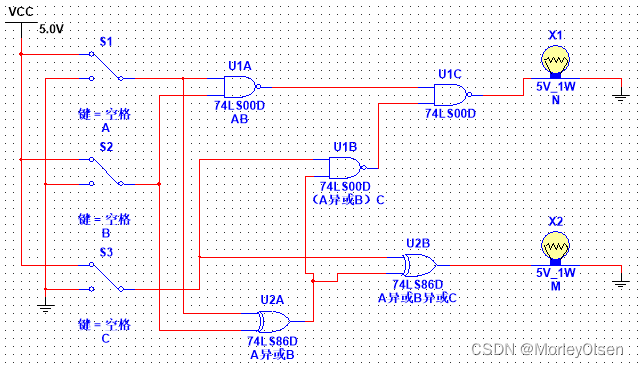

(4)实验验证真值表

通过上述电路图仿真,得到以下实验结果图片:

| 000 |

|

| 001 |

|

| 010 |

|

| 011 |

|

| 100 |

|

| 101 |

|

| 110 |

|

| 111 |

|

2 设计全减器

(1)逻辑抽象真值表

在输入方面,将上一位借位、被减数、减数分别设为Ci、A、B。在输出方面,将当前借位、差值分别设为Co、D。令1表示有相应位置的输入信号/输出信号,0表示没有相应位置的输入信号/输出信号。通过分析,可得真值表如下表所示:

| Ci | A | B | Co | D |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 0 | 0 |

| 1 | 0 | 0 | 1 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 |

(2)真值表写表达式

根据(1)的真值表可知Co、D的表达式分别为:

Co = m1 + m4 + m5 + m7 = (m1’ m4’ m5’ m7’)’

D = m1 + m2 + m4 + m7 = (m1’ m2’ m4’ m7’)’

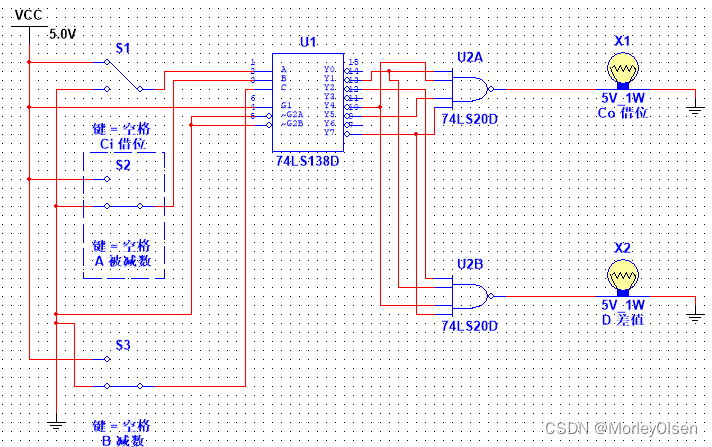

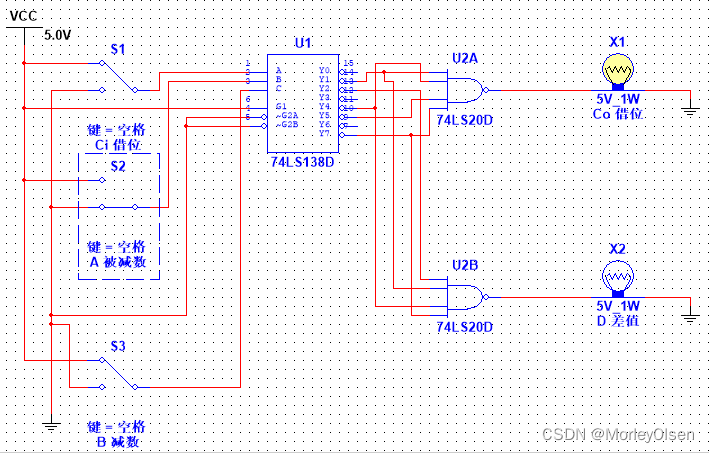

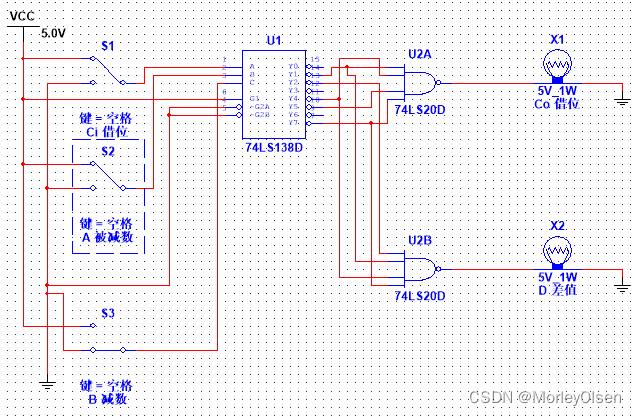

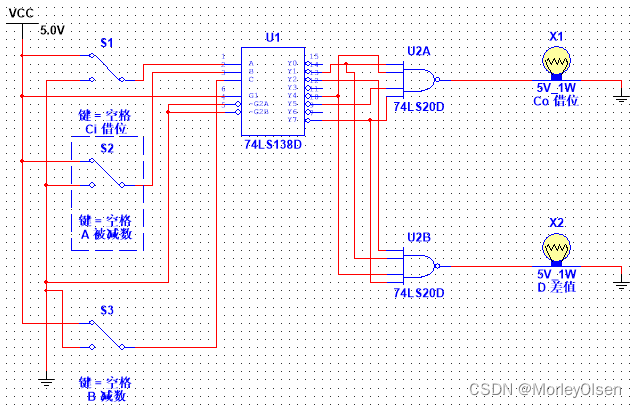

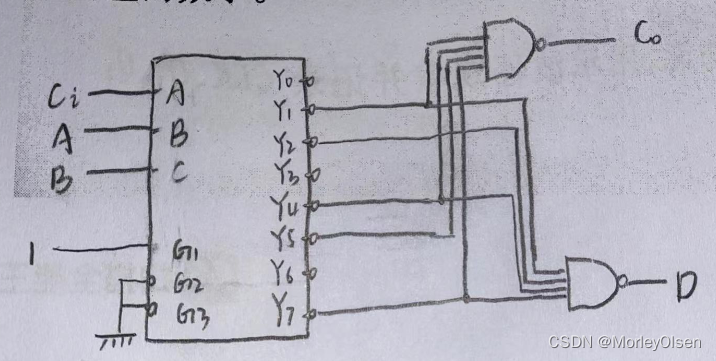

(3)表达式画电路图

理论电路图:

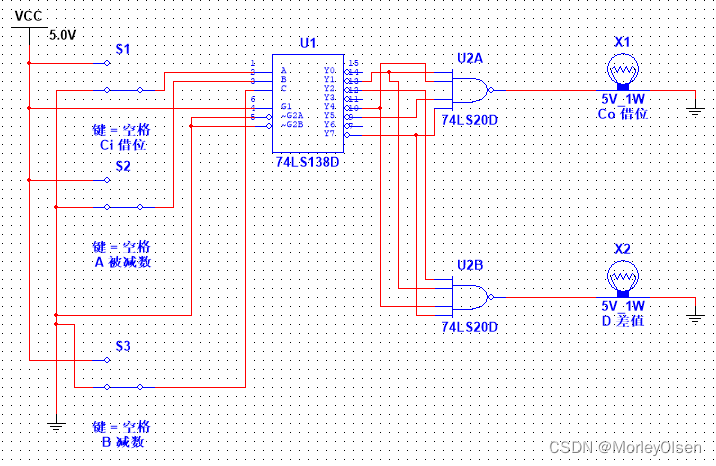

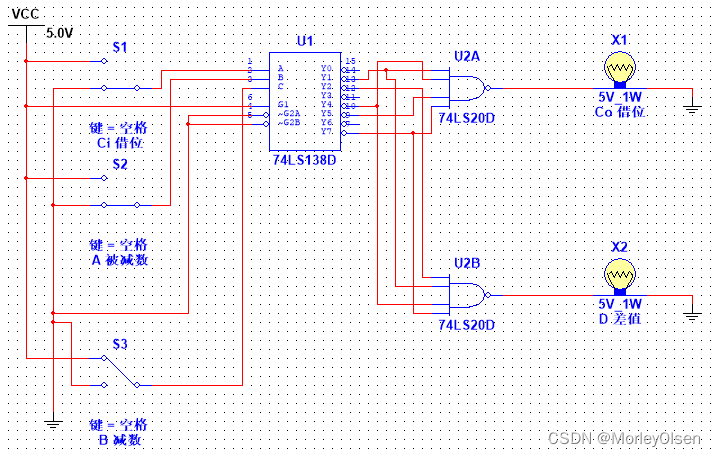

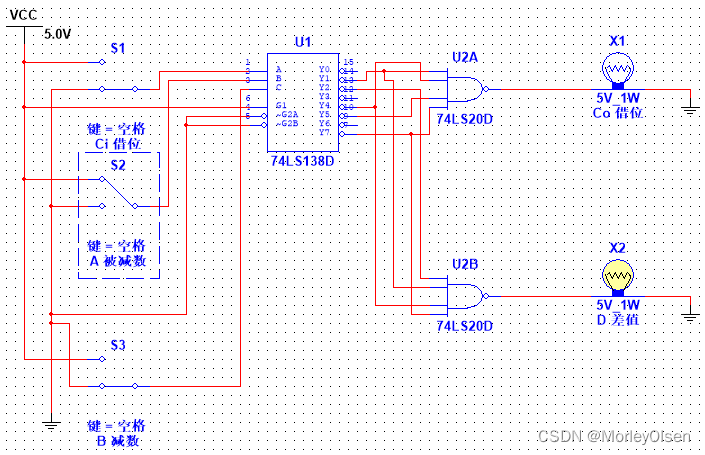

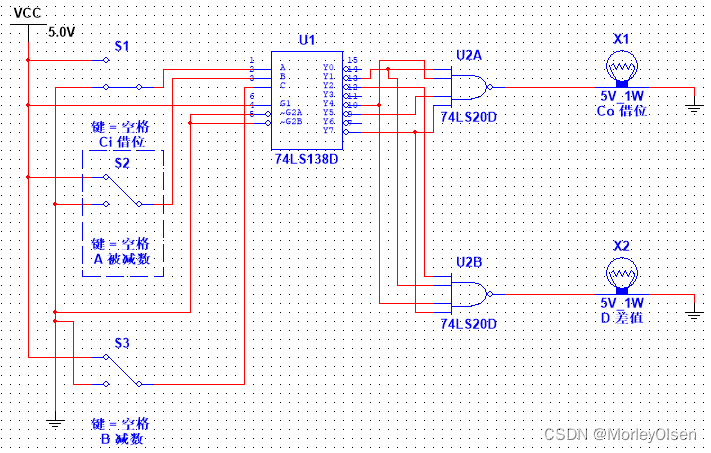

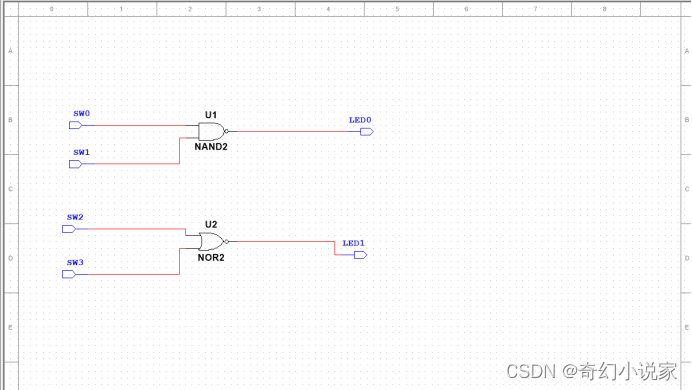

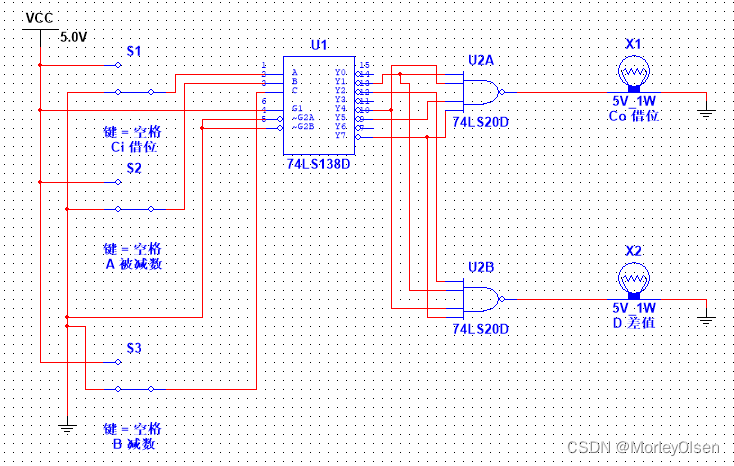

Multisim电路图:

(4)实验验证真值表

通过上述电路图仿真,得到以下实验结果图片:

| 000 |

|

| 001 |

|

| 010 |

|

| 011 |

|

| 100 |

|

| 101 |

|

| 110 |

|

| 111 |

|

3 设计译码显示电路

(1)逻辑抽象真值表

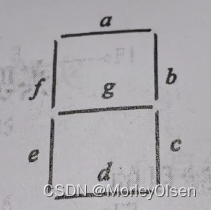

在输入方面,通过4位拨码开关进行数字的输入。相应的数字信号经过排阻后传到译码器,由译码器翻译出结果后单条输出。在输出方面,译码器的输出信号传输到共阳极数码显示管,并显示出图像。令1表示有相应位置的输入信号/输出信号,0表示没有相应位置的输入信号/输出信号。通过分析,可得真值表如下表所示:

| 4位拨码开关输入 (左边为低位) | 共阳极数码显示管显示位置 | 共阳极数码显示管理应显示数字 |

| 0000 | A B C D E F | 0 |

| 0001 | B C | 1 |

| 0010 | A B G E D | 2 |

| 0011 | A B G C D | 3 |

| 0100 | F G B C | 4 |

| 0101 | A F G C D | 5 |

| 0110 | F G E D C | 6 |

| 0111 | A B C | 7 |

| 1000 | A B C D E F G | 8 |

| 1001 | A B G F C | 9 |

| 1010 | G E D | 10 |

| 1011 | G C D | 11 |

| 1100 | F G B | 12 |

| 1101 | A F G D | 13 |

| 1110 | F G E D | 14 |

| 1111 | / | 15 |

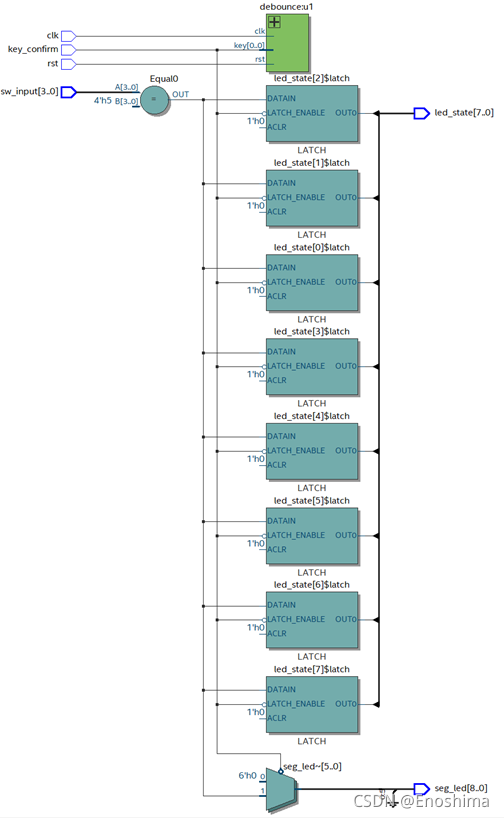

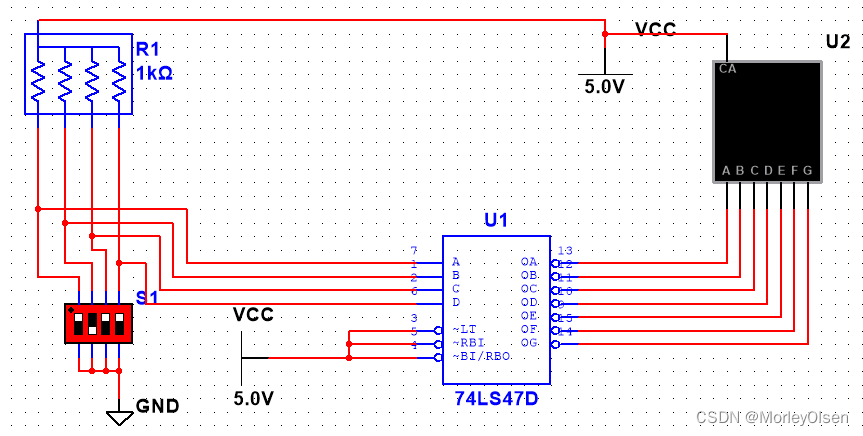

(2)根据译码器结构画电路图

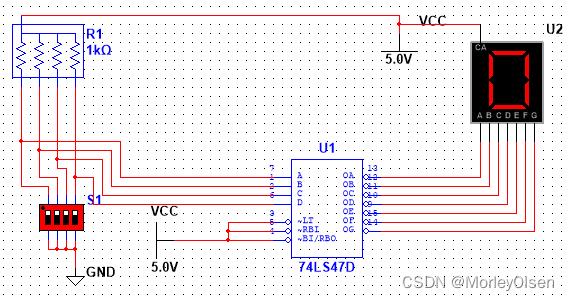

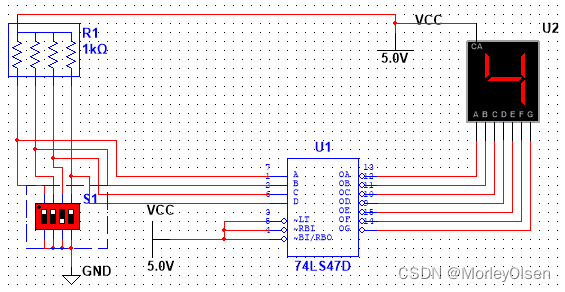

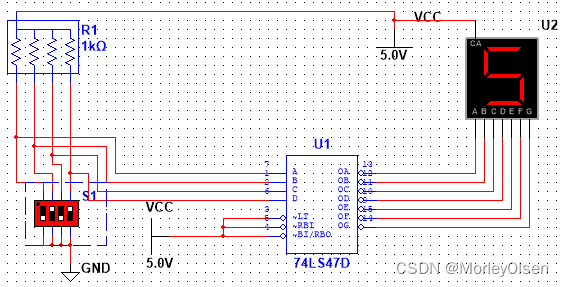

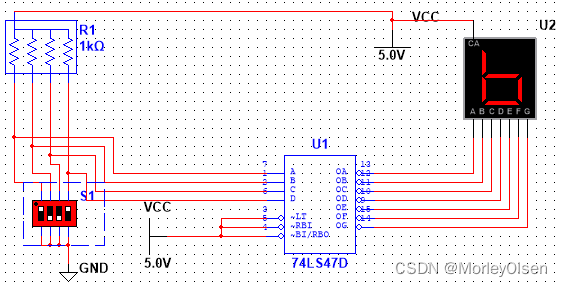

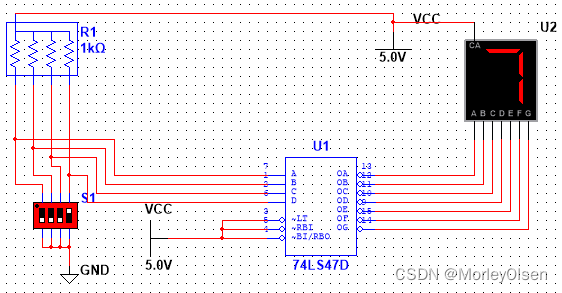

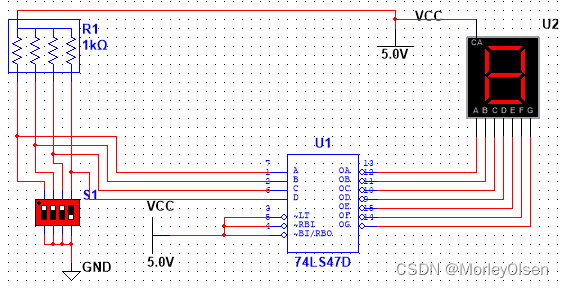

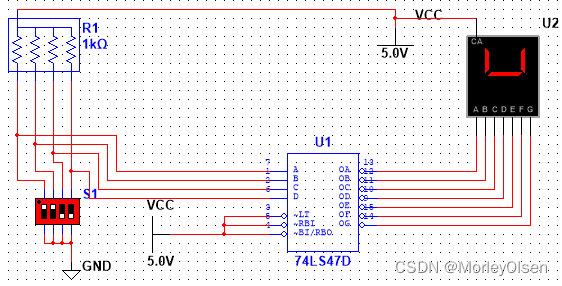

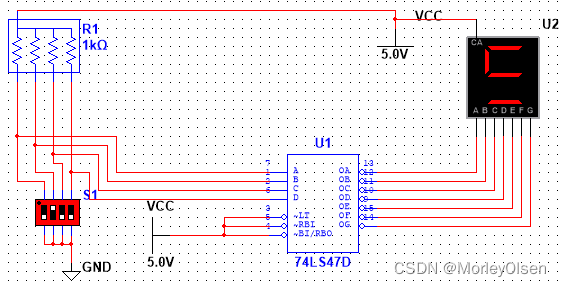

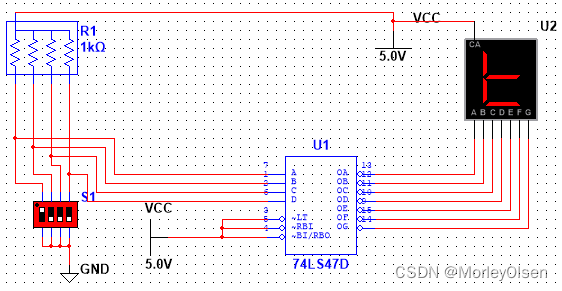

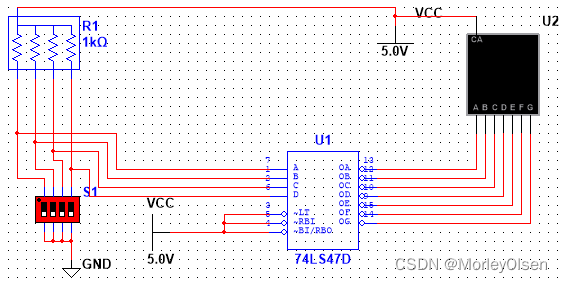

Multisim电路图:

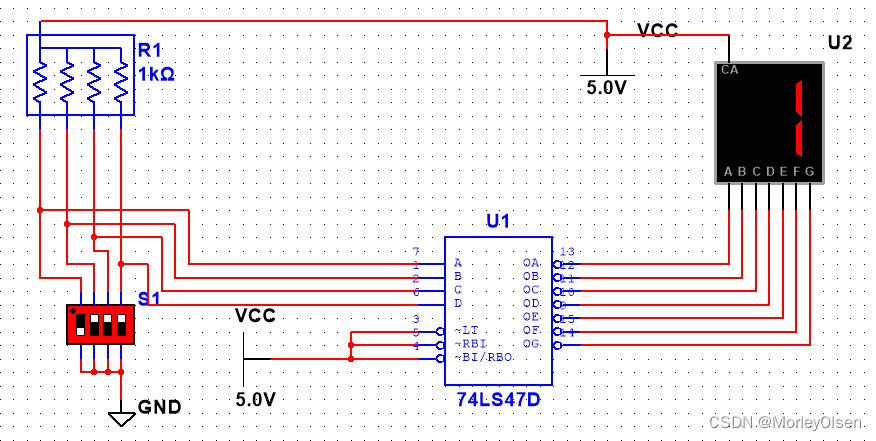

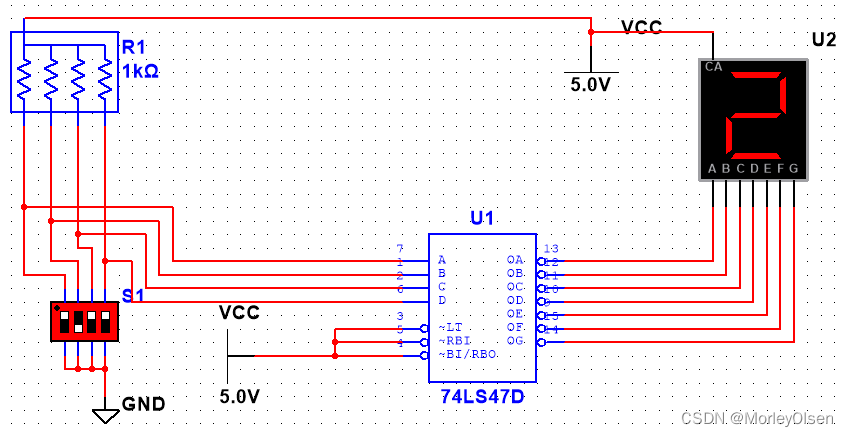

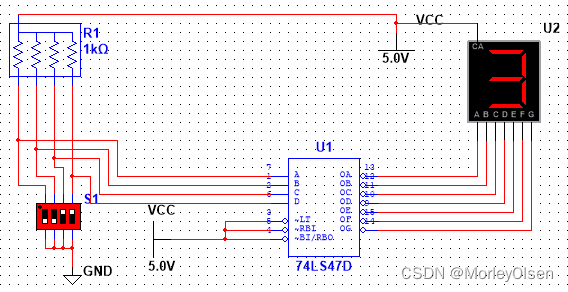

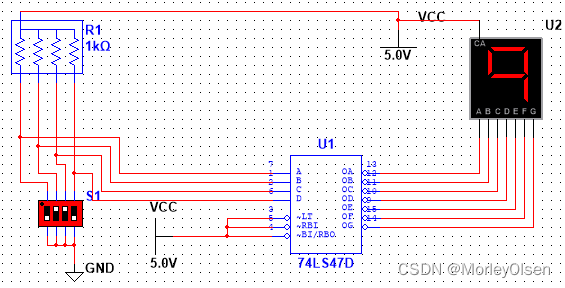

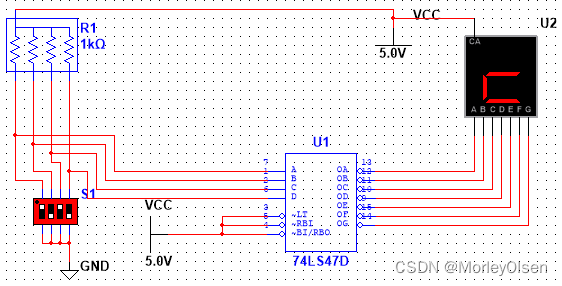

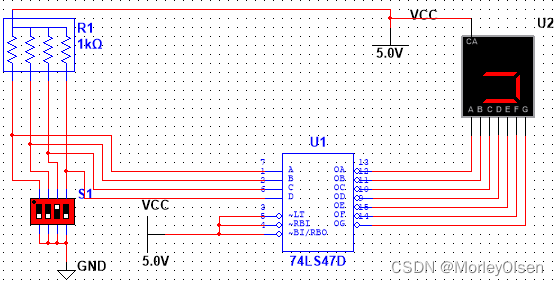

(3)实验验证真值表

| 4位拨码开关输入 (左边为低位) | 共阳极数码显示管显示位置 |

| 0000 |

|

| 0001 |

|

| 0010 |

|

| 0011 |

|

| 0100 |

|

| 0101 |

|

| 0110 |

|

| 0111 |

|

| 1000 |

|

| 1001 |

|

| 1010 |

|

| 1011 |

|

| 1100 |

|

| 1101 |

|

| 1110 |

|

| 1111 |

|

三 实验总结

由上述三个实验的仿真结果可知,自设连线的仿真电路与预期的真值表结果完全拟合。由此可知,本次仿真实验的结果良好。

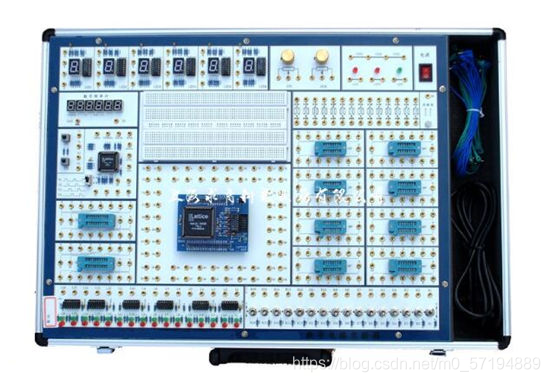

通过本次仿真实验,我学习到了组合逻辑电路的实验步骤主要是:逻辑抽象真值表-->真值表写表达式-->表达式画电路图-->实验验证真值表。我虽然没有能够在线下实操面包板、实验箱等实验装置,但是学习到了Multisim软件中的各种按钮功能,认识到Vcc和电路接地元件如何进行放置,并通过仿真实验进一步巩固了组合逻辑电路的相关知识。此外,因为不理解实验3的左侧电路结构,我通过查询相关资料,我学习了排阻、4位拨码开关、数字接地等元件的安置与连接,进行了简易版替换。虽然最终效果与课堂上的自动数字传输器不同,但基本实现了实验3所要求的功能。

另,实验的电路源文件在附属文档之中。