【本人只是想自己总结一下,大部分代码和原理图来源于教程https://www.stepfpga.com/doc】

1、点亮LED

目的:利用开发板上的四个拨码开关和四个按键分别控制8个LED灯的亮灭(按键按下时输出高电平,LED亮)。

module LED (key,sw,led);input [3:0] key; //按键输入信号input [3:0] sw; //开关输入信号output [7:0] led; //输出信号到LEDassign led = {key,sw}; //assign连续赋值。大括号是拼接符,表示把key和sw拼接组成一个新的8位数赋值给ledendmodule

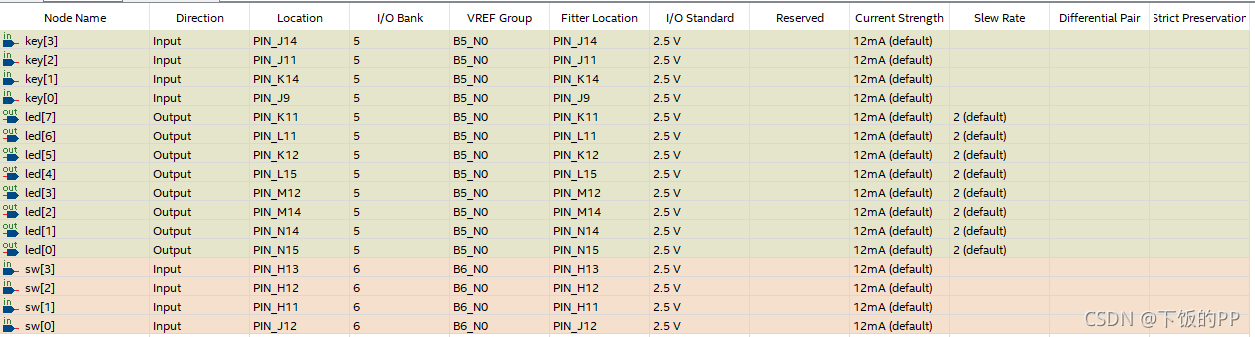

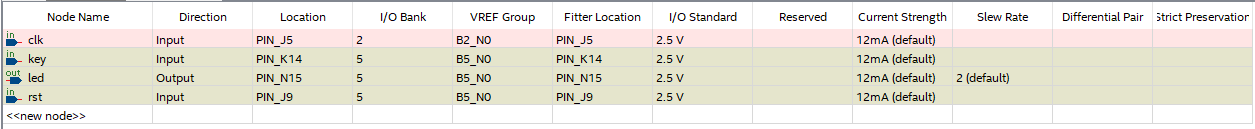

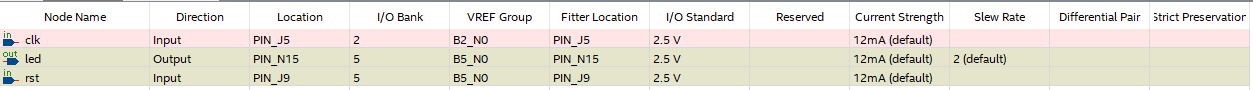

引脚分配:

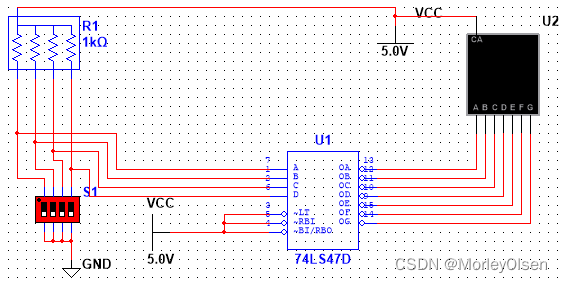

2、点亮七段数码管

0 - F 对应的输入码和输出码

seg_data_1 和 seg_data_2,分别输入控制两个数码管的显示。seg提前存储16个输出字符所对应的十六进制数字。【稍加补充可以显示A-F】

module segment (seg_data_1,seg_data_2,seg_led_1,seg_led_2);input [3:0] seg_data_1; //数码管需要显示0~9十个数字,所以最少需要4位输入做译码input [3:0] seg_data_2; //小脚丫上第二个数码管output [8:0] seg_led_1; //在小脚丫上控制一个数码管需要9个信号 MSB~LSB=DIG、DP、G、F、E、D、C、B、Aoutput [8:0] seg_led_2; //在小脚丫上第二个数码管的控制信号 MSB~LSB=DIG、DP、G、F、E、D、C、B、Areg [8:0] seg [15:0]; //定义了一个reg型的数组变量,相当于一个10*9的存储器,存储器一共有10个数,每个数有9位宽initial //在过程块中只能给reg型变量赋值,Verilog中有两种过程块always和initial//initial和always不同,其中语句只执行一次beginseg[0] = 9'h3f; //对存储器中第一个数赋值9'b00_0011_1111,相当于共阴极接地,DP点变低不亮,7段显示数字 0seg[1] = 9'h06; //7段显示数字 1seg[2] = 9'h5b; //7段显示数字 2seg[3] = 9'h4f; //7段显示数字 3seg[4] = 9'h66; //7段显示数字 4seg[5] = 9'h6d; //7段显示数字 5seg[6] = 9'h7d; //7段显示数字 6seg[7] = 9'h07; //7段显示数字 7seg[8] = 9'h7f; //7段显示数字 8seg[9] = 9'h6f; //7段显示数字 9seg[10] = 9'h77; //7段显示字母 Aseg[11] = 9'h7C; //7段显示字母 Bseg[12] = 9'h39; //7段显示字母 Cseg[13] = 9'h5e; //7段显示字母 Dseg[14] = 9'h79; //7段显示字母 Eseg[15] = 9'h71; //7段显示字母 Fendassign seg_led_1 = seg[seg_data_1]; //连续赋值,这样输入不同四位数,就能输出对于译码的9位输出assign seg_led_2 = seg[seg_data_2];endmodule

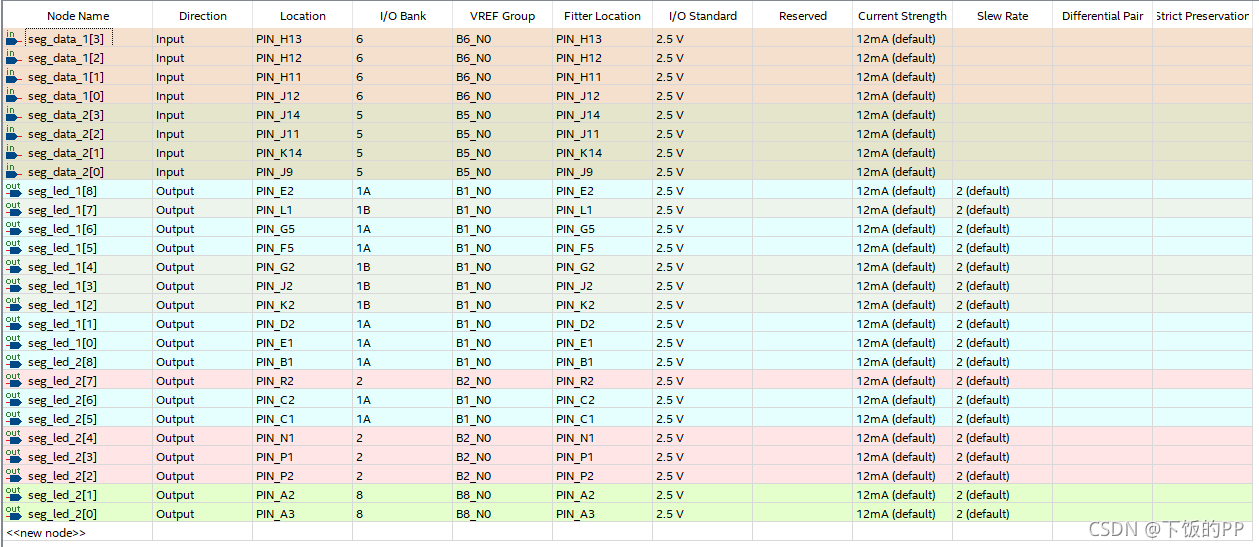

引脚分配:

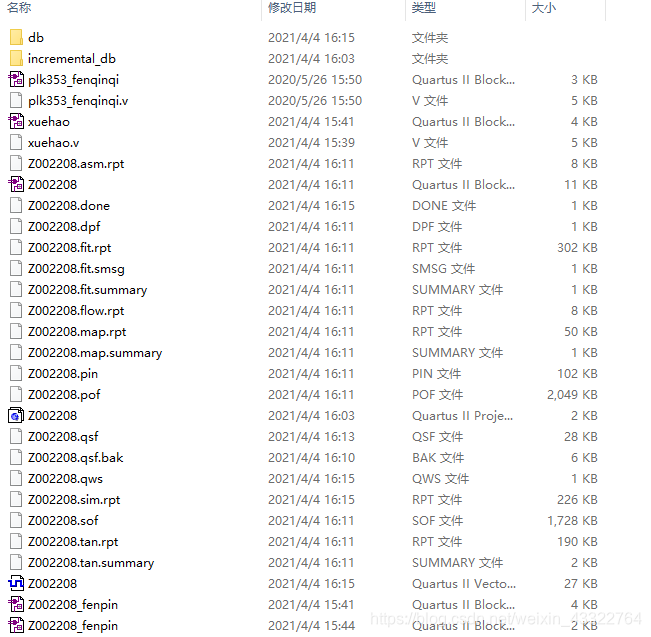

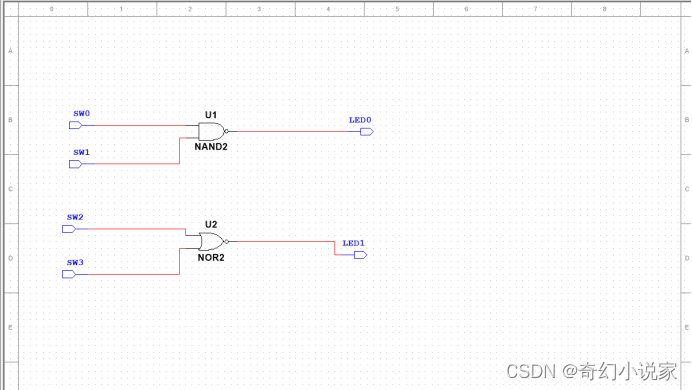

3、FPGA开发流程

实现功能:设置a,b两个输入引脚,分别接高低电平。按钮的状态控制LED灯的输出。这里我接B4为高电平,A5为低电平。不按下按钮LED亮,反之则灭。代码如下:

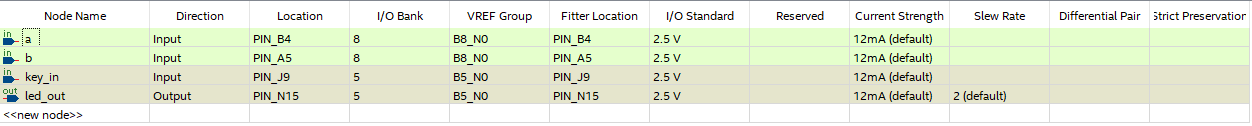

module led_test(a,b,key_in,led_out);input a;//输入端口ainput b;//输入端口binput key_in;//按键输入,实现输入输入通道的选择output led_out;//led 控制端口//当key_in == 0; led_oud = 1assign led_out = {key_in == 0}? a : b;endmodule引脚分配:

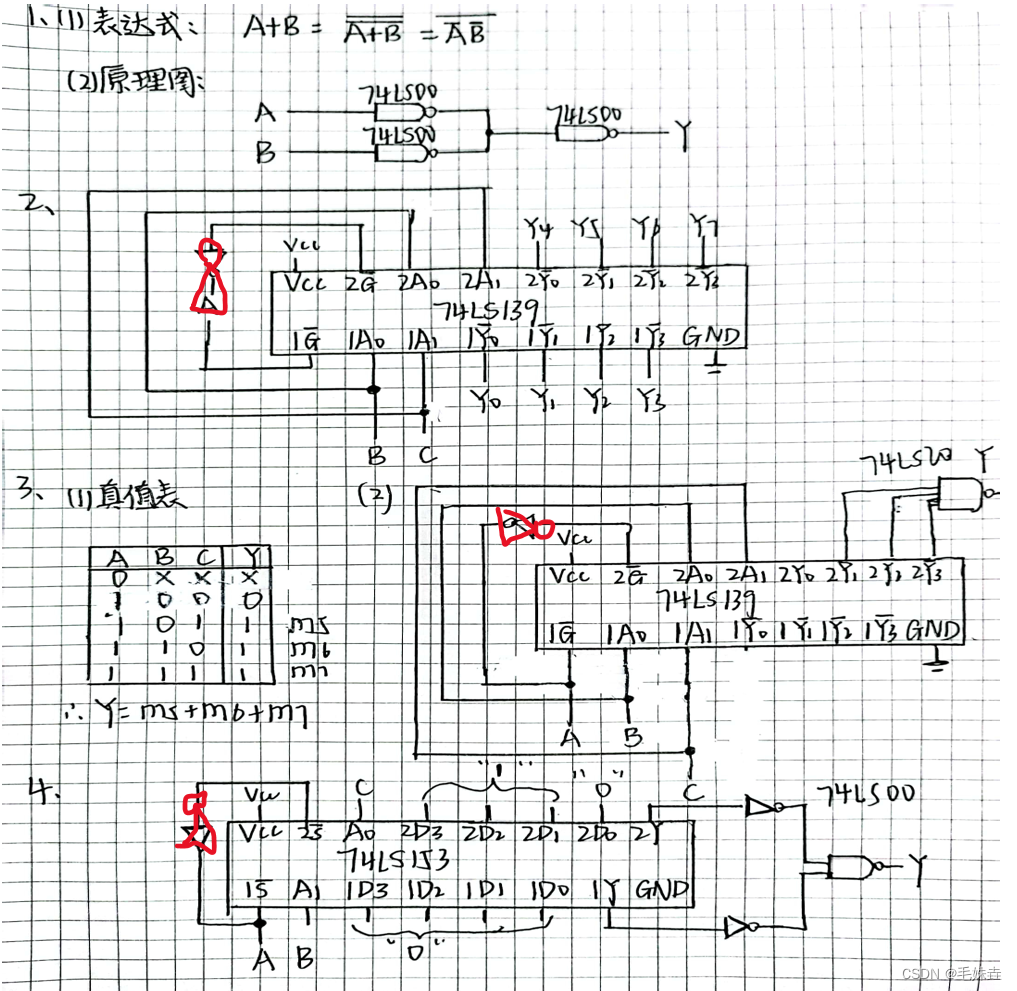

4、3-8译码器

本实验内容为通过控制三个拨码开关来控制8个LED灯的亮灭状态。【注意,实验中输出为1的时候LED是灭的状态】

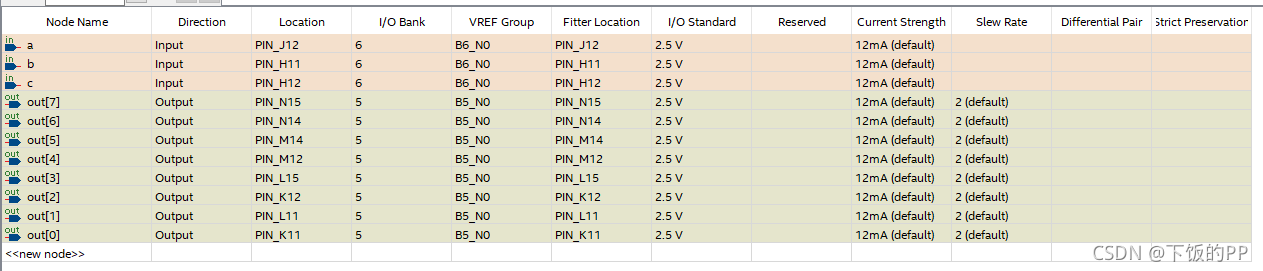

module my3_8(a,b,c,out);input a;//输入端口Ainput b;//输入端口Binput c;//输入端口Coutput reg [7:0]out;//输出端口always@(a,b,c)begincase({a,b,c})3'b000:out = 8'b1111_1110;3'b001:out = 8'b1111_1101;3'b010:out = 8'b1111_1011;3'b011:out = 8'b1111_0111;3'b100:out = 8'b1110_1111;3'b101:out = 8'b1101_1111;3'b110:out = 8'b1011_1111;3'b111:out = 8'b0111_1111;endcaseendendmodule引脚分配:

5、按键消抖

本人通俗的理解就是在按下按键的时候按键会产生抖动,按下的前期按键的电平不会保持稳定,而是处于高低转换的一个状态。这里需要等待20ms左右等待按键稳定了再去检测。

消抖程序设置了两个寄存器用来存储上一个和当前触发的按键值并进行边缘检测【key_edge】,如果还在抖动状态则key_edge在此过程中会变为1,时钟复位,重新计时。只有当时钟计时满20ms之后才能进行下一步骤【检测状态变化】

如果按键从1变为0,那么在这过程中key_pause会产生一个时钟的高脉冲,反之则不会。因为我们只是按下按键的时候才是有效状态,因此这样的设计是十分合理的。

下面是代码,首先是没有进行按键消抖的代码:

module top(key, //按键输入rst, //复位输入led //led输出);input key,rst;output reg led;always @(key or rst)if (!rst) //复位时led熄灭led = 1;else if(key == 0) led = ~led; //按键按下时led翻转elseled = led;

endmodule下面是按键消抖代码:

module debounce (clk,rst,key,key_pulse);parameter N = 1; //要消除的按键的数量input clk;input rst;input [N-1:0] key; //输入的按键 output [N-1:0] key_pulse; //按键动作产生的脉冲 reg [N-1:0] key_rst_pre; //定义一个寄存器型变量存储上一个触发时的按键值reg [N-1:0] key_rst; //定义一个寄存器变量储存储当前时刻触发的按键值wire [N-1:0] key_edge; //检测到按键由高到低变化是产生一个高脉冲//利用非阻塞赋值特点,将两个时钟触发时按键状态存储在两个寄存器变量中always @(posedge clk or negedge rst)beginif (!rst) beginkey_rst <= {N{1'b1}}; //初始化时给key_rst赋值全为1,{}中表示N个1key_rst_pre <= {N{1'b1}};endelse beginkey_rst <= key; //第一个时钟上升沿触发之后key的值赋给key_rst,同时key_rst的值赋给key_rst_prekey_rst_pre <= key_rst; //非阻塞赋值。相当于经过两个时钟触发,key_rst存储的是当前时刻key的值,key_rst_pre存储的是前一个时钟的key的值end endassign key_edge = key_rst_pre & (~key_rst);//脉冲边沿检测。当key检测到下降沿时,key_edge产生一个时钟周期的高电平reg [17:0] cnt; //产生延时所用的计数器,系统时钟12MHz,要延时20ms左右时间,至少需要18位计数器 //产生20ms延时,当检测到key_edge有效是计数器清零开始计数always @(posedge clk or negedge rst)beginif(!rst)cnt <= 18'h0;else if(key_edge)cnt <= 18'h0;elsecnt <= cnt + 1'h1;end reg [N-1:0] key_sec_pre; //延时后检测电平寄存器变量reg [N-1:0] key_sec; //延时后检测key,如果按键状态变低产生一个时钟的高脉冲。如果按键状态是高的话说明按键无效always @(posedge clk or negedge rst)beginif (!rst) key_sec <= {N{1'b1}}; else if (cnt==18'h3ffff)key_sec <= key; endalways @(posedge clk or negedge rst)beginif (!rst)key_sec_pre <= {N{1'b1}};else key_sec_pre <= key_sec; end assign key_pulse = key_sec_pre & (~key_sec); endmodule

调整后的代码:

module top (clk,rst,key,led);input clk;input rst;input key; output reg led; wire key_pulse;//当按键按下时产生一个高脉冲,翻转一次ledalways @(posedge clk or negedge rst)beginif (!rst) led <= 1'b1;else if (key_pulse)led <= ~led;elseled <= led;end //例化消抖module,这里没有传递参数N,采用了默认的N=1 debounce u1 ( .clk (clk),.rst (rst),.key (key),.key_pulse (key_pulse));endmodule

引脚分配:

6、时钟分频【自己写写理解,可能不对】

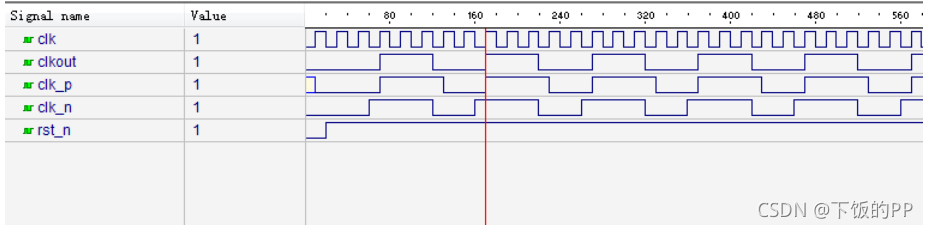

在本实验中我们将实现任意整数的分频器,分频的时钟保持50%占空比。

本实验利用系统时钟计时,当每一次触发系统时钟上升沿的时候上升沿和下降沿计数器进行自增或者清零。cnt为偶数的时候clk输出高低电平时间相等,占空比为50%,因此可以直接输出ckl的结果;如果cnt为奇数,由于在代码中我们要进行右移一位(也就是整数除以2去掉余数)的操作,于是高电平周期相比于低电平周期要多一个,因此最终要通过两个clk错开半个周期触发(也就是上升沿和下降沿)然后进行相与的操作得到我们想得到的结果。

代码分为两大部分:上升沿和下降沿

分别在系统时钟上升和下降的时候触发。计数器与N-1比较控制周期。计数器通过与(N>>1)控制分频时钟。

代码:

module divide ( clk,rst_n,clkout);input clk,rst_n; //输入信号,其中clk连接到FPGA的C1脚,频率为12MHzoutput clkout; //输出信号,可以连接到LED观察分频的时钟//parameter是verilog里常数语句parameter WIDTH = 3; //计数器的位数,计数的最大值为 2**WIDTH-1parameter N = 5; //分频系数,请确保 N < 2**WIDTH-1,否则计数会溢出reg [WIDTH-1:0] cnt_p,cnt_n; //cnt_p为上升沿触发时的计数器,cnt_n为下降沿触发时的计数器reg clk_p,clk_n; //clk_p为上升沿触发时分频时钟,clk_n为下降沿触发时分频时钟//上升沿触发时计数器的控制always @ (posedge clk or negedge rst_n ) //posedge和negedge是verilog表示信号上升沿和下降沿//当clk上升沿来临或者rst_n变低的时候执行一次always里的语句beginif(!rst_n)cnt_p<=0;else if (cnt_p==(N-1))cnt_p<=0;else cnt_p<=cnt_p+1; //计数器一直计数,当计数到N-1的时候清零,这是一个模N的计数器end//上升沿触发的分频时钟输出,如果N为奇数得到的时钟占空比不是50%;如果N为偶数得到的时钟占空比为50%always @ (posedge clk or negedge rst_n)beginif(!rst_n)clk_p<=0;else if (cnt_p<(N>>1)) //N>>1表示右移一位,相当于除以2去掉余数clk_p<=0;else clk_p<=1; //得到的分频时钟正周期比负周期多一个clk时钟end//下降沿触发时计数器的控制 always @ (negedge clk or negedge rst_n)beginif(!rst_n)cnt_n<=0;else if (cnt_n==(N-1))cnt_n<=0;else cnt_n<=cnt_n+1;end//下降沿触发的分频时钟输出,和clk_p相差半个时钟always @ (negedge clk)beginif(!rst_n)clk_n<=0;else if (cnt_n<(N>>1)) clk_n<=0;else clk_n<=1; //得到的分频时钟正周期比负周期多一个clk时钟endassign clkout = (N==1)?clk:(N[0])?(clk_p&clk_n):clk_p; //条件判断表达式//当N=1时,直接输出clk//当N为偶数也就是N的最低位为0,N(0)=0,输出clk_p//当N为奇数也就是N最低位为1,N(0)=1,输出clk_p&clk_n。正周期多所以是相与

endmodule

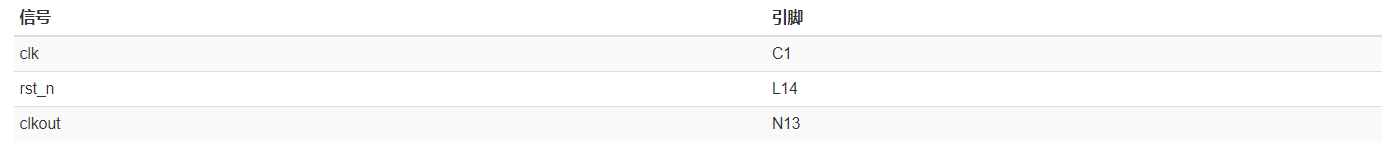

引脚分配:

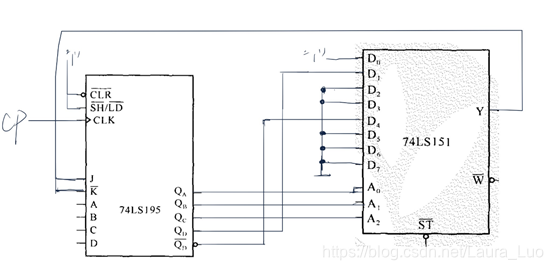

7、LED流水灯

流水灯的实现是通过分频器进行计时,设置好我们想要的周期,然后调用divide进行时钟分配反馈一个clk1h信号,当clk1h触发上升沿的时候也就是每隔一秒钟我们会调用一次3-8译码器,分配给八个LED等高低电平,控制他们的两与灭。同时也可以通过每一次将最后一位LED灯的电平前移到第一个然后循环实现流水灯的操作,代码分别如下。

第一种方法:

module flashled (clk,rst,led);input clk,rst; output [7:0] led; reg [2:0] cnt ; //定义了一个3位的计数器,输出可以作为3-8译码器的输入wire clk1h; //定义一个中间变量,表示分频得到的时钟,用作计数器的触发 //例化module decode38,相当于调用decode38 u1 ( .sw(cnt), //例化的输入端口连接到cnt,输出端口连接到led .led(led));//例化分频器模块,产生一个1Hz时钟信号 divide #(.WIDTH(32),.N(12000000)) u2 ( //传递参数.clk(clk),.rst_n(rst), //例化的端口信号都连接到定义好的信号.clkout(clk1h)); //1Hz时钟上升沿触发计数器,循环计数 always @(posedge clk1h or negedge rst)if (!rst)cnt <= 0;elsecnt <= cnt +1;endmodule

第二种方法:

module flashled (clk,rst,led);input clk,rst; output [7:0] led; wire clk1h; //定义一个中间变量,表示分频得到的时钟,用作计数器的触发 //例化分频器模块,产生一个1Hz时钟信号 divide #(.WIDTH(32),.N(12000000)) u2 ( //传递参数.clk(clk),.rst_n(rst), //例化的端口信号都连接到定义好的信号.clkout(clk1h)); //1Hz时钟上升沿触发循环赋值 reg [7:0] led;always@(posedge clk1h or negedge rst)beginif(!rst)led <= 8'b11111110; // <=为非阻塞赋值else led <= {led[0],led[7:1]}; //当时钟上升沿来一次,执行一次赋值,赋值内容是led[0]与led[7:1]重新拼接成8位赋给led,相当于循环右移end

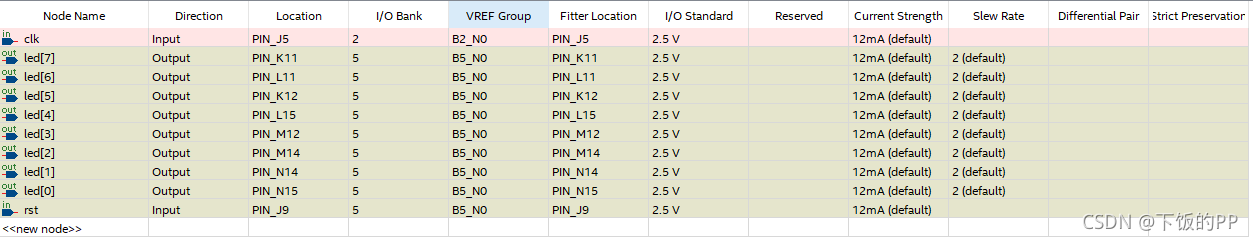

引脚分配:

8、呼吸灯

呼吸灯的实现方案很简单,具体的思想就是设置两个计数器cnt1和cnt2。cnt1关联系统时钟,系统时钟每触发一次cnt1自增1。当系统时钟触发N次(N与我们所想得到的呼吸灯的呼吸时间周期有关)的时候cnt2自增1(上限也为T)。这样cnt2实现了从0到T变化的过程。

对于每一个cnt2,他与当前cnt1的值进行比较,从而输出高电平与低电平,进而控制了呼吸灯的亮度程度,也就是实现了呼吸灯的功能。

从图中我们可以看出,这里的周期设定为2,也就是从灭到亮与从亮到灭分别需要1s的时间。因为系统时钟频率为12M,所以我认为这里应当将T设置为3464。【实际测定当T为3464 的时候的确是2s的周期】,但是教程中使用的是2400,因此闪烁频率更大一些。

下面是代码:

module breath_led(clk,rst,led);input clk; //系统时钟输入input rst; //复位输出output led; //led输出reg [24:0] cnt1; //计数器1reg [24:0] cnt2; //计数器2reg flag; //呼吸灯变亮和变暗的标志位parameter CNT_NUM = 2400; //计数器的最大值 period = (2400^2)*2 = 24000000 = 2s//产生计数器cnt1always@(posedge clk or negedge rst) begin if(!rst) begincnt1<=13'd0;end else beginif(cnt1>=CNT_NUM-1) cnt1<=1'b0;else cnt1<=cnt1+1'b1; endend//产生计数器cnt2always@(posedge clk or negedge rst) begin if(!rst) begincnt2<=13'd0;flag<=1'b0;end else beginif(cnt1==CNT_NUM-1) begin //当计数器1计满时计数器2开始计数加一或减一if(!flag) begin //当标志位为0时计数器2递增计数,表示呼吸灯效果由暗变亮if(cnt2>=CNT_NUM-1) //计数器2计满时,表示亮度已最大,标志位变高,之后计数器2开始递减flag<=1'b1;elsecnt2<=cnt2+1'b1;end else begin //当标志位为高时计数器2递减计数if(cnt2<=0) //计数器2级到0,表示亮度已最小,标志位变低,之后计数器2开始递增flag<=1'b0;else cnt2<=cnt2-1'b1;endendelse cnt2<=cnt2; //计数器1在计数过程中计数器2保持不变endend//比较计数器1和计数器2的值产生自动调整占空比输出的信号,输出到led产生呼吸灯效果assign led = (cnt1<cnt2)?1'b0:1'b1;endmodule

代码的结构很清晰,分为cnt1和cnt2两个模块。

cnt1在未达到上限的时候一直自增,达到上限后还原为0

cnt2在cnt1达到上限时触发,上下限分别是设定值和0。通过判断flag的值来决定是自增还是自减。

最后通过判断cnt1和cnt2的大小输出高低电平。从图中我们也可以看出,当cnt1大的时候输出高电平,也就是说LED是亮 - 灭 - 亮 的状态。

引脚分配:

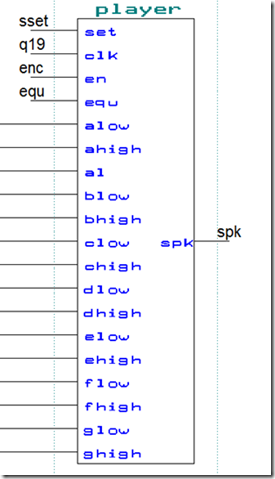

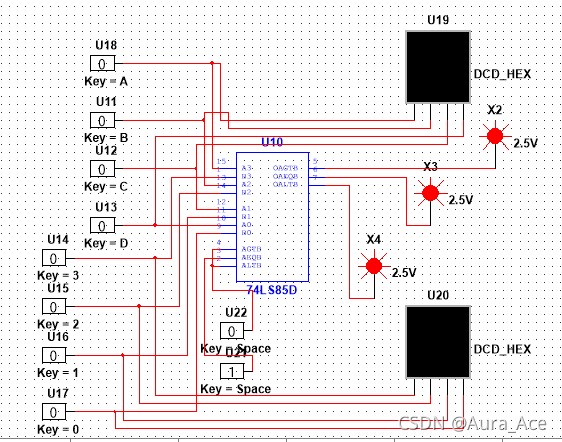

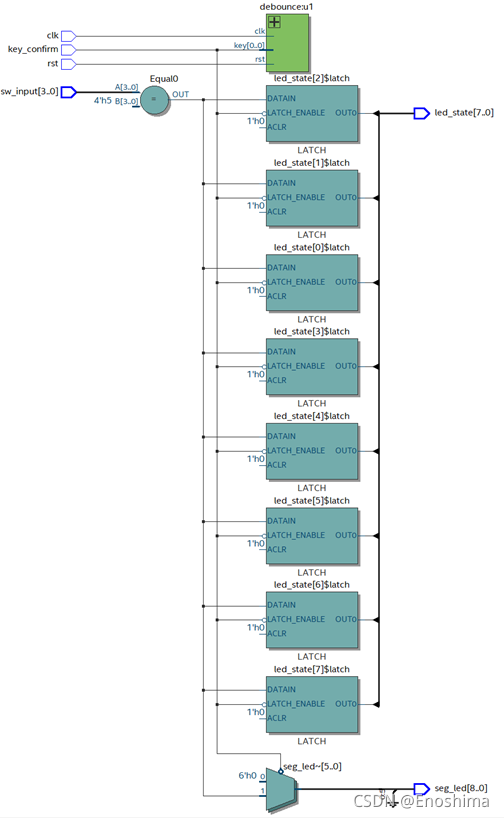

9、密码箱【本人改编】

各个输入输出按键的功能:

- key1:确认输入【不论是输入密码还是修改密码时候的确认都是使用这个共同的按键】

- key2:复位按键。将左侧数码管显示还原为3【一共有3次修改机会】;右侧数码管显示为“-”【无输入状态】

- key3:重置密码按键,只有当解锁成功的时候按下此按键才能成功触发修改密码程序。当触发程序后会亮起蓝灯。

- key4:删除按键,当输入的数字想要修改时按下此案件可以清除上一个输入的数字,并且数码管显示为“-”。

SW1,2,3,4相当于四位二进制数字,在此程序中可以将其转换为十进制数字并显示到数码管上。

本实验使用了红绿蓝三个指示灯和两个数码管。

本程序的基本步骤:

- 1、初始密码为0000,初始拨码为0000,按下四次key1可以实现四次输入,当按下第五次key1时相当于确认。如果输入密码正确则绿灯亮起。两个数码管均显示为“-”,解锁成功;如果输入密码失败则会亮起红灯,左侧数码管的示数会减小1,如果三次密码均输入错误,下侧的LED灯会同时亮起红色和绿色的灯,这样代表解锁失败。

- 2、如果解锁成功,这时候可以按下key2,可以发现左侧的数码管显示为3,右侧的数码管显示为“-”,此时处于锁住状态,打乱密码后可以当做密码锁使用

- 3、如果解锁成功,这时候按下key3,可以发现下侧蓝色的led等亮起,这时候可以通过拨动拨码开关修改当前数字,按下四次确认件后再按下第五次确认件代表设置密码成功,这时候再输入初始的0000将不可以进行解锁。

- 4、当输入过程中按下key4可以发现右侧的数码管显示为“-”,这样代表清除了上一次输入的数字。

- 5、细节处理:如果输入的数字大于9,将始终显示“-”,因为这样会导致屏幕显示出现异常。

代码分为两部分,一部分是按键消抖,另一部分是主程序。按键消抖上面已经总结过了,因此这里只发表一下主程序代码。

module pwd(clk,rst,key_cfm,key1_cfm,key_del,sw_pwd,led,sega,segb,blue);input clk;//时钟.input rst;//复位.input key_cfm;//确认键.input key1_cfm;//修改密码确认键input key_del;//管理员重置程序按键input [3:0] sw_pwd;//四路拨动开关对应四位二进制密码.output [1:0] led;//解锁指示灯.output [8:0] sega;//第一根数码管(右).output [8:0] segb;//第二根数码管(左).output [0:0] blue;//蓝色指示灯//parameter password = 4'b1001;//设置密码.reg [3:0] password [3:0];//固定密码reg [3:0] input_pwd [3:0];//输入密码reg [1:0] sgn;//两位指示灯信号,对应两路6指示灯(一红一绿).reg [8:0] seg [9:0];//9位宽信号,用来储存数码管数字显示数据.reg [8:0] seg_data [1:0];//数码管显示信号寄存器.reg [0:0] led_blue;reg [1:0] cnt;//计数器,用以统计错误次数.reg [2:0] cnt_pwd;//输入密码次数计数器,一共四位密码,用来计数一共输入了几密码。reg [0:0] confirm;//用来确认是否开始设置新密码reg lock;//程序锁,以避免次数用完后或者密码正确之后的误操作.wire cfm_dbs;//消抖后的确认脉冲.wire cfm_dbs1;//消抖后的确认脉冲.wire cfm_del;//消抖后的确认脉冲.initial begin//初始化.//密码初始化为0000password[0] <= 4'b0000;password[1] <= 4'b0000;password[2] <= 4'b0000;password[3] <= 4'b0000;seg[0] <= 9'h3f;//数码管显示数字0信号.seg[1] <= 9'h06;//数字1信号.seg[2] <= 9'h5b;//数字2信号.seg[3] <= 9'h4f;//数字3信号.seg[4] <= 9'h66;//数字4信号.seg[5] <= 9'h6d;//数字5信号.seg[6] <= 9'h7d;//数字6信号seg[7] <= 9'h07;//数字7信号seg[8] <= 9'h7f;//数字8信号seg[9] <= 9'h6f;//数字9信号seg_data[0] <= 9'h3f;//数码管初始显示数字0.seg_data[1] <= 9'h40;//数码管初始显示一条横线.cnt <= 2'b11;//计数器初始值为3.cnt_pwd <= 3'b100;//密码次数计数器初始值为4.confirm <= 1'b0;//初始时设置新密码判断值为为0,相当于bool类型的falseendalways @ (posedge clk or negedge rst)//时钟边沿触发或复位按键触发.beginif(!rst)begin//复位操作.sgn <= 2'b11;//两灯均灭.led_blue <=1'b1;//蓝灯灭seg_data[0] <= seg[3];//第一根显示数字3.seg_data[1] <= 9'h40;//第二根显示一根横线.cnt <= 2'b11;//计数器复位到3.cnt_pwd <= 3'b100;//密码次数计数器复位到4.lock <= 1'b1;//开锁.endelse if(cfm_dbs && lock)begin//按下确认键,此处用的消抖后的脉冲信号.若程序锁已锁,此下代码均不会再被执行.if(cnt_pwd == 3'b000)beginif(input_pwd[0] == password[0] && input_pwd[1] == password[1] && input_pwd[2] == password[2] && input_pwd[3] == password[3])begin//密码正确.sgn <= 2'b10;//绿灯亮.seg_data[0] <= 9'h40;//密码输入正确后两根数码管显示两根横线.seg_data[1] <= 9'h40;//因为横线显示只在此处使用,故没有写入seg数组中.lock <= 0;//程序锁死,防止解锁成功后还能进行操作.endelse if(cnt == 2'b11)beginsgn <= 2'b01;//红灯亮.seg_data[0] <= seg[2];//数码管显示数字2.cnt <= 2'b10;//计数器移至2.cnt_pwd <= 3'b100;seg_data[1] <= 9'h40;endelse if(cnt == 2'b10) beginsgn <= 2'b01;//红灯亮.seg_data[0] <= seg[1];//数码管显示数字1.cnt <= 2'b01;//计数器移至1.cnt_pwd <= 3'b100;seg_data[1] <= 9'h40;endelse if(cnt == 2'b01)beginsgn <= 2'b00;//红灯和绿灯同时亮seg_data[0] <= seg[0];//数码管显示数字0.seg_data[1] <= 9'h40;lock <= 0;//程序锁死.endend//输入密码并存储的操作else if(cnt_pwd > 3'b000)beginif(cnt_pwd == 3'b100)beginif(sw_pwd < 4'b1010)begininput_pwd[3] <= sw_pwd;cnt_pwd <= 3'b011;seg_data[1] <= seg[sw_pwd];endelse beginseg_data[1] <= 9'h40;endendif(cnt_pwd == 3'b011)beginif(sw_pwd < 4'b1010)begininput_pwd[2] <= sw_pwd;cnt_pwd <= 3'b010;seg_data[1] <= seg[sw_pwd];endelse beginseg_data[1] <= 9'h40;endendif(cnt_pwd == 3'b010)beginif(sw_pwd < 4'b1010)begininput_pwd[1] <= sw_pwd;cnt_pwd <= 3'b001;seg_data[1] <= seg[sw_pwd];endelse beginseg_data[1] <= 9'h40;endendif(cnt_pwd == 3'b001)beginif(sw_pwd < 4'b1010)begininput_pwd[0] <= sw_pwd;cnt_pwd <= 3'b000;seg_data[1] <= seg[sw_pwd];endelse beginseg_data[1] <= 9'h40;endendendend//如果当前输入错误,可以进行删除操作,删除后显示一条横线else if(cfm_del)beginif(cnt_pwd == 3'b011)begincnt_pwd <= 3'b100;seg_data[1] <= 9'h40;endif(cnt_pwd == 3'b010)begincnt_pwd <= 3'b011;seg_data[1] <= 9'h40;endif(cnt_pwd == 3'b001)begincnt_pwd <= 3'b010;seg_data[1] <= 9'h40;endif(cnt_pwd == 3'b000)begincnt_pwd <= 3'b001;seg_data[1] <= 9'h40;end end//如果解锁成功,可以进行修改密码操作else if(cfm_dbs1 && !lock)beginconfirm <= 1'b1;lock <= 1'b0;//锁死.cnt_pwd <= 3'b100;//设置为4次led_blue <= 1'b0;//蓝灯亮end//保险操作,本人感觉可以不写else if(cfm_dbs1 && confirm == 1'b1)beginsgn <= 2'b11;//两灯均灭.led_blue <=1'b1;//蓝灯灭seg_data[0] <= seg[3];//第一根显示数字3.seg_data[1] <= 9'h40;//第二根显示一根横线.cnt <= 2'b11;//计数器复位到3.cnt_pwd <= 3'b100;//密码次数计数器复位到4.lock <= 1'b1;//开锁.end//修改密码操作else if(confirm == 1'b1)beginif(cfm_dbs && !lock)beginif(cnt_pwd >= 3'b000)beginif(cnt_pwd == 3'b100)beginif(sw_pwd < 4'b1010)beginpassword[3] <= sw_pwd;cnt_pwd <= 3'b011;seg_data[1] <= seg[sw_pwd];endelse beginseg_data[1] <= 9'h40;endendif(cnt_pwd == 3'b011)beginif(sw_pwd < 4'b1010)beginpassword[2] <= sw_pwd;cnt_pwd <= 3'b010;seg_data[1] <= seg[sw_pwd];endelse beginseg_data[1] <= 9'h40;endendif(cnt_pwd == 3'b010)beginif(sw_pwd < 4'b1010)beginpassword[1] <= sw_pwd;cnt_pwd <= 3'b001;seg_data[1] <= seg[sw_pwd];endelse beginseg_data[1] <= 9'h40;endendif(cnt_pwd == 3'b001)beginif(sw_pwd < 4'b1010)beginpassword[0] <= sw_pwd;cnt_pwd <= 3'b000;seg_data[1] <= seg[sw_pwd];sgn <= 2'b00;//红灯和绿灯同时亮endelse beginseg_data[1] <= 9'h40;endendif(cnt_pwd == 3'b000)beginsgn <= 2'b11;//两灯均灭.led_blue <=1'b1;//蓝灯灭seg_data[0] <= seg[3];//第一根显示数字3.seg_data[1] <= 9'h40;//第二根显示一根横线.cnt <= 2'b11;//计数器复位到3.cnt_pwd <= 3'b100;//密码次数计数器复位到4.lock <= 1'b1;//开锁.confirm <= 1'b0;endendendelse if(cfm_del)beginif(cnt_pwd == 3'b011)begincnt_pwd <= 3'b100;seg_data[1] <= 9'h40;endif(cnt_pwd == 3'b010)begincnt_pwd <= 3'b011;seg_data[1] <= 9'h40;endif(cnt_pwd == 3'b001)begincnt_pwd <= 3'b010;seg_data[1] <= 9'h40;endif(cnt_pwd == 3'b000)begincnt_pwd <= 3'b001;seg_data[1] <= 9'h40;end endendendassign led = sgn;//绿灯亮代表密码正确,红灯反之.assign sega = seg_data[0];//第一根数码管通过输入信号变化改变数值assign segb = seg_data[1];//第二根数码管其实一直显示数字0assign blue = led_blue;debounce key_cfm_dbs (//调用消抖模块,用以消抖确认键..clk (clk),.rst (rst),.key (key_cfm),.key_pulse (cfm_dbs));debounce key1_cfm_dbs (//调用消抖模块,用以消抖确认键..clk (clk),.rst (rst),.key (key1_cfm),.key_pulse (cfm_dbs1));debounce key_cfm_del (//调用消抖模块,用以消抖确认键..clk (clk),.rst (rst),.key (key_del),.key_pulse (cfm_del));endmodule

代码小细节,在确认密码的时候增加了一个判断,即每一位不能大于9,大于9输入无效,显示横线。

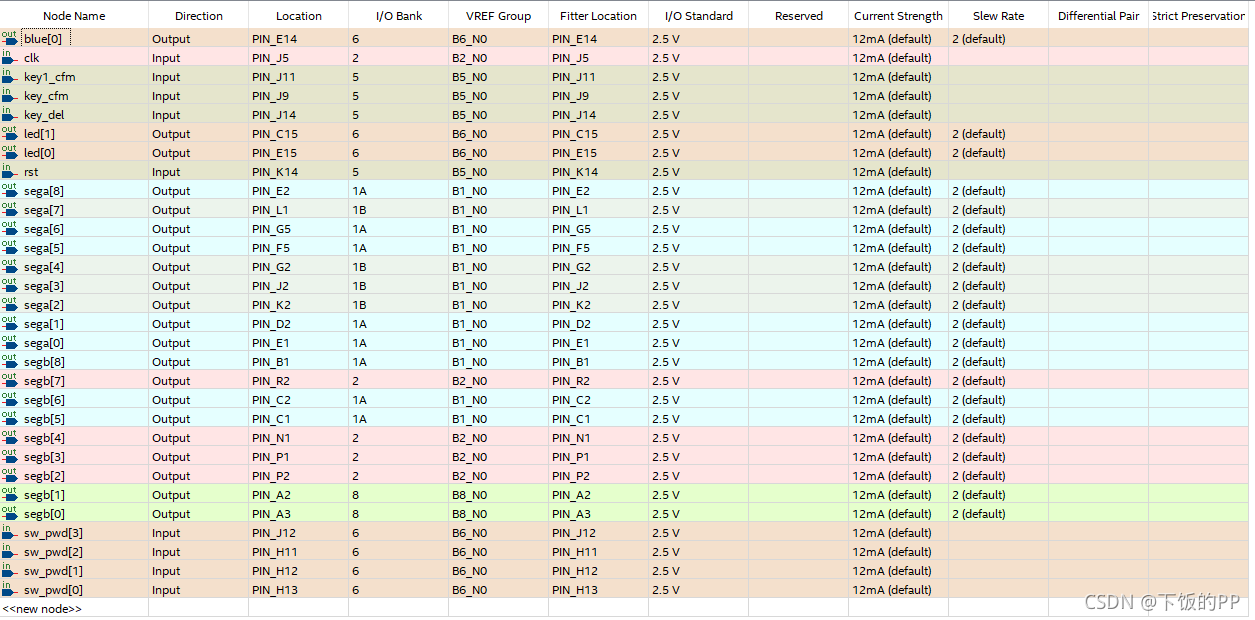

引脚分配:

本次总结就到这里,欢迎与我讨论或指出我的错误,谢谢大家!