实验名称 电子琴设计—任务1

1.设计思路

预置分频比

音名 分频系数(3Mhz)

中音 高音

1 11468 5736

2 10215 5111

3 9102 4552

4 8591 4289

5 7653 3827

6 6818 3409

7 6073 3037

理论频率对照表

音名 频率(Hz)

中音 高音

1 261.63 523.25

2 293.66 587.33

3 329.63 659.26

4 349.23 698.46

5 392.00 784.00

6 440.00 880.00

7 493.88 987.77

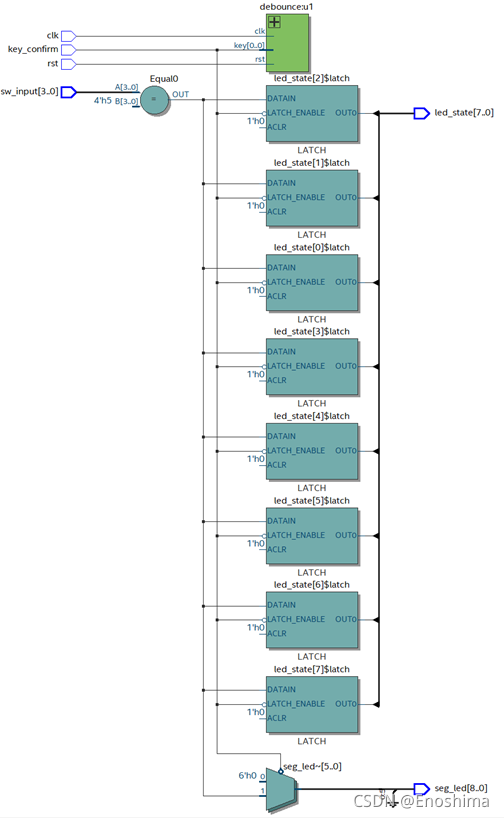

由“十二平均率”的规定,计算得到中音1到高音1每个音名名对应的频率如右表。以上12种频率的信号都可以由一个基准频率分频得到。由于分频系数不能为小数,故必须将分频系数取整(这必然会产生误差),所以基准频率大小的会影响误差的大小。基准频率过小,取整后的误差过大,所以基准频率应该要大。

但是过大的基准频率,导致分频系数也会很大。所以,综合考虑两方面的因素,我们选择6Mhz的基准频率(实验箱上的CLK0可以直接提供)。表中的分频比是由6Mhz二分频得到的3Mhz的基础上计算得到的。然后根据输入的不同,将预置的分频比送入分频器中,就可以得到对应频率的音符。

通过八段数码管显示高中音的音名(高音有小数点,中音没有,以此来区分)。

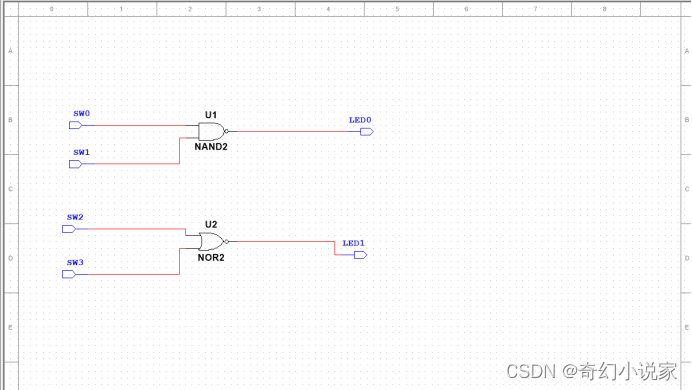

2.程序代码

//顶层文件

module lyj_3501_7(clk_in,clr,key,clk_out,clk_out_1,seg,codeout);//输入

input [13:0]key;//14个琴键输入

input clk_in;//时钟为6Mhz

input clr;//复位信号//输出

output reg clk_out;//分频器信号输出

output clk_out_1;//与clk_out一致

output [7:0] codeout;//八段数码管

output seg;//数码管位选选信号//内部变量

reg [13:0]divider;//分屏系数

reg [13:0]cnt;//计数器

reg flag;assign clk_out_1=clk_out;//与clk_out一致always@(posedge clk_in or posedge clr)

beginif(clr)//异步复位,高电平有效beginflag<=1;cnt<=0;endelse beginif(cnt<divider)begincnt<=cnt+1'b1;flag<=1'b0;endelsebeginflag<=1'b1;cnt<=1'b0;endend

endalways@(posedge flag)

begin//flag==1表示计数满,则波形反转if(clr)clk_out<=0;elsebeginif(key!=0)clk_out<=~clk_out;//得到50%占空比的方波信号elseclk_out<=1'd0;end

endalways@(key)

begincase(key)//根据不同的音符,预置分频比14'b0000_000_0000_000:divider<=0;14'b1000_000_0000_000:divider<=14'd11468;14'b0100_000_0000_000:divider<=14'd10215;14'b0010_000_0000_000:divider<=14'd9102;14'b0001_000_0000_000:divider<=14'd8591;14'b0000_100_0000_000:divider<=14'd7653;14'b0000_010_0000_000:divider<=14'd6818;14'b0000_001_0000_000:divider<=14'd6073;14'b0000_000_1000_000:divider<=14'd5736;14'b0000_000_0100_000:divider<=14'd5111;14'b0000_000_0010_000:divider<=14'd4552;14'b0000_000_0001_000:divider<=14'd4289;14'b0000_000_0000_100:divider<=14'd3827;14'b0000_000_0000_010:divider<=14'd3409;14'b0000_000_0000_001:divider<=14'd3037;default:divider<=0;endcase

endlyj_3501_6_b u1(key,codeout,seg);//显示模块

endmodulemodule lyj_3501_6_b(key,codeout,seg);//译码器模块

input [13:0] key;

output reg[7:0] codeout;

output seg;assign seg=1'b1;//数码管位选信号always@ (key)

begincase(key)14'b1000_000_0000_000:codeout=8'b0_0000110;//中音114'b0100_000_0000_000:codeout=8'b0_1011011;//中音214'b0010_000_0000_000:codeout=8'b0_1001111;//中音314'b0001_000_0000_000:codeout=8'b0_1100110;//中音414'b0000_100_0000_000:codeout=8'b0_1101101;//中音514'b0000_010_0000_000:codeout=8'b0_1111101;//中音614'b0000_001_0000_000:codeout=8'b0_0000111;//中音714'b0000_000_1000_000:codeout=8'b1_0000110;//高音114'b0000_000_0100_000:codeout=8'b1_1011011;//高音214'b0000_000_0010_000:codeout=8'b1_1001111;//高音314'b0000_000_0001_000:codeout=8'b1_1100110;//高音414'b0000_000_0000_100:codeout=8'b1_1101101;//高音514'b0000_000_0000_010:codeout=8'b1_1111101;//高音614'b0000_000_0000_001:codeout=8'b1_0000111;//高音714'b0000_000_0000_000:codeout=8'b1_1111111;//休止符default:codeout=8'b1_0111111;//0endcase

end

endmodule

//测试文件

`timescale 1ns / 1ns//时间单位/时间精度

module test_lyj_3501_6;

reg clk_in,clr;

reg [13:0]key;

wire seg;

wire [7:0]codeout;

wire clk_out_1,clk_out;

//

integer i;

//

lyj_3501_7 test_a(.clk_in(clk_in),.clr(clr),.key(key),.clk_out(clk_out),.clk_out_1(clk_out_1),.seg(seg),.codeout(codeout));

//

always #83 clk_in=~clk_in;//近似为6Mhz的时钟

//

initial

begini=14;clk_in=1'b0;clr=1'b1;key=14'd0;#1000clr=1'b0;#1000press_13to0;

endtask press_13to0;//每个按键按至少3个周期的时间repeat(14)begini=i-1;key=14'd0; #1_000_000key[i]=1'b1;#12_000_000key=14'd0; end

endtask endmodule

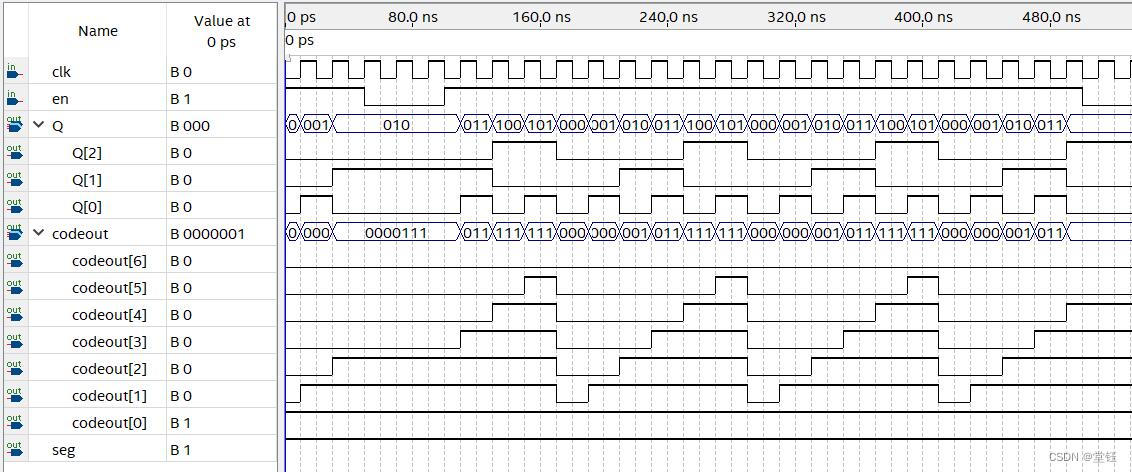

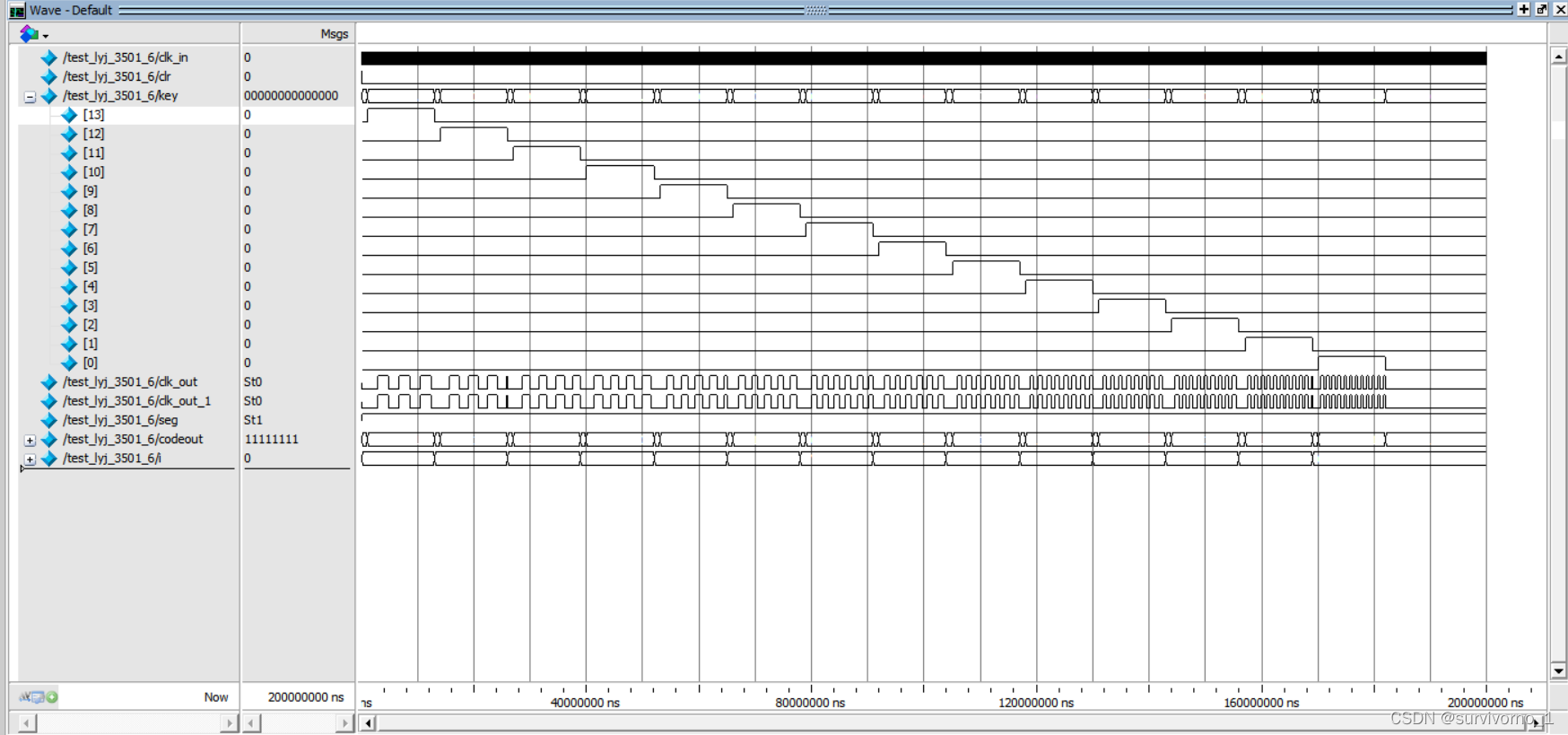

3.仿真波形图

音名 中音 高音

仿真周期(ns) 仿真频率(hz) 误差 仿真周期(ns) 仿真频率(hz) 误差

1 3807708 262.6251 0.38% 1904684 525.0214 0.34%

2 3391712 294.8363 0.40% 1697184 589.2113 0.32%

3 3022196 330.8852 0.38% 1511596 661.5524 0.35%

4 2852544 350.5642 0.38% 1424280 702.1091 0.52%

5 2541128 393.5260 0.39% 1270896 786.8464 0.36%

6 2263908 441.7140 0.39% 1132120 883.2985 0.37%

7 2016568 495.8920 0.41% 1008616 991.4576 0.37%

误差在允许范围内

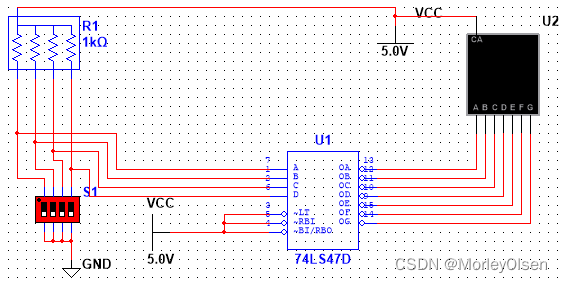

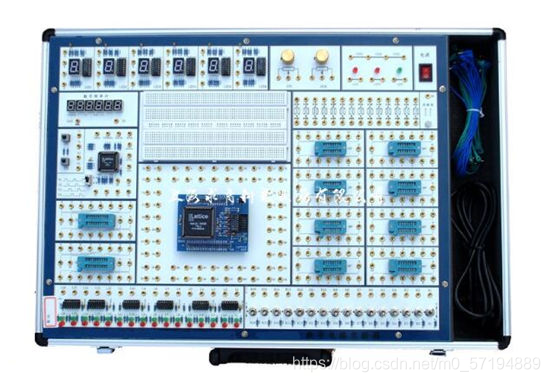

二、引脚分配表(电路中的信号名称->主板器件名称->引脚号PIN)

信号名 主板器件 PIN 信号名 主板器件 PIN

key[13] Key13 PIN_7 codeout[0] a PIN_112

key[12] Key12 PIN_8 codeout[1] b PIN_100

key[11] Key11 PIN_144 codeout[2] c PIN_104

key[10] Key10 PIN_6 codeout[3] d PIN_111

key[9] Key9 PIN_13 codeout[4] e PIN_106

key[8] Key8 PIN_43 codeout[5] f PIN_110

key[7] Key7 PIN_44 codeout[6] g PIN_103

key[6] Key6 PIN_39 codeout[7] h PIN_105

key[5] Key5 PIN_42 seg SEG0 PIN_119

key[4] Key4 PIN_32 clk_out 扬声器 PIN_128

key[3] Key3 PIN_33 clk_out_1 LED0/IO0 PIN_46

key[2] Key2 PIN_30

key[1] Key1 PIN_31

key[0] Key0 PIN_24

clk_in Clk0 PIN_88

clr Key17 PIN_137

参考资料:

王金明,徐志军,苏勇.《EDA技术与Verilog HDL设计》[M]:电子工业出版社,2013