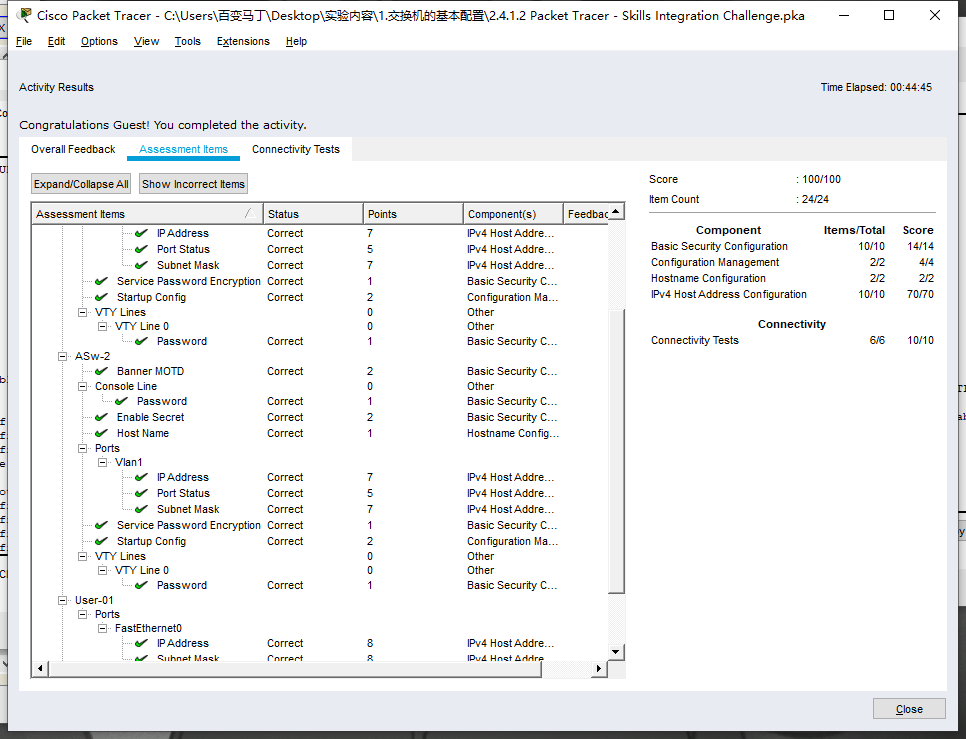

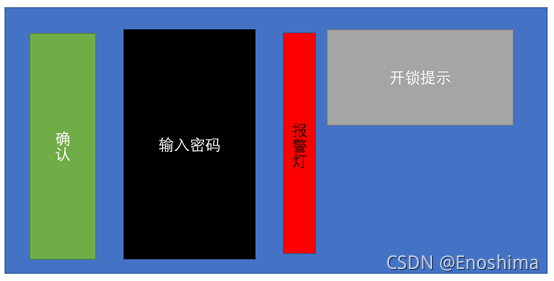

1.设计理念

通过拨动开关输入由四位二进制表示的密码,然后按键确认输入并校验。

如果校验通过,则led不亮,数码led显示0提示开锁。

如果校验失败,则数码led不亮,led全亮,启动报警,直到输入正确密码并再次确认校验成功后,led灭,数码led显示0提示开锁。

安全性:

- 开锁成功或失败提示明显;

- 密码组合一共16种供选择。但一旦输入错误便进入报警模式;

- 需要确认输入,避免意外误触;

视频见附件。

2.代码

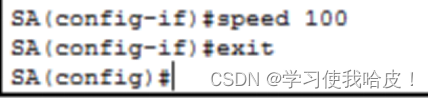

(1) my_codelock.v

module my_codelock(seg_led, //数码led_state,key_confirm,sw_input, //led,开关,按键clk,rst //消抖需要的输入);input key_confirm; //按键=确认input [3:0] sw_input; //拨动开关=输入密码output [7:0] led_state;reg [7:0] led_state; //led表示状态reg [8:0] seg_led;output [8:0] seg_led; //数码管提示正确打开 input clk,rst; always@(*)beginseg_led=9'h00;if (key_confirm==0)begin //当按下确认开始校对if (sw_input==4'b0101) beginled_state=8'b1111_1111; //如果密码正确,那就不亮led亮数码板seg_led=9'h3f; endelse beginled_state=8'b0000_0000;endendenddebounce u1 ( .clk (clk),.rst (rst),.key (key_confirm),.key_pulse ());endmodule

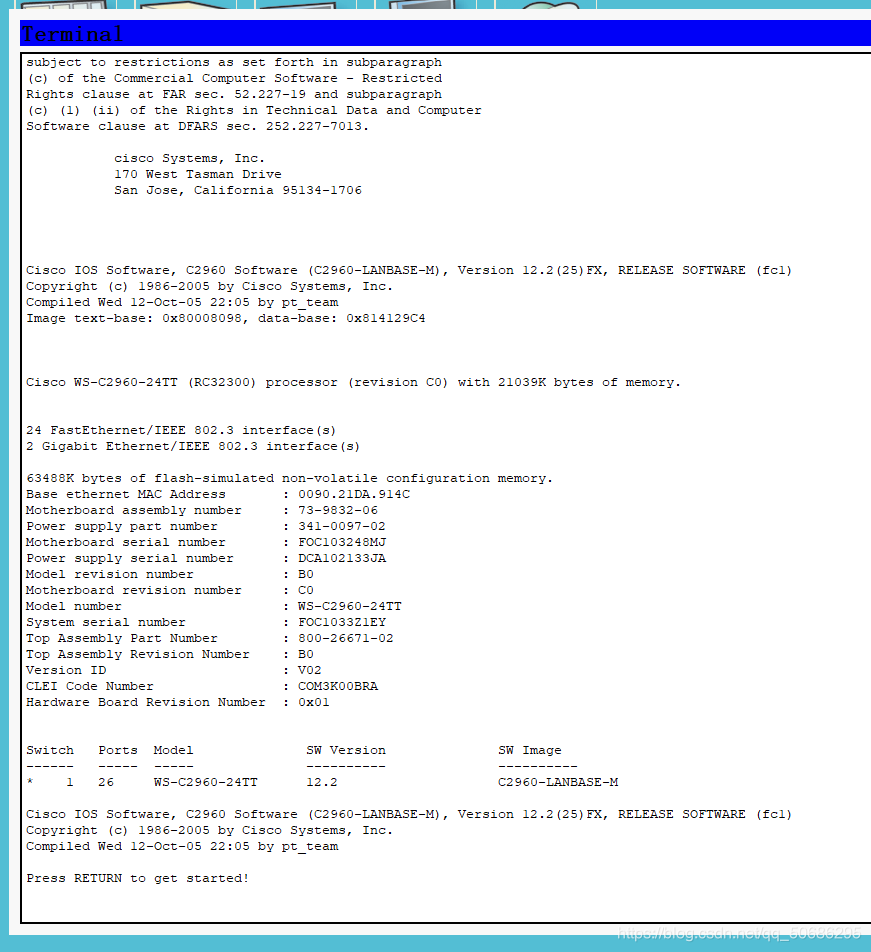

(1) debounce.v

module debounce (clk,rst,key,key_pulse);parameter N = 1; //要消除的按键的数量input clk;input rst;input [N-1:0] key; //输入的按键 output [N-1:0] key_pulse; //按键动作产生的脉冲 reg [N-1:0] key_rst_pre; //定义一个寄存器型变量存储上一个触发时的按键值reg [N-1:0] key_rst; //定义一个寄存器变量储存储当前时刻触发的按键值wire [N-1:0] key_edge; //检测到按键由高到低变化是产生一个高脉冲//利用非阻塞赋值特点,将两个时钟触发时按键状态存储在两个寄存器变量中always @(posedge clk or negedge rst)beginif (!rst) beginkey_rst <= {N{1'b1}}; //初始化时给key_rst赋值全为1,{}中表示N个1key_rst_pre <= {N{1'b1}};endelse beginkey_rst <= key; //第一个时钟上升沿触发之后key的值赋给key_rst,同时key_rst的值赋给key_rst_prekey_rst_pre <= key_rst; //非阻塞赋值。相当于经过两个时钟触发,key_rst存储的是当前时刻key的值,key_rst_pre存储的是前一个时钟的key的值end endassign key_edge = key_rst_pre & (~key_rst);//脉冲边沿检测。当key检测到下降沿时,key_edge产生一个时钟周期的高电平reg [17:0] cnt; //产生延时所用的计数器,系统时钟12MHz,要延时20ms左右时间,至少需要18位计数器 //产生20ms延时,当检测到key_edge有效是计数器清零开始计数always @(posedge clk or negedge rst)beginif(!rst)cnt <= 18'h0;else if(key_edge)cnt <= 18'h0;elsecnt <= cnt + 1'h1;end reg [N-1:0] key_sec_pre; //延时后检测电平寄存器变量reg [N-1:0] key_sec; //延时后检测key,如果按键状态变低产生一个时钟的高脉冲。如果按键状态是高的话说明按键无效always @(posedge clk or negedge rst)beginif (!rst) key_sec <= {N{1'b1}}; else if (cnt==18'h3ffff)key_sec <= key; endalways @(posedge clk or negedge rst)beginif (!rst)key_sec_pre <= {N{1'b1}};else key_sec_pre <= key_sec; end assign key_pulse = key_sec_pre & (~key_sec); endmodule

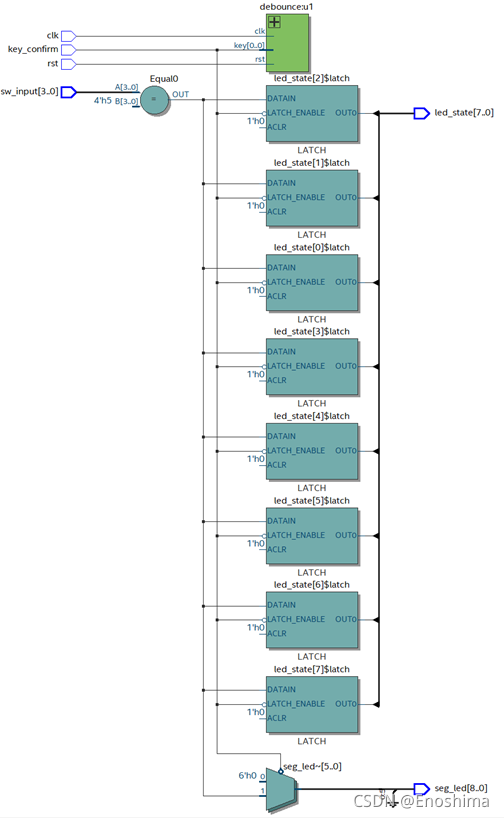

3.RTL电路