相关文章

74161/74LS161 四位二进制同步计数器

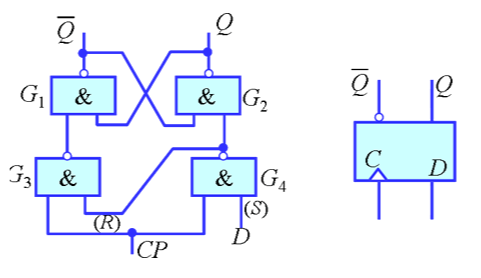

逻辑符号 功能表 异步清零,同步置数 输出数范围为0000~1111 当Q0~Q3全为1时,C输出1表示进位

用74161计数器芯片 设计十二进制计数器

用74161计数器芯片 设计十二进制计数器

一.实验内容 1.利用74161计数器芯片设计一个M12的计数器 2.利用Quartus软件进行设计和仿真 3.观察仿真波形

二.实验步骤 1,新建工程 2,新建BDF文件,双击空白处搭建电路 3,新建vwf文件&am…

利用74161计数器芯片设计二十进制的计数器

利用74161计数器芯片设计M20的计数器

一.实验内容 1.利用74161计数器芯片设计一个M20的计数器 2.利用Quartus软件进行设计和仿真 3.观察仿真波形

二.实验步骤 1,新建工程 2,新建bdf文件 3,双击空白处搭建电路:

4,对…

quartus仿真32:74161构成的模7计数器

异步清零法,从0计数到6然后利用过渡态7完成清零操作同步置零法,计数到6时输出一个置位信号,将准备的数字0000输入到计数器中清零和置数的控制端输入相当于对计数数字的译码的过程清零法很遗憾的是有毛刺导致只能计数4个状态,置零法…

EDA数字钟--由(两片74161做成的六十进制计数器)问题总结

六十进制计数器 十二进制计数器 数字钟 问题波形 原因分析

实际的真值表 要求的真值表

09波形时间太短 六十进制计数器 当EN0是 并且LDN0时 遇到上升沿后74161清零 ,与EN0保持 相矛盾 2. 改进方案 为清零时,添加EN的约束 即EN1时才能进行清零操作

74161-可预置任意进制计数器(基于QuartusII实现)

1、 使用74161设计一个可预置的任意进制计数器,使用QuartusII 完成创建工程、编辑电路图、编译,编辑波形文件仿真,记录波形并说明仿真结果,最后在FPGA上进行硬件测试。

原理:如图所示。预置数为0000,当计数…

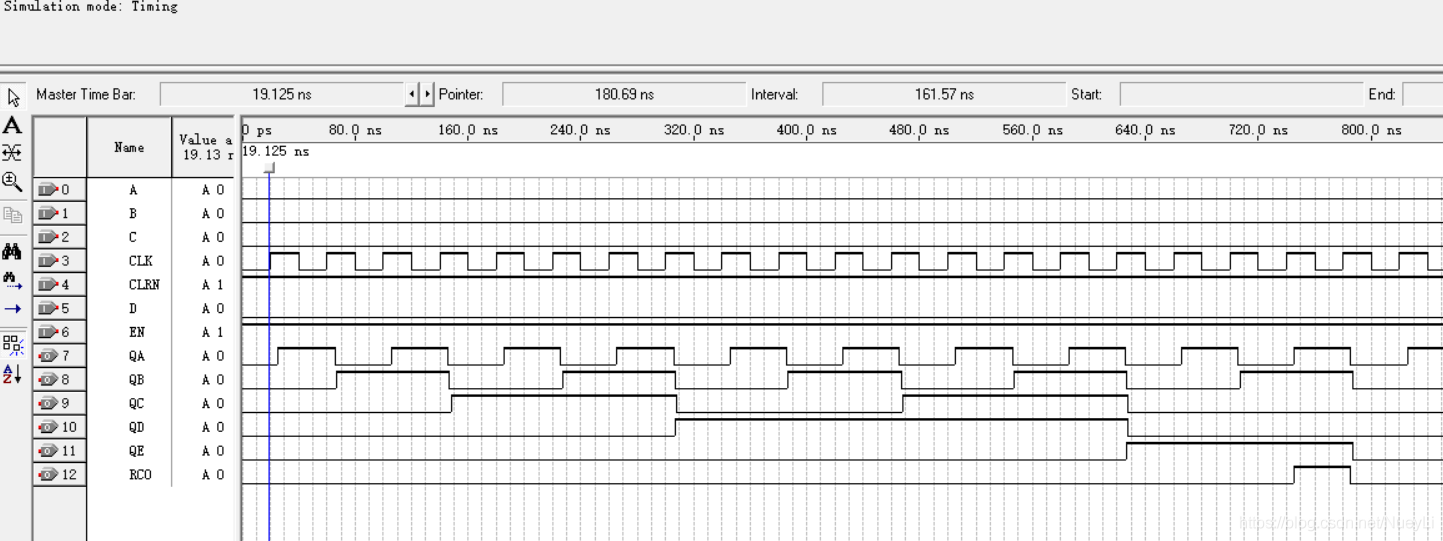

使用Quartus II9.0验证74161计数器

使用Quartus II9.0验证74161计数器

首先使用Quartus,新建一个项目New Quartus Project,创建一个BDF文件,双击BDF空白处,添加组件符号。 然后编译一次,新建一个vwf,矢量波形仿真文件,双击name下空白处&…

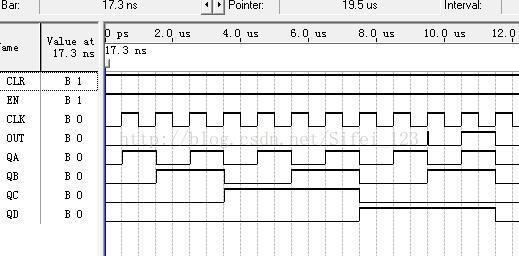

使用Quartus II9.0实现用74161计数器设计一个12进制的计数器

用161计数器芯片,设计一个M12的计数器

因为我们知道74161是16进制计数器,16>12,所以我们用一个74161计数器采用置零法或者置数法设计一个12进制计数器,这里我们采用置数法。

因为74161是同步置数,所以计数器会从0…

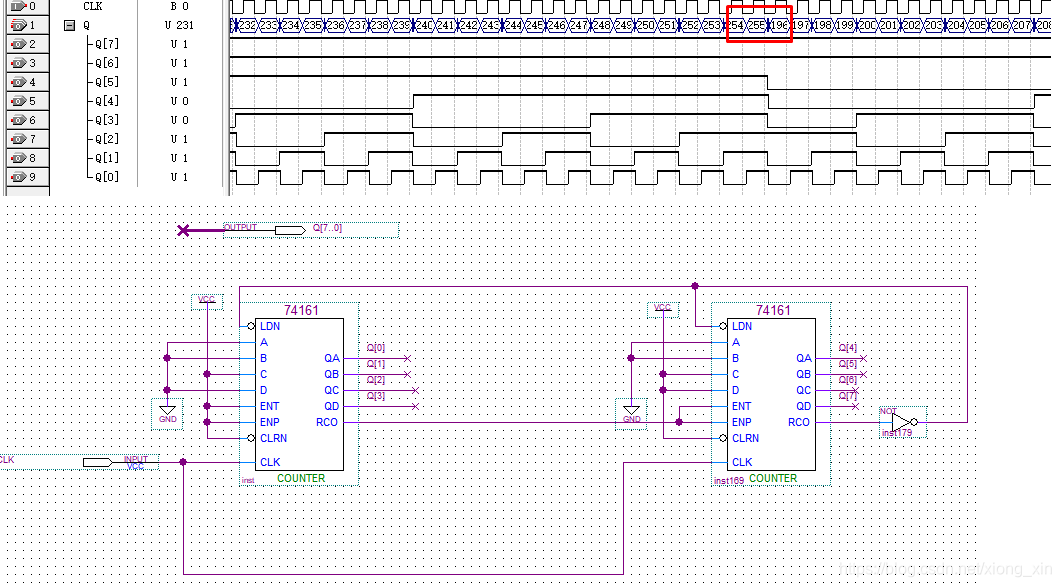

使用Quartus II9.0实现用74161计数器设计一个20进制的计数器

用74161计数器芯片设计一个20进制的计数器

因为我们知道74161是16进制计数器,16<20,所以我们要用2个74161计数器,可以将一个74161变为二进制,一个74161变为10进制从而完成设计。事实上,采用74160计数器将更加方便&…

quartus仿真33:74161级联实现模60计数器

将60分解成6*10,分别用74161实现模6和模10计数器,再级联成模60计数器利用OC进位端反相得到的信号输入到置位端,模6计数器的实现15-X16,解得置数端需要准备的数为X101010,模10计数器的实现15-X110,解得置数端…

初识FPGA:用FPGA进行简单74138、74161电路设计

一、用2片3-8 译码器拼接成4-16 译码器

1、3-8译码器功能表 2、实现原理图 采用两个3-8译码器上片为高八位,下片低八位。输入为INA、INB、INC、IND(由低到高位),EN0。IND0时,下片工作;IND1时,上片工作…

74161设计二十进制计数器

1. 2^4<20<2^8,因此在设计中要用到两片74161芯片。

2. 新建BDF文件,保存工程。

3.将所需要的元器件和引脚拖入区域内并完成连接,如图1所示 图1. 二十进制计数器连接图

4.建立VWF文件,仿真后得到结果如图2 图2、 仿真结…

用74161设计十二进制计数器

1.74161为十六进制计数器,设计十二进制计数器时1片就可以满足要求。

2.新建BDF文件及保存工程同前篇。

3.将所需要的元器件和引脚拖入区域内并完成连接,如图1所示 图1 十二进制计数器连接图

4.建立VWF文件,仿真后得到结果如图2

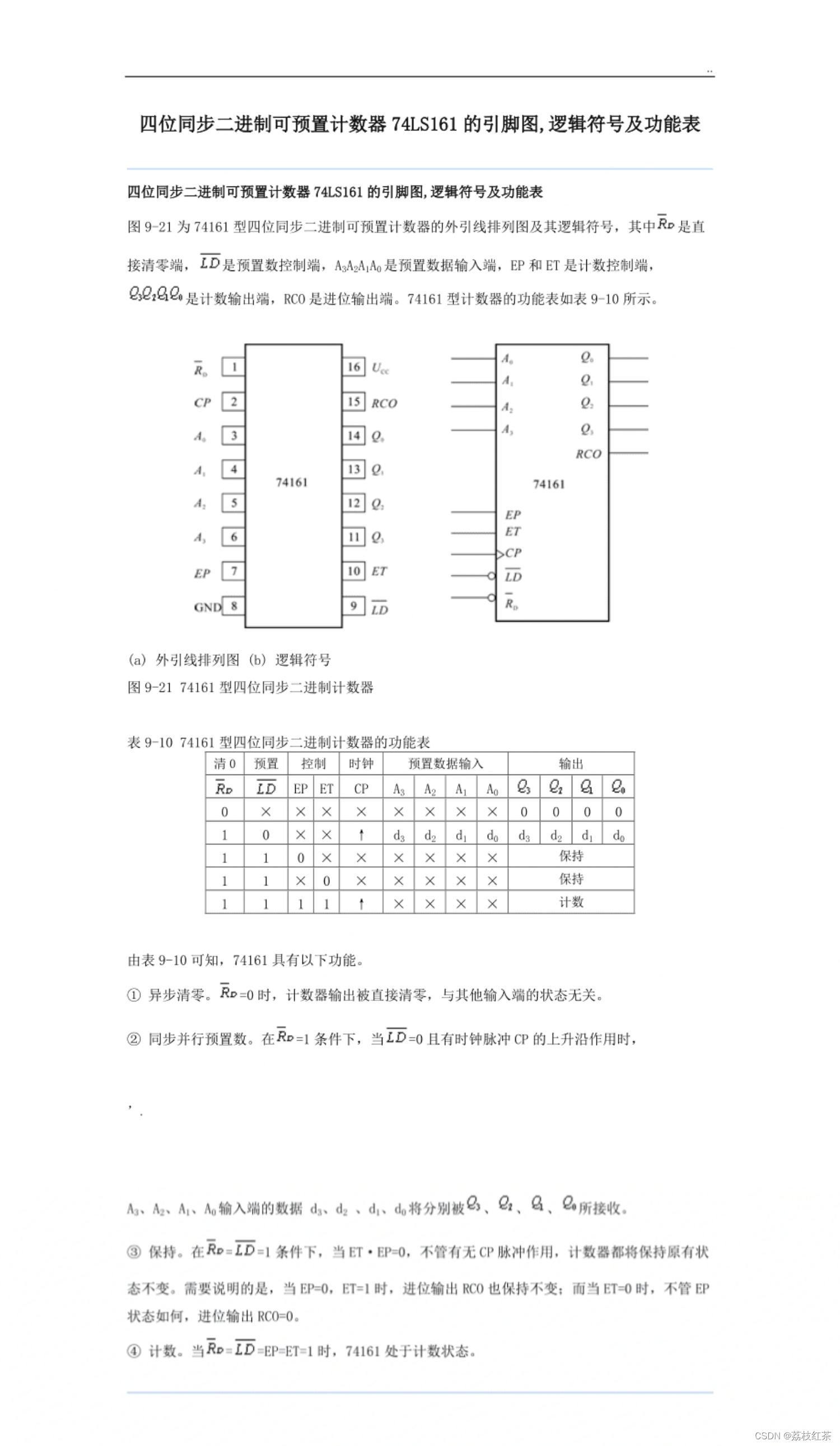

c语言实现同步四位加法计数器,试用4位同步二进制加法计数器74161才用置数法构成三进制计数器...

一是用时钟触发器和门电路进行设计; 二是用集成计数器构成。集成计数器一般都设有清零输入端和置数输入端,且无论是清零还是置数都有同步和异步之分,例如清零、置数均采用同步方式的有集成4位二进制同步加法计数器74163; 4位二进制…

用74161实现12进制与20进制

今天天气很不好,想起了我家那里,高三下午自习,有次外面突然开始刮气起大风,然后我就看着天空一点一点变黄,满天的沙尘,我们那里叫沙城可能就是由此而来的 吧,不过现在治理的沙尘暴已经近乎绝迹了…

quartus仿真34:74161构成长度为10的序列发生器

序列发生器构成有两种形式 计数器组合逻辑电路(译码器/多路选择器)移位寄存器构成的最大长度序列发生器74161是计数器,选第一种 产生1101000101序列的计数型序列信号发生器 确定模值,序列长度为10,需要模十计数器计数…

用二进制计数器集成芯片74161设计一个64进制计数器

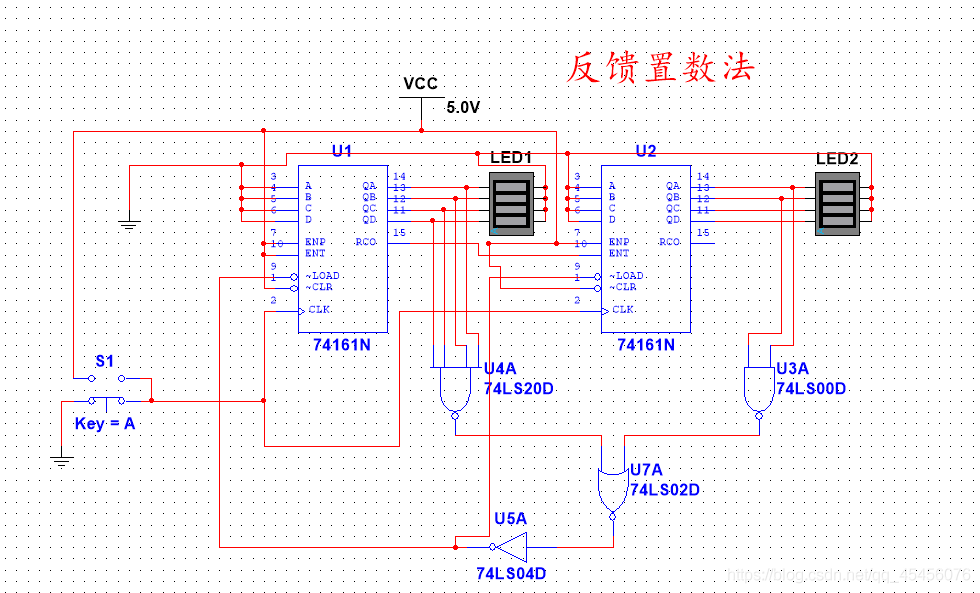

用二进制计数器集成芯片74161设计一个64进制计数器。要求分别用反馈清零法和反馈置数法实现。画出设计的电路图。

端口介绍:

A B C D为置数的数字输入端(其中D为最高位,A为最低位),在实现置数功能时会将ABCD的数值传…

quartus仿真31:74161的级联

74LS161是模16(四位二进制)同步集成计数器,异步清零一张功能表时刻准备查询 异步级联方法:将前一计数器的输出作为后一级计数器的时钟信号 两片161所需要的时钟不同称为异步前一级计数器的进位输出触发器输出的高位为何需要加反相…