基于FPGA的SDRAM初始化配置

- SDRAM简述

- SDRAM的引脚及作用

- SDRAM初始化时序控制

- SDRAM上电时序代码

- SDRAM测试模块的代码

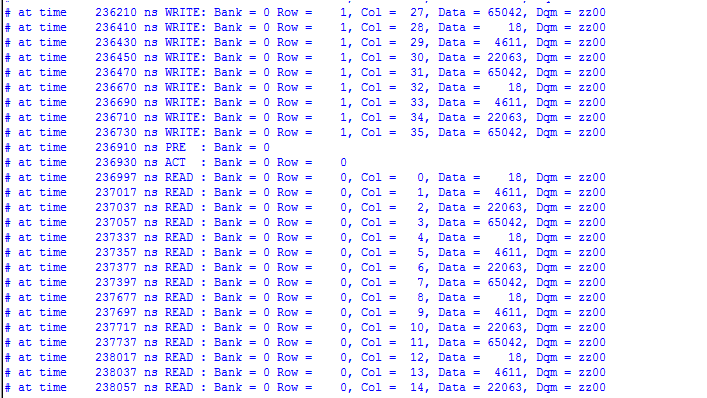

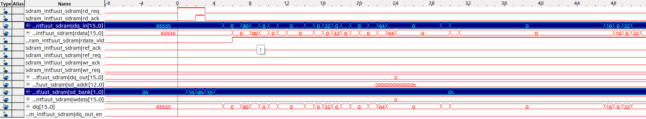

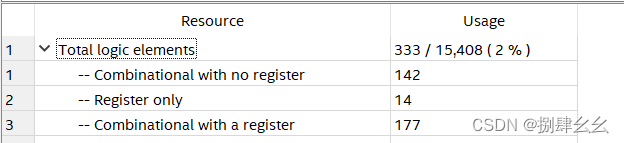

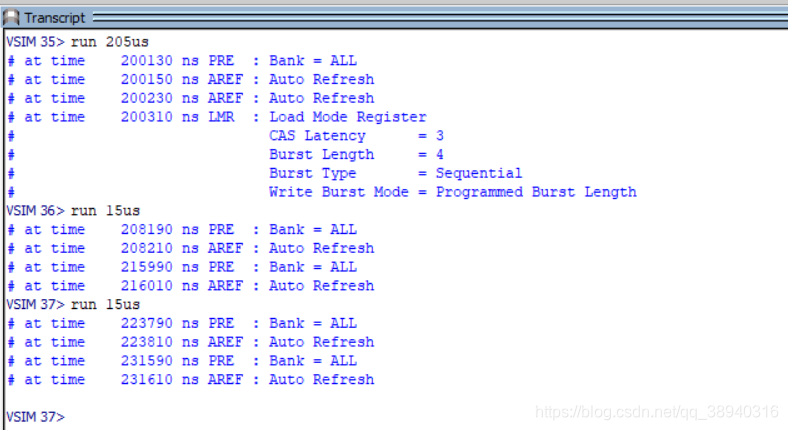

- 仿真测试结果

- 参考文献

- 总结

SDRAM简述

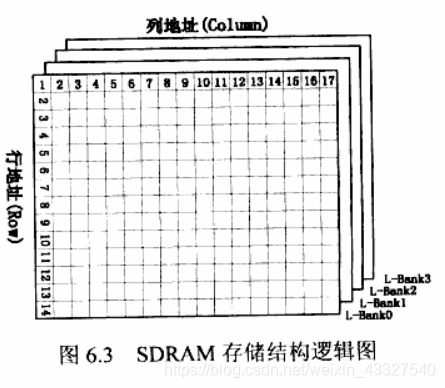

SDRAM( Synchronous Dynamic Random Access Memory),同步动态随机存储器。同步是指 Memory 工作需要同步时钟,内部的命令的发送与数据的传输都以它为基准;动态是指存储阵列需要不断的刷新来保证存储的数据不丢失,因为 SDRAM 中存储数据是通过电容来工作的,大家知道电容在自然放置状态是会有放电的,如果电放完了,也就意味着 SDRAM 中的数据丢失了,所以 SDRAM需要在电容的电量放完之前进行刷新;随机是指数据不是线性依次存储,而是自由指定地址进行数据的读写。

SDRAM作为FPGA处理吞吐量较大的数据时必须选择的存储器件,因为FPGA中存储空间有效。例如想存一张1080P的图片,单单靠FPGA本身的M9K或M18K是远远达不到的,所以我们要利用SDRAM作为缓存0。

要想确定这个存储单 元,只需要知道行地址( row address)和列地址( col address)与bank地址就可以

了,SDRAM总容量的计算公式如下:

SDRAM 容量 = 数据位宽 x 存储单元数量(行地址 x 列地址 x Bank 数)

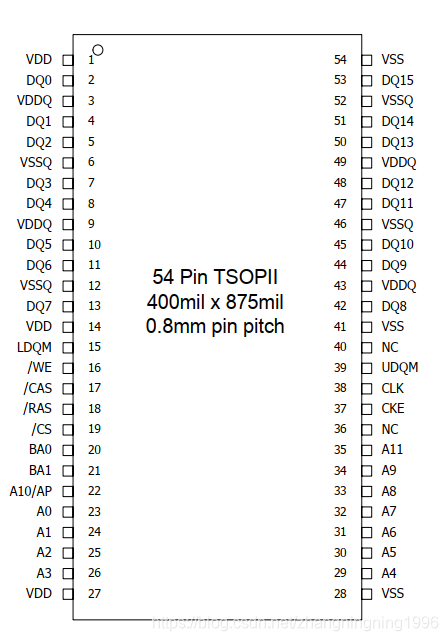

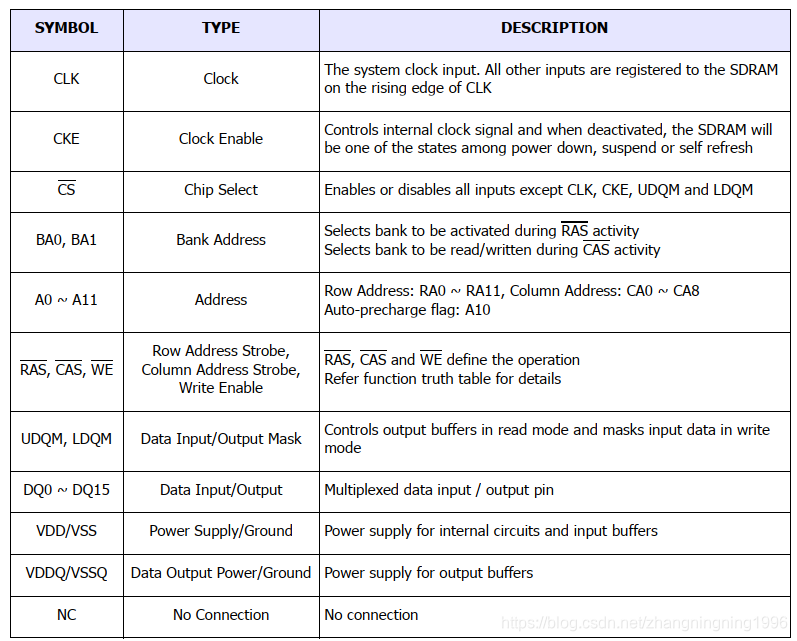

SDRAM的引脚及作用

从技术手册中很容易发现,SDRAM的常见的引脚及作用:

每个引脚的含义如下:

从上面我们很容易知道SDRAM的外设引脚及每个引脚的作用,这里如果还有不清出的地方可以去查找技术手册,SDRAM的技术手册比较简单。

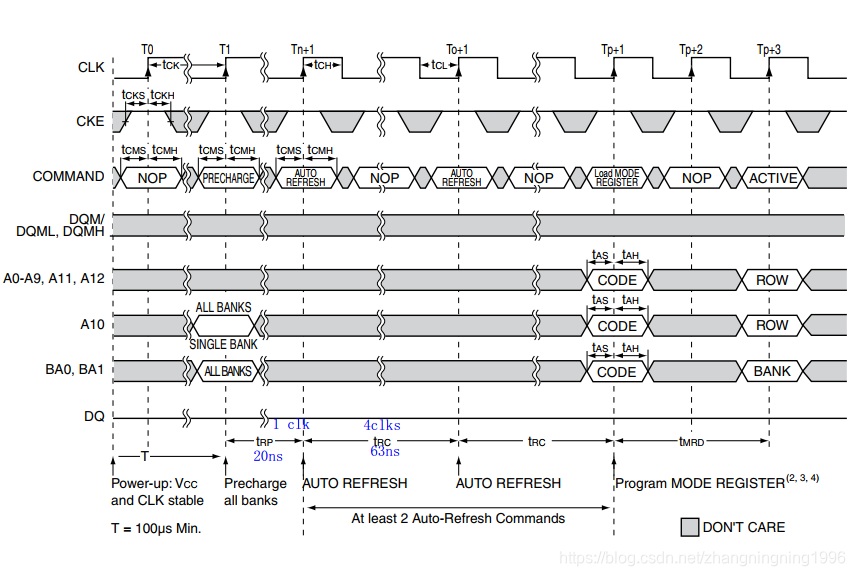

SDRAM初始化时序控制

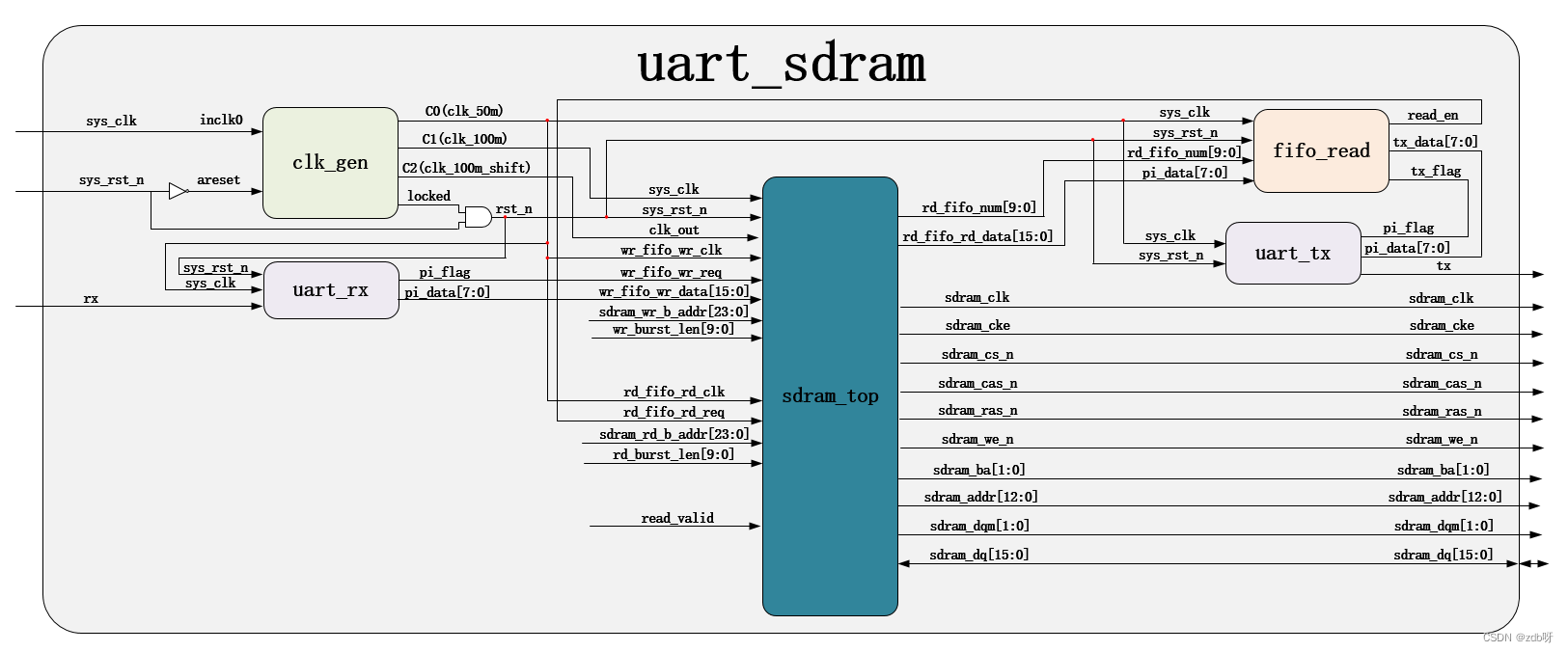

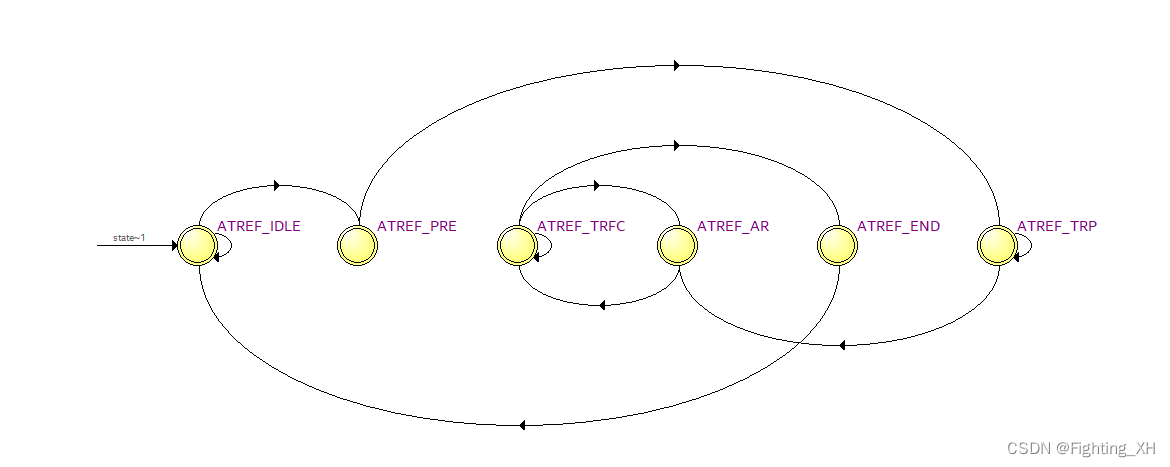

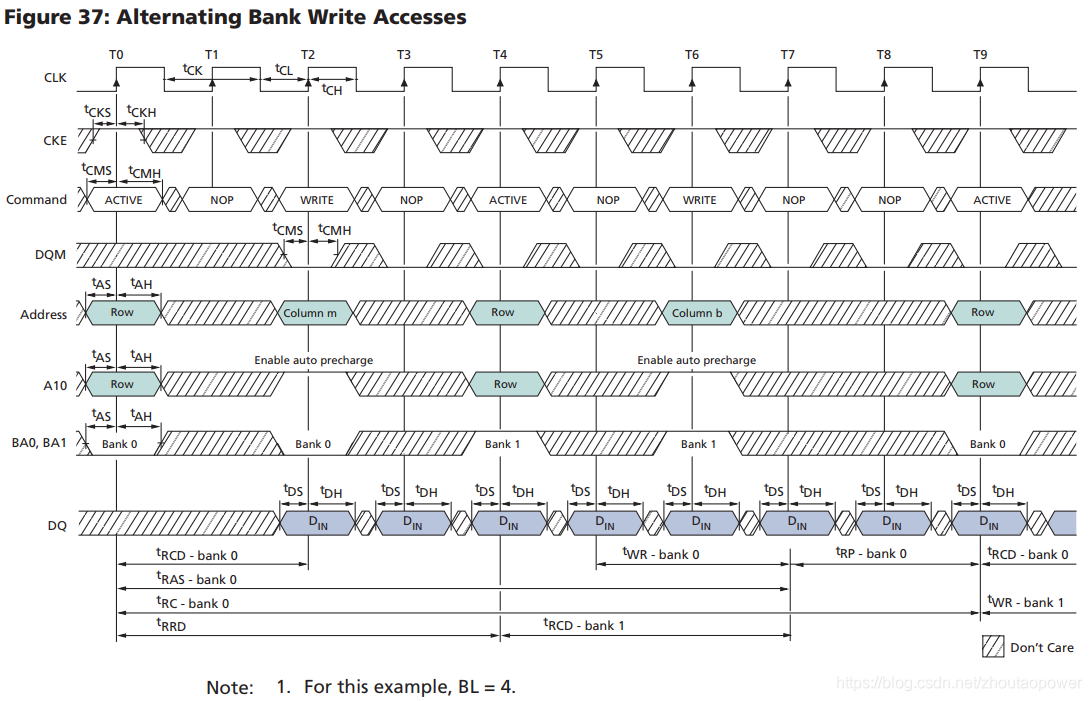

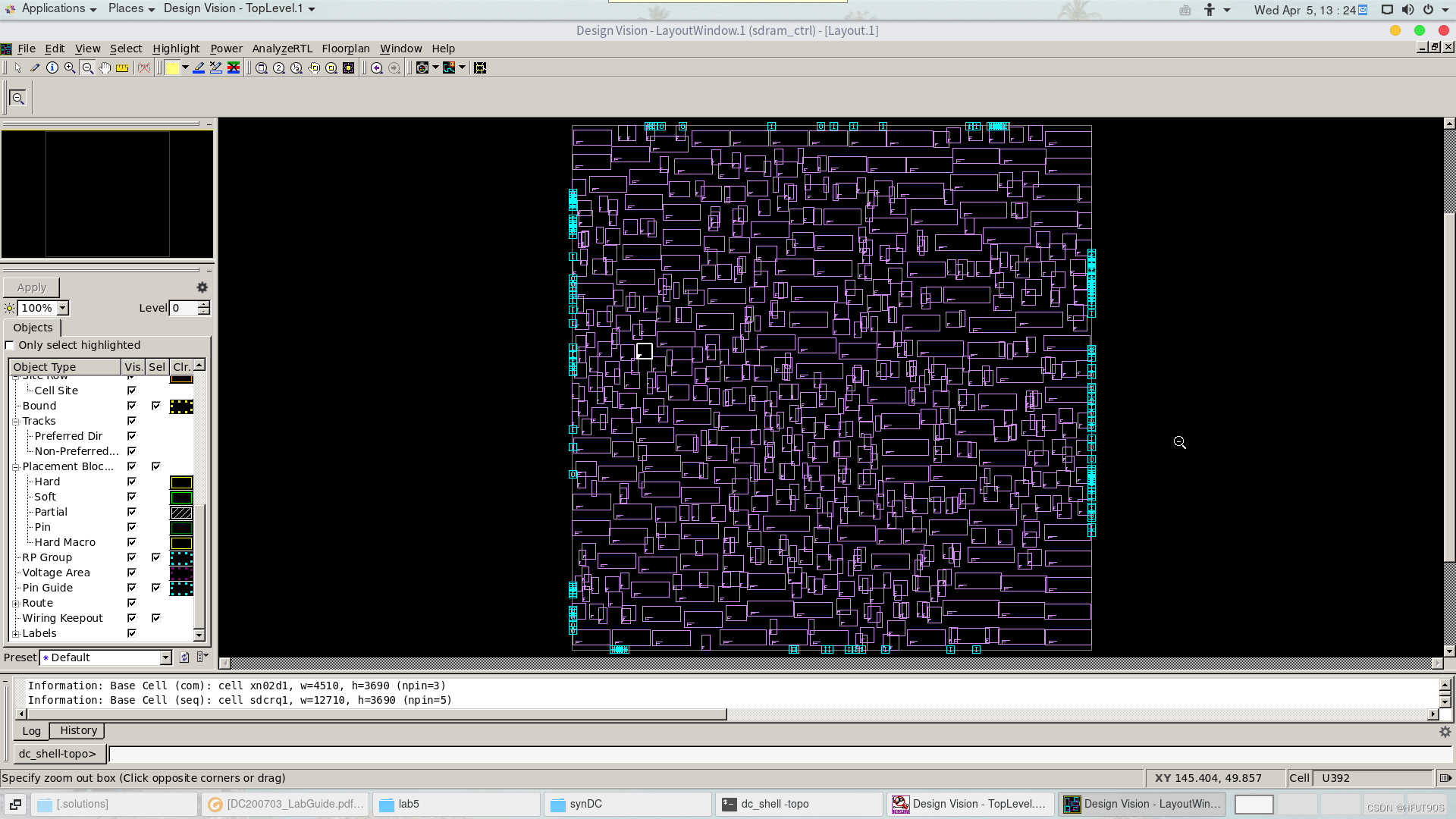

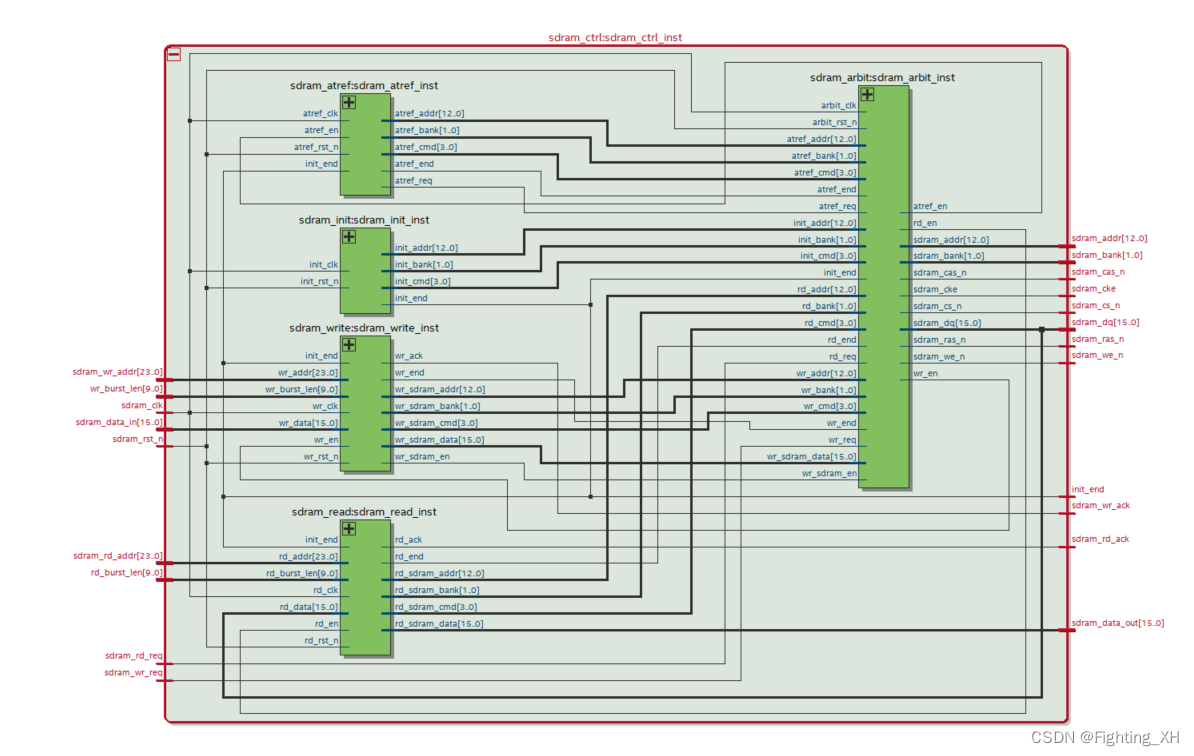

这里说明要写一个完整的SDRAM控制器需要五个模块,上电初始化模块、刷新模块、读模块、写模块、仲裁模块。首先能否独立写出SDRAM控制器是作为FPGA是否入门的一个很好的衡量措施。我们首先写SDRAM的初始化控制,这里查找技术手册可以知道,SDRAM上电初始化的空时时序如下:

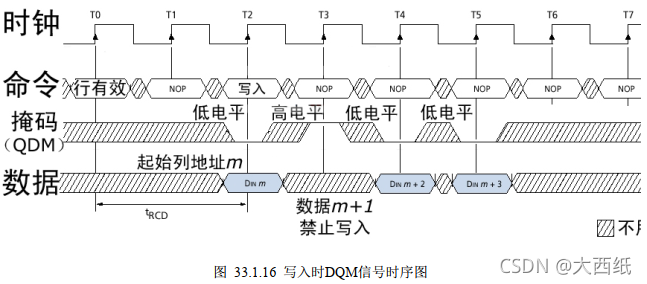

这里提醒一定要注意A10,因为该信号可以选择对单个bank操作还是对所有bank操作,而且在后面的读写操作中该信号还有控制状态机跳转的作用。

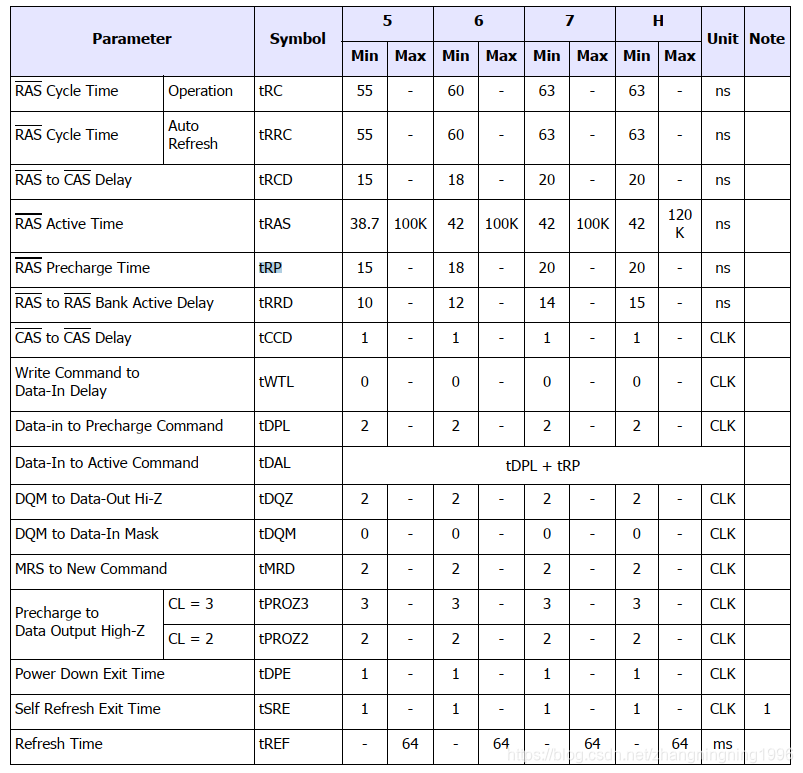

上面时间具体的值也可以查找技术手册:

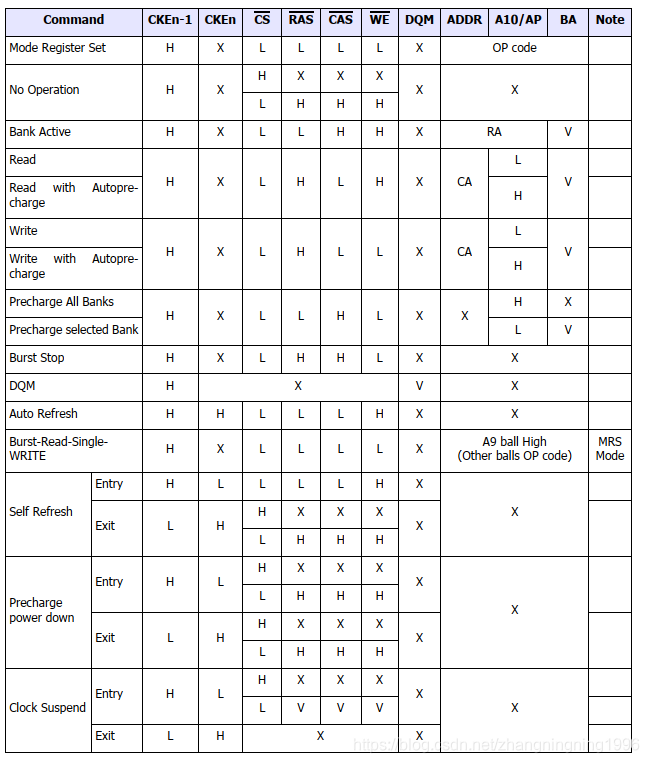

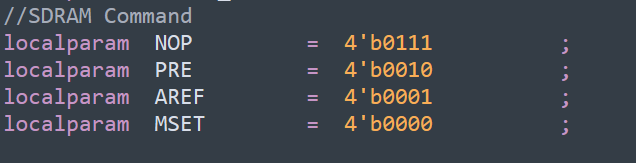

从图中我们可以看到COMMAND信号,该信号是由sdram的四个控制信号构成,即sdram_cs_n, sdram_ras_n, sdram_cas_n, sdram_we_n,具体每个命令的编码如下:

从上面的表格中,很容易解析出如下命令:

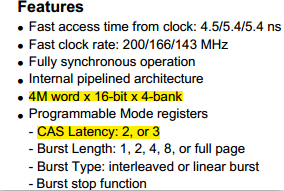

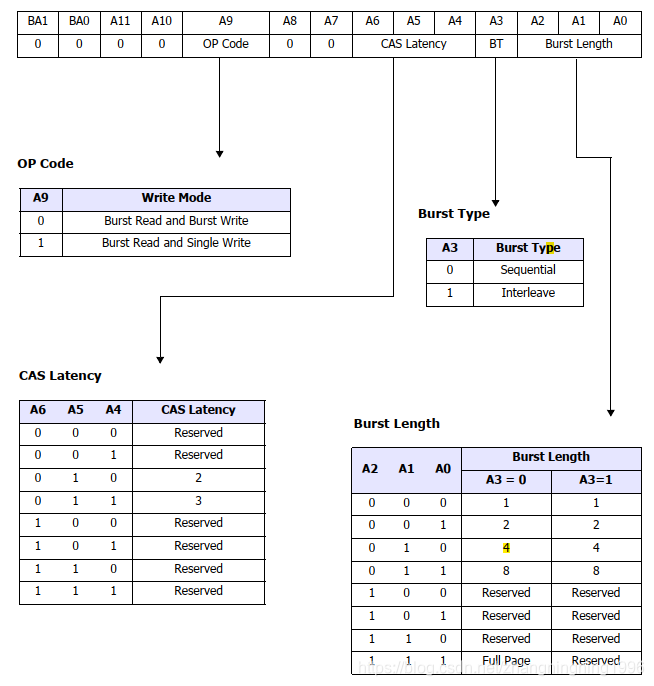

从SDRAM初始化的时序图中很容易想到利用线性序列机来写,也是很基础的逻辑代码。这里特别注意,在初始化的时候有一个状态是加载模式寄存器,模式寄存器的编码有特定的含义,这里我们从技术手册中找到,如下:

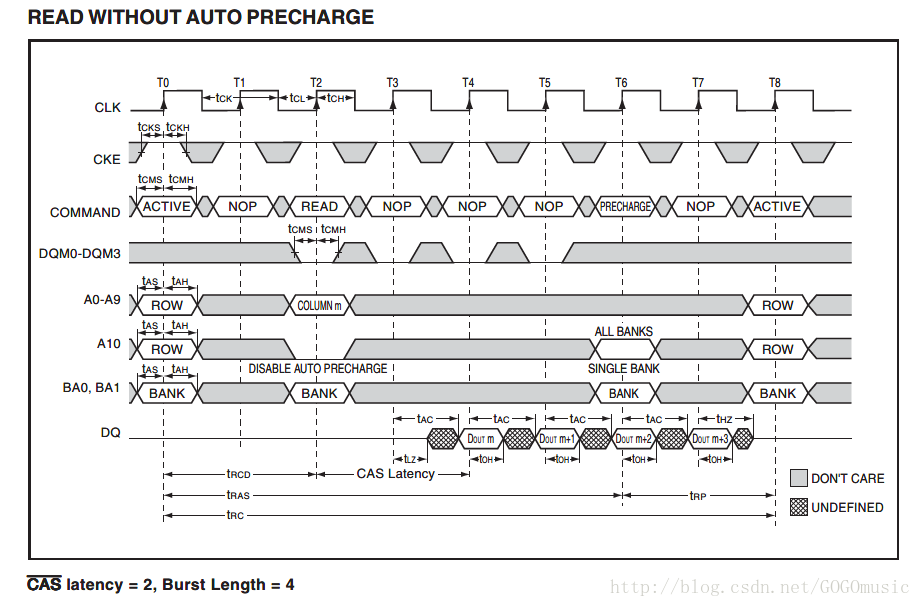

我们一般选择的模式是4突发,读数据3个时钟延时,Sequential模式,突发读写模式,具体的编码可以去程序中查找。

SDRAM上电时序代码

top模块的代码:

`timescale 1ns / 1ps

// *********************************************************************************

// Project Name : OSXXXX

// Author : zhangningning

// Email : nnzhang1996@foxmail.com

// Website :

// Module Name : sdram_top.v

// Create Time : 2020-02-09 17:22:24

// Editor : sublime text3, tab size (4)

// CopyRight(c) : All Rights Reserved

//

// *********************************************************************************

// Modification History:

// Date By Version Change Description

// -----------------------------------------------------------------------

// XXXX zhangningning 1.0 Original

//

// *********************************************************************************module sdram_top(//System Interfacesinput sclk ,input rst_n ,//SDRAM Interfacesoutput wire sdram_clk ,output wire sdram_cke ,output wire sdram_cs_n ,output wire sdram_cas_n ,output wire sdram_ras_n ,output wire sdram_we_n ,output wire [ 1:0] sdram_bank ,output wire [11:0] sdram_addr ,output wire [ 1:0] sdram_dqm ,inout [15:0] sdram_dq

);//========================================================================================\

//**************Define Parameter and Internal Signals**********************************

//========================================================================================/

//sdram_init

wire [ 3:0] init_cmd ;

wire [11:0] init_addr ;

wire init_done ;//========================================================================================\

//************** Main Code **********************************

//========================================================================================/

assign sdram_dqm = 2'b00;

assign sdram_clk = ~sclk;

assign {sdram_cs_n, sdram_ras_n, sdram_cas_n, sdram_we_n} = init_cmd;

assign sdram_addr = init_addr;

assign sdram_cke = 1'b1;

assign sdram_bank = 2'b00;sdram_init sdram_init_inst(//System Interfaces.sclk (sclk ),.rst_n (rst_n ),//SDRAM Interfaces.sdram_cmd (init_cmd ),.sdram_addr (init_addr ),//Others.init_done (init_done )

);endmoduleSDRAM上电初始化的代码:

`timescale 1ns / 1ps

// *********************************************************************************

// Project Name : OSXXXX

// Author : zhangningning

// Email : nnzhang1996@foxmail.com

// Website :

// Module Name : sdram_init.v

// Create Time : 2020-02-09 16:20:31

// Editor : sublime text3, tab size (4)

// CopyRight(c) : All Rights Reserved

//

// *********************************************************************************

// Modification History:

// Date By Version Change Description

// -----------------------------------------------------------------------

// XXXX zhangningning 1.0 Original

//

// *********************************************************************************module sdram_init(//System Interfacesinput sclk ,input rst_n ,//SDRAM Interfacesoutput reg [ 3:0] sdram_cmd ,output reg [11:0] sdram_addr ,//Othersoutput reg init_done

);//========================================================================================\

//**************Define Parameter and Internal Signals**********************************

//========================================================================================/

localparam DELAY_200US = 20000 ;

//SDRAM Command

localparam NOP = 4'b0111 ;

localparam PRE = 4'b0010 ;

localparam AREF = 4'b0001 ;

localparam MSET = 4'b0000 ;reg [14:0] cnt_200us ;

reg flag_200us ;

reg [ 4:0] cnt_cmd ;//========================================================================================\

//************** Main Code **********************************

//========================================================================================/

always @(posedge sclk or negedge rst_n)if(rst_n == 1'b0)cnt_200us <= 11'd0;else if(flag_200us == 1'b0)cnt_200us <= cnt_200us + 1'b1;elsecnt_200us <= cnt_200us;always @(posedge sclk or negedge rst_n)if(rst_n == 1'b0)flag_200us <= 1'b0;else if(cnt_200us >= DELAY_200US) flag_200us <= 1'b1;elseflag_200us <= flag_200us;always @(posedge sclk or negedge rst_n)if(rst_n == 1'b0)cnt_cmd <= 5'd0;else if(flag_200us == 1'b1 && cnt_cmd <= 5'd19)cnt_cmd <= cnt_cmd + 1'b1;else cnt_cmd <= cnt_cmd;always @(posedge sclk or negedge rst_n)if(rst_n == 1'b0)sdram_cmd <= NOP;else case(cnt_cmd)1 : sdram_cmd <= PRE;3 : sdram_cmd <= AREF;11 : sdram_cmd <= AREF;19 : sdram_cmd <= MSET;default : sdram_cmd <= NOP;endcasealways @(posedge sclk or negedge rst_n)if(rst_n == 1'b0)sdram_addr <= 12'b0100_0000_0000;else if(cnt_cmd == 5'd19) sdram_addr <= 12'b0000_0011_0010;elsesdram_addr <= 12'b0100_0000_0000;always @(posedge sclk or negedge rst_n)if(rst_n == 1'b0)init_done <= 1'b0; else if(cnt_cmd > 5'd19) init_done <= 1'b1;elseinit_done <= init_done;endmodule从上面的代码中不难发现,其实SDRAM的上电初始化代码就是一个线性序列机。

SDRAM测试模块的代码

SDRAM的测试要有仿真模型文件,但是我感觉这个仿真模型的文件在读操作、4突发操作的情况下第4个数据持续时间短,但是现在没把板子带回家没办法验证,但是很容易规避这个问题,就是读出的数据使用SDRAM的时钟来锁存,这个问题等我们到SDRAM读操作的时候具体描述。仿真的顶层测试文件如下:

`timescale 1ns / 1ps

`define CLOCK 10

// *********************************************************************************

// Project Name : OSXXXX

// Author : zhangningning

// Email : nnzhang1996@foxmail.com

// Website :

// Module Name : sdram_init_tb.v

// Create Time : 2020-02-09 17:10:08

// Editor : sublime text3, tab size (4)

// CopyRight(c) : All Rights Reserved

//

// *********************************************************************************

// Modification History:

// Date By Version Change Description

// -----------------------------------------------------------------------

// XXXX zhangningning 1.0 Original

//

// *********************************************************************************module sdram_init_tb;

reg sclk ;

reg rst_n ;

wire sdram_clk ;

wire sdram_cke ;

wire sdram_cs_n ;

wire sdram_cas_n ;

wire sdram_ras_n ;

wire sdram_we_n ;

wire [ 1:0] sdram_bank ;

wire [11:0] sdram_addr ;

wire [ 1:0] sdram_dqm ;

wire [15:0] sdram_dq ;initial beginsclk = 1'b0;rst_n <= 1'b0;#(100*`CLOCK);rst_n <= 1'b1;

end

always #(`CLOCK/2) sclk = ~sclk; sdram_top sdram_top_inst(//System Interfaces.sclk (sclk ),.rst_n (rst_n ),//SDRAM Interfaces.sdram_clk (sdram_clk ),.sdram_cke (sdram_cke ),.sdram_cs_n (sdram_cs_n ),.sdram_cas_n (sdram_cas_n ),.sdram_ras_n (sdram_ras_n ),.sdram_we_n (sdram_we_n ),.sdram_bank (sdram_bank ),.sdram_addr (sdram_addr ),.sdram_dqm (sdram_dqm ),.sdram_dq (sdram_dq )

);defparam sdram_model_plus_inst.addr_bits = 12;

defparam sdram_model_plus_inst.data_bits = 16;

defparam sdram_model_plus_inst.col_bits = 9;

defparam sdram_model_plus_inst.mem_sizes = 2*1024*1024; // 2Msdram_model_plus sdram_model_plus_inst(.Dq (sdram_dq ), .Addr (sdram_addr ), .Ba (sdram_bank ), .Clk (sdram_clk ), .Cke (sdram_cke ), .Cs_n (sdram_cs_n ), .Ras_n (sdram_ras_n ), .Cas_n (sdram_cas_n ), .We_n (sdram_we_n ), .Dqm (sdram_dqm ),.Debug (1'b1 )

);endmoduleSDRAM的仿真模型文件如下:

/***************************************************************************************

作者: 李晟

2003-08-27 V0.1 李晟 添加内存模块倒空功能,在外部需要创建事件:sdram_r ,本SDRAM的内容将会按Bank 顺序damp out 至文件sdram_data.txt 中

×××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××*/

//2004-03-04 陈乃奎 修改原程序中将BANK的数据转存入TXT文件的格式

//2004-03-16 陈乃奎 修改SDRAM 的初始化数据

//2004/04/06 陈乃奎 将SDRAM的操作命令以字符形式表示,以便用MODELSIM监视

//2004/04/19 陈乃奎 修改参数 parameter tAC = 8;

//2010/09/17 罗瑶 修改sdram的大小,数据位宽,dqm宽度;

/****************************************************************************************

*

* File Name: sdram_model.V

* Version: 0.0f

* Date: July 8th, 1999

* Model: BUS Functional

* Simulator: Model Technology (PC version 5.2e PE)

*

* Dependencies: None

*

* Author: Son P. Huynh

* Email: sphuynh@micron.com

* Phone: (208) 368-3825

* Company: Micron Technology, Inc.

* Model: sdram_model (1Meg x 16 x 4 Banks)

*

* Description: 64Mb SDRAM Verilog model

*

* Limitation: - Doesn't check for 4096 cycle refresh

*

* Note: - Set simulator resolution to "ps" accuracy

* - Set Debug = 0 to disable $display messages

*

* Disclaimer: THESE DESIGNS ARE PROVIDED "AS IS" WITH NO WARRANTY

* WHATSOEVER AND MICRON SPECIFICALLY DISCLAIMS ANY

* IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR

* A PARTICULAR PURPOSE, OR AGAINST INFRINGEMENT.

*

* Copyright ?1998 Micron Semiconductor Products, Inc.

* All rights researved

*

* Rev Author Phone Date Changes

* ---- ---------------------------- ---------- ---------------------------------------

* 0.0f Son Huynh 208-368-3825 07/08/1999 - Fix tWR = 1 Clk + 7.5 ns (Auto)

* Micron Technology Inc. - Fix tWR = 15 ns (Manual)

* - Fix tRP (Autoprecharge to AutoRefresh)

*

* 0.0a Son Huynh 208-368-3825 05/13/1998 - First Release (from 64Mb rev 0.0e)

* Micron Technology Inc.

****************************************************************************************/`timescale 1ns / 100psmodule sdram_model_plus (Dq, Addr, Ba, Clk, Cke, Cs_n, Ras_n, Cas_n, We_n, Dqm,Debug);parameter addr_bits = 11;parameter data_bits = 32;parameter col_bits = 8;parameter mem_sizes = 1048576*2-1;//1 Meg inout [data_bits - 1 : 0] Dq;input [addr_bits - 1 : 0] Addr;input [1 : 0] Ba;input Clk;input Cke;input Cs_n;input Ras_n;input Cas_n;input We_n;input [3 : 0] Dqm; //高低各8bit//added by xzliinput Debug;reg [data_bits - 1 : 0] Bank0 [0 : mem_sizes];//存储器类型数据reg [data_bits - 1 : 0] Bank1 [0 : mem_sizes];reg [data_bits - 1 : 0] Bank2 [0 : mem_sizes];reg [data_bits - 1 : 0] Bank3 [0 : mem_sizes];reg [1 : 0] Bank_addr [0 : 3]; // Bank Address Pipelinereg [col_bits - 1 : 0] Col_addr [0 : 3]; // Column Address Pipelinereg [3 : 0] Command [0 : 3]; // Command Operation Pipelinereg [3 : 0] Dqm_reg0, Dqm_reg1; // DQM Operation Pipelinereg [addr_bits - 1 : 0] B0_row_addr, B1_row_addr, B2_row_addr, B3_row_addr;reg [addr_bits - 1 : 0] Mode_reg;reg [data_bits - 1 : 0] Dq_reg, Dq_dqm;reg [col_bits - 1 : 0] Col_temp, Burst_counter;reg Act_b0, Act_b1, Act_b2, Act_b3; // Bank Activatereg Pc_b0, Pc_b1, Pc_b2, Pc_b3; // Bank Prechargereg [1 : 0] Bank_precharge [0 : 3]; // Precharge Commandreg A10_precharge [0 : 3]; // Addr[10] = 1 (All banks)reg Auto_precharge [0 : 3]; // RW AutoPrecharge (Bank)reg Read_precharge [0 : 3]; // R AutoPrechargereg Write_precharge [0 : 3]; // W AutoPrechargeinteger Count_precharge [0 : 3]; // RW AutoPrecharge (Counter)reg RW_interrupt_read [0 : 3]; // RW Interrupt Read with Auto Prechargereg RW_interrupt_write [0 : 3]; // RW Interrupt Write with Auto Prechargereg Data_in_enable;reg Data_out_enable;reg [1 : 0] Bank, Previous_bank;reg [addr_bits - 1 : 0] Row;reg [col_bits - 1 : 0] Col, Col_brst;// Internal system clockreg CkeZ, Sys_clk;reg [21:0] dd;// Commands Decodewire Active_enable = ~Cs_n & ~Ras_n & Cas_n & We_n;wire Aref_enable = ~Cs_n & ~Ras_n & ~Cas_n & We_n;wire Burst_term = ~Cs_n & Ras_n & Cas_n & ~We_n;wire Mode_reg_enable = ~Cs_n & ~Ras_n & ~Cas_n & ~We_n;wire Prech_enable = ~Cs_n & ~Ras_n & Cas_n & ~We_n;wire Read_enable = ~Cs_n & Ras_n & ~Cas_n & We_n;wire Write_enable = ~Cs_n & Ras_n & ~Cas_n & ~We_n;// Burst Length Decodewire Burst_length_1 = ~Mode_reg[2] & ~Mode_reg[1] & ~Mode_reg[0];wire Burst_length_2 = ~Mode_reg[2] & ~Mode_reg[1] & Mode_reg[0];wire Burst_length_4 = ~Mode_reg[2] & Mode_reg[1] & ~Mode_reg[0];wire Burst_length_8 = ~Mode_reg[2] & Mode_reg[1] & Mode_reg[0];// CAS Latency Decodewire Cas_latency_2 = ~Mode_reg[6] & Mode_reg[5] & ~Mode_reg[4];wire Cas_latency_3 = ~Mode_reg[6] & Mode_reg[5] & Mode_reg[4];// Write Burst Modewire Write_burst_mode = Mode_reg[9];wire Debug; // Debug messages : 1 = On; 0 = Offwire Dq_chk = Sys_clk & Data_in_enable; // Check setup/hold time for DQreg [31:0] mem_d;event sdram_r,sdram_w,compare;assign Dq = Dq_reg; // DQ buffer// Commands Operation`define ACT 0`define NOP 1`define READ 2`define READ_A 3`define WRITE 4`define WRITE_A 5`define PRECH 6`define A_REF 7`define BST 8`define LMR 9// // Timing Parameters for -75 (PC133) and CAS Latency = 2

// parameter tAC = 8; //test 6.5

// parameter tHZ = 7.0;

// parameter tOH = 2.7;

// parameter tMRD = 2.0; // 2 Clk Cycles

// parameter tRAS = 44.0;

// parameter tRC = 66.0;

// parameter tRCD = 20.0;

// parameter tRP = 20.0;

// parameter tRRD = 15.0;

// parameter tWRa = 7.5; // A2 Version - Auto precharge mode only (1 Clk + 7.5 ns)

// parameter tWRp = 0.0; // A2 Version - Precharge mode only (15 ns)// Timing Parameters for -7 (PC143) and CAS Latency = 3parameter tAC = 6.5; //test 6.5parameter tHZ = 5.5;parameter tOH = 2;parameter tMRD = 2.0; // 2 Clk Cyclesparameter tRAS = 48.0;parameter tRC = 70.0;parameter tRCD = 20.0;parameter tRP = 20.0;parameter tRRD = 14.0;parameter tWRa = 7.5; // A2 Version - Auto precharge mode only (1 Clk + 7.5 ns)parameter tWRp = 0.0; // A2 Version - Precharge mode only (15 ns)// Timing Check variableinteger MRD_chk;integer WR_counter [0 : 3];time WR_chk [0 : 3];time RC_chk, RRD_chk;time RAS_chk0, RAS_chk1, RAS_chk2, RAS_chk3;time RCD_chk0, RCD_chk1, RCD_chk2, RCD_chk3;time RP_chk0, RP_chk1, RP_chk2, RP_chk3;integer test_file;//*****display the command of the sdram**************************************parameter Mode_Reg_Set =4'b0000;parameter Auto_Refresh =4'b0001;parameter Row_Active =4'b0011;parameter Pre_Charge =4'b0010;parameter PreCharge_All =4'b0010;parameter Write =4'b0100;parameter Write_Pre =4'b0100;parameter Read =4'b0101;parameter Read_Pre =4'b0101;parameter Burst_Stop =4'b0110;parameter Nop =4'b0111;parameter Dsel =4'b1111;wire [3:0] sdram_control;reg cke_temp;reg [8*13:1] sdram_command;always@(posedge Clk)cke_temp<=Cke;assign sdram_control={Cs_n,Ras_n,Cas_n,We_n};always@(sdram_control or cke_temp)begincase(sdram_control)Mode_Reg_Set: sdram_command<="Mode_Reg_Set";Auto_Refresh: sdram_command<="Auto_Refresh";Row_Active: sdram_command<="Row_Active";Pre_Charge: sdram_command<="Pre_Charge";Burst_Stop: sdram_command<="Burst_Stop";Dsel: sdram_command<="Dsel";Write: if(cke_temp==1)sdram_command<="Write";elsesdram_command<="Write_suspend";Read: if(cke_temp==1)sdram_command<="Read";elsesdram_command<="Read_suspend";Nop: if(cke_temp==1)sdram_command<="Nop";elsesdram_command<="Self_refresh";default: sdram_command<="Power_down";endcaseend//*****************************************************initial begin//test_file=$fopen("test_file.txt");endinitial beginDq_reg = {data_bits{1'bz}};{Data_in_enable, Data_out_enable} = 0;{Act_b0, Act_b1, Act_b2, Act_b3} = 4'b0000;{Pc_b0, Pc_b1, Pc_b2, Pc_b3} = 4'b0000;{WR_chk[0], WR_chk[1], WR_chk[2], WR_chk[3]} = 0;{WR_counter[0], WR_counter[1], WR_counter[2], WR_counter[3]} = 0;{RW_interrupt_read[0], RW_interrupt_read[1], RW_interrupt_read[2], RW_interrupt_read[3]} = 0;{RW_interrupt_write[0], RW_interrupt_write[1], RW_interrupt_write[2], RW_interrupt_write[3]} = 0;{MRD_chk, RC_chk, RRD_chk} = 0;{RAS_chk0, RAS_chk1, RAS_chk2, RAS_chk3} = 0;{RCD_chk0, RCD_chk1, RCD_chk2, RCD_chk3} = 0;{RP_chk0, RP_chk1, RP_chk2, RP_chk3} = 0;$timeformat (-9, 0, " ns", 12);//$readmemh("bank0.txt", Bank0);//$readmemh("bank1.txt", Bank1);//$readmemh("bank2.txt", Bank2);//$readmemh("bank3.txt", Bank3);

/* for(dd=0;dd<=mem_sizes;dd=dd+1)beginBank0[dd]=dd[data_bits - 1 : 0];Bank1[dd]=dd[data_bits - 1 : 0]+1;Bank2[dd]=dd[data_bits - 1 : 0]+2;Bank3[dd]=dd[data_bits - 1 : 0]+3;end

*/ initial_sdram(0);endtask initial_sdram; input data_sign;reg [3:0] data_sign;for(dd=0;dd<=mem_sizes;dd=dd+1)beginmem_d = {data_sign,data_sign,data_sign,data_sign,data_sign,data_sign,data_sign,data_sign};if(data_bits==16)beginBank0[dd]=mem_d[15:0];Bank1[dd]=mem_d[15:0];Bank2[dd]=mem_d[15:0];Bank3[dd]=mem_d[15:0];endelse if(data_bits==32)beginBank0[dd]=mem_d[31:0];Bank1[dd]=mem_d[31:0];Bank2[dd]=mem_d[31:0];Bank3[dd]=mem_d[31:0];endend endtask// System clock generatoralwaysbegin@(posedge Clk)beginSys_clk = CkeZ;CkeZ = Cke;end@(negedge Clk) beginSys_clk = 1'b0;endendalways @ (posedge Sys_clk) begin// Internal Commamd PipelinedCommand[0] = Command[1];Command[1] = Command[2];Command[2] = Command[3];Command[3] = `NOP;Col_addr[0] = Col_addr[1];Col_addr[1] = Col_addr[2];Col_addr[2] = Col_addr[3];Col_addr[3] = {col_bits{1'b0}};Bank_addr[0] = Bank_addr[1];Bank_addr[1] = Bank_addr[2];Bank_addr[2] = Bank_addr[3];Bank_addr[3] = 2'b0;Bank_precharge[0] = Bank_precharge[1];Bank_precharge[1] = Bank_precharge[2];Bank_precharge[2] = Bank_precharge[3];Bank_precharge[3] = 2'b0;A10_precharge[0] = A10_precharge[1];A10_precharge[1] = A10_precharge[2];A10_precharge[2] = A10_precharge[3];A10_precharge[3] = 1'b0;// Dqm pipeline for ReadDqm_reg0 = Dqm_reg1;Dqm_reg1 = Dqm;// Read or Write with Auto Precharge Counterif (Auto_precharge[0] == 1'b1) beginCount_precharge[0] = Count_precharge[0] + 1;endif (Auto_precharge[1] == 1'b1) beginCount_precharge[1] = Count_precharge[1] + 1;endif (Auto_precharge[2] == 1'b1) beginCount_precharge[2] = Count_precharge[2] + 1;endif (Auto_precharge[3] == 1'b1) beginCount_precharge[3] = Count_precharge[3] + 1;end// tMRD CounterMRD_chk = MRD_chk + 1;// tWR Counter for WriteWR_counter[0] = WR_counter[0] + 1;WR_counter[1] = WR_counter[1] + 1;WR_counter[2] = WR_counter[2] + 1;WR_counter[3] = WR_counter[3] + 1;// Auto Refreshif (Aref_enable == 1'b1) beginif (Debug) $display ("at time %t AREF : Auto Refresh", $time);// Auto Refresh to Auto Refreshif (($time - RC_chk < tRC)&&Debug) begin$display ("at time %t ERROR: tRC violation during Auto Refresh", $time);end// Precharge to Auto Refreshif (($time - RP_chk0 < tRP || $time - RP_chk1 < tRP || $time - RP_chk2 < tRP || $time - RP_chk3 < tRP)&&Debug) begin$display ("at time %t ERROR: tRP violation during Auto Refresh", $time);end// Precharge to Refreshif (Pc_b0 == 1'b0 || Pc_b1 == 1'b0 || Pc_b2 == 1'b0 || Pc_b3 == 1'b0) begin$display ("at time %t ERROR: All banks must be Precharge before Auto Refresh", $time);end// Record Current tRC timeRC_chk = $time;end// Load Mode Registerif (Mode_reg_enable == 1'b1) begin// Decode CAS Latency, Burst Length, Burst Type, and Write Burst Modeif (Pc_b0 == 1'b1 && Pc_b1 == 1'b1 && Pc_b2 == 1'b1 && Pc_b3 == 1'b1) beginMode_reg = Addr;if (Debug) begin$display ("at time %t LMR : Load Mode Register", $time);// CAS Latencyif (Addr[6 : 4] == 3'b010)$display (" CAS Latency = 2");else if (Addr[6 : 4] == 3'b011)$display (" CAS Latency = 3");else$display (" CAS Latency = Reserved");// Burst Lengthif (Addr[2 : 0] == 3'b000)$display (" Burst Length = 1");else if (Addr[2 : 0] == 3'b001)$display (" Burst Length = 2");else if (Addr[2 : 0] == 3'b010)$display (" Burst Length = 4");else if (Addr[2 : 0] == 3'b011)$display (" Burst Length = 8");else if (Addr[3 : 0] == 4'b0111)$display (" Burst Length = Full");else$display (" Burst Length = Reserved");// Burst Typeif (Addr[3] == 1'b0)$display (" Burst Type = Sequential");else if (Addr[3] == 1'b1)$display (" Burst Type = Interleaved");else$display (" Burst Type = Reserved");// Write Burst Modeif (Addr[9] == 1'b0)$display (" Write Burst Mode = Programmed Burst Length");else if (Addr[9] == 1'b1)$display (" Write Burst Mode = Single Location Access");else$display (" Write Burst Mode = Reserved");endend else begin$display ("at time %t ERROR: all banks must be Precharge before Load Mode Register", $time);end// REF to LMRif ($time - RC_chk < tRC) begin$display ("at time %t ERROR: tRC violation during Load Mode Register", $time);end// LMR to LMRif (MRD_chk < tMRD) begin$display ("at time %t ERROR: tMRD violation during Load Mode Register", $time);endMRD_chk = 0;end// Active Block (Latch Bank Address and Row Address)if (Active_enable == 1'b1) beginif (Ba == 2'b00 && Pc_b0 == 1'b1) begin{Act_b0, Pc_b0} = 2'b10;B0_row_addr = Addr [addr_bits - 1 : 0];RCD_chk0 = $time;RAS_chk0 = $time;if (Debug) $display ("at time %t ACT : Bank = 0 Row = %d", $time, Addr);// Precharge to Activate Bank 0if ($time - RP_chk0 < tRP) begin$display ("at time %t ERROR: tRP violation during Activate bank 0", $time);endend else if (Ba == 2'b01 && Pc_b1 == 1'b1) begin{Act_b1, Pc_b1} = 2'b10;B1_row_addr = Addr [addr_bits - 1 : 0];RCD_chk1 = $time;RAS_chk1 = $time;if (Debug) $display ("at time %t ACT : Bank = 1 Row = %d", $time, Addr);// Precharge to Activate Bank 1if ($time - RP_chk1 < tRP) begin$display ("at time %t ERROR: tRP violation during Activate bank 1", $time);endend else if (Ba == 2'b10 && Pc_b2 == 1'b1) begin{Act_b2, Pc_b2} = 2'b10;B2_row_addr = Addr [addr_bits - 1 : 0];RCD_chk2 = $time;RAS_chk2 = $time;if (Debug) $display ("at time %t ACT : Bank = 2 Row = %d", $time, Addr);// Precharge to Activate Bank 2if ($time - RP_chk2 < tRP) begin$display ("at time %t ERROR: tRP violation during Activate bank 2", $time);endend else if (Ba == 2'b11 && Pc_b3 == 1'b1) begin{Act_b3, Pc_b3} = 2'b10;B3_row_addr = Addr [addr_bits - 1 : 0];RCD_chk3 = $time;RAS_chk3 = $time;if (Debug) $display ("at time %t ACT : Bank = 3 Row = %d", $time, Addr);// Precharge to Activate Bank 3if ($time - RP_chk3 < tRP) begin$display ("at time %t ERROR: tRP violation during Activate bank 3", $time);endend else if (Ba == 2'b00 && Pc_b0 == 1'b0) begin$display ("at time %t ERROR: Bank 0 is not Precharged.", $time);end else if (Ba == 2'b01 && Pc_b1 == 1'b0) begin$display ("at time %t ERROR: Bank 1 is not Precharged.", $time);end else if (Ba == 2'b10 && Pc_b2 == 1'b0) begin$display ("at time %t ERROR: Bank 2 is not Precharged.", $time);end else if (Ba == 2'b11 && Pc_b3 == 1'b0) begin$display ("at time %t ERROR: Bank 3 is not Precharged.", $time);end// Active Bank A to Active Bank Bif ((Previous_bank != Ba) && ($time - RRD_chk < tRRD)) begin$display ("at time %t ERROR: tRRD violation during Activate bank = %d", $time, Ba);end// Load Mode Register to Activeif (MRD_chk < tMRD ) begin$display ("at time %t ERROR: tMRD violation during Activate bank = %d", $time, Ba);end// Auto Refresh to Activateif (($time - RC_chk < tRC)&&Debug) begin$display ("at time %t ERROR: tRC violation during Activate bank = %d", $time, Ba);end// Record variables for checking violationRRD_chk = $time;Previous_bank = Ba;end// Precharge Blockif (Prech_enable == 1'b1) beginif (Addr[10] == 1'b1) begin{Pc_b0, Pc_b1, Pc_b2, Pc_b3} = 4'b1111;{Act_b0, Act_b1, Act_b2, Act_b3} = 4'b0000;RP_chk0 = $time;RP_chk1 = $time;RP_chk2 = $time;RP_chk3 = $time;if (Debug) $display ("at time %t PRE : Bank = ALL",$time);// Activate to Precharge all banksif (($time - RAS_chk0 < tRAS) || ($time - RAS_chk1 < tRAS) ||($time - RAS_chk2 < tRAS) || ($time - RAS_chk3 < tRAS)) begin$display ("at time %t ERROR: tRAS violation during Precharge all bank", $time);end// tWR violation check for writeif (($time - WR_chk[0] < tWRp) || ($time - WR_chk[1] < tWRp) ||($time - WR_chk[2] < tWRp) || ($time - WR_chk[3] < tWRp)) begin$display ("at time %t ERROR: tWR violation during Precharge all bank", $time);endend else if (Addr[10] == 1'b0) beginif (Ba == 2'b00) begin{Pc_b0, Act_b0} = 2'b10;RP_chk0 = $time;if (Debug) $display ("at time %t PRE : Bank = 0",$time);// Activate to Precharge Bank 0if ($time - RAS_chk0 < tRAS) begin$display ("at time %t ERROR: tRAS violation during Precharge bank 0", $time);endend else if (Ba == 2'b01) begin{Pc_b1, Act_b1} = 2'b10;RP_chk1 = $time;if (Debug) $display ("at time %t PRE : Bank = 1",$time);// Activate to Precharge Bank 1if ($time - RAS_chk1 < tRAS) begin$display ("at time %t ERROR: tRAS violation during Precharge bank 1", $time);endend else if (Ba == 2'b10) begin{Pc_b2, Act_b2} = 2'b10;RP_chk2 = $time;if (Debug) $display ("at time %t PRE : Bank = 2",$time);// Activate to Precharge Bank 2if ($time - RAS_chk2 < tRAS) begin$display ("at time %t ERROR: tRAS violation during Precharge bank 2", $time);endend else if (Ba == 2'b11) begin{Pc_b3, Act_b3} = 2'b10;RP_chk3 = $time;if (Debug) $display ("at time %t PRE : Bank = 3",$time);// Activate to Precharge Bank 3if ($time - RAS_chk3 < tRAS) begin$display ("at time %t ERROR: tRAS violation during Precharge bank 3", $time);endend// tWR violation check for writeif ($time - WR_chk[Ba] < tWRp) begin$display ("at time %t ERROR: tWR violation during Precharge bank %d", $time, Ba);endend// Terminate a Write Immediately (if same bank or all banks)if (Data_in_enable == 1'b1 && (Bank == Ba || Addr[10] == 1'b1)) beginData_in_enable = 1'b0;end// Precharge Command Pipeline for Readif (Cas_latency_3 == 1'b1) beginCommand[2] = `PRECH;Bank_precharge[2] = Ba;A10_precharge[2] = Addr[10];end else if (Cas_latency_2 == 1'b1) beginCommand[1] = `PRECH;Bank_precharge[1] = Ba;A10_precharge[1] = Addr[10];endend// Burst terminateif (Burst_term == 1'b1) begin// Terminate a Write Immediatelyif (Data_in_enable == 1'b1) beginData_in_enable = 1'b0;end// Terminate a Read Depend on CAS Latencyif (Cas_latency_3 == 1'b1) beginCommand[2] = `BST;end else if (Cas_latency_2 == 1'b1) beginCommand[1] = `BST;endif (Debug) $display ("at time %t BST : Burst Terminate",$time);end// Read, Write, Column Latchif (Read_enable == 1'b1 || Write_enable == 1'b1) begin// Check to see if bank is open (ACT)if ((Ba == 2'b00 && Pc_b0 == 1'b1) || (Ba == 2'b01 && Pc_b1 == 1'b1) ||(Ba == 2'b10 && Pc_b2 == 1'b1) || (Ba == 2'b11 && Pc_b3 == 1'b1)) begin$display("at time %t ERROR: Cannot Read or Write - Bank %d is not Activated", $time, Ba);end// Activate to Read or Writeif ((Ba == 2'b00) && ($time - RCD_chk0 < tRCD))$display("at time %t ERROR: tRCD violation during Read or Write to Bank 0", $time);if ((Ba == 2'b01) && ($time - RCD_chk1 < tRCD))$display("at time %t ERROR: tRCD violation during Read or Write to Bank 1", $time);if ((Ba == 2'b10) && ($time - RCD_chk2 < tRCD))$display("at time %t ERROR: tRCD violation during Read or Write to Bank 2", $time);if ((Ba == 2'b11) && ($time - RCD_chk3 < tRCD))$display("at time %t ERROR: tRCD violation during Read or Write to Bank 3", $time);// Read Commandif (Read_enable == 1'b1) begin// CAS Latency pipelineif (Cas_latency_3 == 1'b1) beginif (Addr[10] == 1'b1) beginCommand[2] = `READ_A;end else beginCommand[2] = `READ;endCol_addr[2] = Addr;Bank_addr[2] = Ba;end else if (Cas_latency_2 == 1'b1) beginif (Addr[10] == 1'b1) beginCommand[1] = `READ_A;end else beginCommand[1] = `READ;endCol_addr[1] = Addr;Bank_addr[1] = Ba;end// Read interrupt Write (terminate Write immediately)if (Data_in_enable == 1'b1) beginData_in_enable = 1'b0;end// Write Commandend else if (Write_enable == 1'b1) beginif (Addr[10] == 1'b1) beginCommand[0] = `WRITE_A;end else beginCommand[0] = `WRITE;endCol_addr[0] = Addr;Bank_addr[0] = Ba;// Write interrupt Write (terminate Write immediately)if (Data_in_enable == 1'b1) beginData_in_enable = 1'b0;end// Write interrupt Read (terminate Read immediately)if (Data_out_enable == 1'b1) beginData_out_enable = 1'b0;endend// Interrupting a Write with Autoprechargeif (Auto_precharge[Bank] == 1'b1 && Write_precharge[Bank] == 1'b1) beginRW_interrupt_write[Bank] = 1'b1;if (Debug) $display ("at time %t NOTE : Read/Write Bank %d interrupt Write Bank %d with Autoprecharge", $time, Ba, Bank);end// Interrupting a Read with Autoprechargeif (Auto_precharge[Bank] == 1'b1 && Read_precharge[Bank] == 1'b1) beginRW_interrupt_read[Bank] = 1'b1;if (Debug) $display ("at time %t NOTE : Read/Write Bank %d interrupt Read Bank %d with Autoprecharge", $time, Ba, Bank);end// Read or Write with Auto Prechargeif (Addr[10] == 1'b1) beginAuto_precharge[Ba] = 1'b1;Count_precharge[Ba] = 0;if (Read_enable == 1'b1) beginRead_precharge[Ba] = 1'b1;end else if (Write_enable == 1'b1) beginWrite_precharge[Ba] = 1'b1;endendend// Read with Auto Precharge Calculation// The device start internal precharge:// 1. CAS Latency - 1 cycles before last burst// and 2. Meet minimum tRAS requirement// or 3. Interrupt by a Read or Write (with or without AutoPrecharge)if ((Auto_precharge[0] == 1'b1) && (Read_precharge[0] == 1'b1)) beginif ((($time - RAS_chk0 >= tRAS) && // Case 2((Burst_length_1 == 1'b1 && Count_precharge[0] >= 1) || // Case 1(Burst_length_2 == 1'b1 && Count_precharge[0] >= 2) ||(Burst_length_4 == 1'b1 && Count_precharge[0] >= 4) ||(Burst_length_8 == 1'b1 && Count_precharge[0] >= 8))) ||(RW_interrupt_read[0] == 1'b1)) begin // Case 3Pc_b0 = 1'b1;Act_b0 = 1'b0;RP_chk0 = $time;Auto_precharge[0] = 1'b0;Read_precharge[0] = 1'b0;RW_interrupt_read[0] = 1'b0;if (Debug) $display ("at time %t NOTE : Start Internal Auto Precharge for Bank 0", $time);endendif ((Auto_precharge[1] == 1'b1) && (Read_precharge[1] == 1'b1)) beginif ((($time - RAS_chk1 >= tRAS) &&((Burst_length_1 == 1'b1 && Count_precharge[1] >= 1) || (Burst_length_2 == 1'b1 && Count_precharge[1] >= 2) ||(Burst_length_4 == 1'b1 && Count_precharge[1] >= 4) ||(Burst_length_8 == 1'b1 && Count_precharge[1] >= 8))) ||(RW_interrupt_read[1] == 1'b1)) beginPc_b1 = 1'b1;Act_b1 = 1'b0;RP_chk1 = $time;Auto_precharge[1] = 1'b0;Read_precharge[1] = 1'b0;RW_interrupt_read[1] = 1'b0;if (Debug) $display ("at time %t NOTE : Start Internal Auto Precharge for Bank 1", $time);endendif ((Auto_precharge[2] == 1'b1) && (Read_precharge[2] == 1'b1)) beginif ((($time - RAS_chk2 >= tRAS) &&((Burst_length_1 == 1'b1 && Count_precharge[2] >= 1) || (Burst_length_2 == 1'b1 && Count_precharge[2] >= 2) ||(Burst_length_4 == 1'b1 && Count_precharge[2] >= 4) ||(Burst_length_8 == 1'b1 && Count_precharge[2] >= 8))) ||(RW_interrupt_read[2] == 1'b1)) beginPc_b2 = 1'b1;Act_b2 = 1'b0;RP_chk2 = $time;Auto_precharge[2] = 1'b0;Read_precharge[2] = 1'b0;RW_interrupt_read[2] = 1'b0;if (Debug) $display ("at time %t NOTE : Start Internal Auto Precharge for Bank 2", $time);endendif ((Auto_precharge[3] == 1'b1) && (Read_precharge[3] == 1'b1)) beginif ((($time - RAS_chk3 >= tRAS) &&((Burst_length_1 == 1'b1 && Count_precharge[3] >= 1) || (Burst_length_2 == 1'b1 && Count_precharge[3] >= 2) ||(Burst_length_4 == 1'b1 && Count_precharge[3] >= 4) ||(Burst_length_8 == 1'b1 && Count_precharge[3] >= 8))) ||(RW_interrupt_read[3] == 1'b1)) beginPc_b3 = 1'b1;Act_b3 = 1'b0;RP_chk3 = $time;Auto_precharge[3] = 1'b0;Read_precharge[3] = 1'b0;RW_interrupt_read[3] = 1'b0;if (Debug) $display ("at time %t NOTE : Start Internal Auto Precharge for Bank 3", $time);endend// Internal Precharge or Bstif (Command[0] == `PRECH) begin // Precharge terminate a read with same bank or all banksif (Bank_precharge[0] == Bank || A10_precharge[0] == 1'b1) beginif (Data_out_enable == 1'b1) beginData_out_enable = 1'b0;endendend else if (Command[0] == `BST) begin // BST terminate a read to current bankif (Data_out_enable == 1'b1) beginData_out_enable = 1'b0;endendif (Data_out_enable == 1'b0) beginDq_reg <= #tOH {data_bits{1'bz}};end// Detect Read or Write commandif (Command[0] == `READ || Command[0] == `READ_A) beginBank = Bank_addr[0];Col = Col_addr[0];Col_brst = Col_addr[0];if (Bank_addr[0] == 2'b00) beginRow = B0_row_addr;end else if (Bank_addr[0] == 2'b01) beginRow = B1_row_addr;end else if (Bank_addr[0] == 2'b10) beginRow = B2_row_addr;end else if (Bank_addr[0] == 2'b11) beginRow = B3_row_addr;endBurst_counter = 0;Data_in_enable = 1'b0;Data_out_enable = 1'b1;end else if (Command[0] == `WRITE || Command[0] == `WRITE_A) beginBank = Bank_addr[0];Col = Col_addr[0];Col_brst = Col_addr[0];if (Bank_addr[0] == 2'b00) beginRow = B0_row_addr;end else if (Bank_addr[0] == 2'b01) beginRow = B1_row_addr;end else if (Bank_addr[0] == 2'b10) beginRow = B2_row_addr;end else if (Bank_addr[0] == 2'b11) beginRow = B3_row_addr;endBurst_counter = 0;Data_in_enable = 1'b1;Data_out_enable = 1'b0;end// DQ buffer (Driver/Receiver)if (Data_in_enable == 1'b1) begin // Writing Data to Memory// Array bufferif (Bank == 2'b00) Dq_dqm [data_bits - 1 : 0] = Bank0 [{Row, Col}];if (Bank == 2'b01) Dq_dqm [data_bits - 1 : 0] = Bank1 [{Row, Col}];if (Bank == 2'b10) Dq_dqm [data_bits - 1 : 0] = Bank2 [{Row, Col}];if (Bank == 2'b11) Dq_dqm [data_bits - 1 : 0] = Bank3 [{Row, Col}];// Dqm operationif (Dqm[0] == 1'b0) Dq_dqm [ 7 : 0] = Dq [ 7 : 0];if (Dqm[1] == 1'b0) Dq_dqm [15 : 8] = Dq [15 : 8];//if (Dqm[2] == 1'b0) Dq_dqm [23 : 16] = Dq [23 : 16];// if (Dqm[3] == 1'b0) Dq_dqm [31 : 24] = Dq [31 : 24];// Write to memoryif (Bank == 2'b00) Bank0 [{Row, Col}] = Dq_dqm [data_bits - 1 : 0];if (Bank == 2'b01) Bank1 [{Row, Col}] = Dq_dqm [data_bits - 1 : 0];if (Bank == 2'b10) Bank2 [{Row, Col}] = Dq_dqm [data_bits - 1 : 0];if (Bank == 2'b11) Bank3 [{Row, Col}] = Dq_dqm [data_bits - 1 : 0];if (Bank == 2'b11 && Row==10'h3 && Col[7:4]==4'h4)$display("at time %t WRITE: Bank = %d Row = %d, Col = %d, Data = Hi-Z due to DQM", $time, Bank, Row, Col);//$fdisplay(test_file,"bank:%h row:%h col:%h write:%h",Bank,Row,Col,Dq_dqm);// Output resultif (Dqm == 4'b1111) beginif (Debug) $display("at time %t WRITE: Bank = %d Row = %d, Col = %d, Data = Hi-Z due to DQM", $time, Bank, Row, Col);end else beginif (Debug) $display("at time %t WRITE: Bank = %d Row = %d, Col = %d, Data = %d, Dqm = %b", $time, Bank, Row, Col, Dq_dqm, Dqm);// Record tWR time and reset counterWR_chk [Bank] = $time;WR_counter [Bank] = 0;end// Advance burst counter subroutine#tHZ Burst;end else if (Data_out_enable == 1'b1) begin // Reading Data from Memory//$display("%h , %h, %h",Bank0,Row,Col);// Array bufferif (Bank == 2'b00) Dq_dqm [data_bits - 1 : 0] = Bank0 [{Row, Col}];if (Bank == 2'b01) Dq_dqm [data_bits - 1 : 0] = Bank1 [{Row, Col}];if (Bank == 2'b10) Dq_dqm [data_bits - 1 : 0] = Bank2 [{Row, Col}];if (Bank == 2'b11) Dq_dqm [data_bits - 1 : 0] = Bank3 [{Row, Col}];// Dqm operationif (Dqm_reg0[0] == 1'b1) Dq_dqm [ 7 : 0] = 8'bz;if (Dqm_reg0[1] == 1'b1) Dq_dqm [15 : 8] = 8'bz;if (Dqm_reg0[2] == 1'b1) Dq_dqm [23 : 16] = 8'bz;if (Dqm_reg0[3] == 1'b1) Dq_dqm [31 : 24] = 8'bz;// Display resultDq_reg [data_bits - 1 : 0] = #tAC Dq_dqm [data_bits - 1 : 0];if (Dqm_reg0 == 4'b1111) beginif (Debug) $display("at time %t READ : Bank = %d Row = %d, Col = %d, Data = Hi-Z due to DQM", $time, Bank, Row, Col);end else beginif (Debug) $display("at time %t READ : Bank = %d Row = %d, Col = %d, Data = %d, Dqm = %b", $time, Bank, Row, Col, Dq_reg, Dqm_reg0);end// Advance burst counter subroutineBurst;endend// Write with Auto Precharge Calculation// The device start internal precharge:// 1. tWR Clock after last burst// and 2. Meet minimum tRAS requirement// or 3. Interrupt by a Read or Write (with or without AutoPrecharge)always @ (WR_counter[0]) beginif ((Auto_precharge[0] == 1'b1) && (Write_precharge[0] == 1'b1)) beginif ((($time - RAS_chk0 >= tRAS) && // Case 2(((Burst_length_1 == 1'b1 || Write_burst_mode == 1'b1) && Count_precharge [0] >= 1) || // Case 1(Burst_length_2 == 1'b1 && Count_precharge [0] >= 2) ||(Burst_length_4 == 1'b1 && Count_precharge [0] >= 4) ||(Burst_length_8 == 1'b1 && Count_precharge [0] >= 8))) ||(RW_interrupt_write[0] == 1'b1 && WR_counter[0] >= 2)) begin // Case 3 (stop count when interrupt)Auto_precharge[0] = 1'b0;Write_precharge[0] = 1'b0;RW_interrupt_write[0] = 1'b0;#tWRa; // Wait for tWRPc_b0 = 1'b1;Act_b0 = 1'b0;RP_chk0 = $time;if (Debug) $display ("at time %t NOTE : Start Internal Auto Precharge for Bank 0", $time);endendendalways @ (WR_counter[1]) beginif ((Auto_precharge[1] == 1'b1) && (Write_precharge[1] == 1'b1)) beginif ((($time - RAS_chk1 >= tRAS) &&(((Burst_length_1 == 1'b1 || Write_burst_mode == 1'b1) && Count_precharge [1] >= 1) || (Burst_length_2 == 1'b1 && Count_precharge [1] >= 2) ||(Burst_length_4 == 1'b1 && Count_precharge [1] >= 4) ||(Burst_length_8 == 1'b1 && Count_precharge [1] >= 8))) ||(RW_interrupt_write[1] == 1'b1 && WR_counter[1] >= 2)) beginAuto_precharge[1] = 1'b0;Write_precharge[1] = 1'b0;RW_interrupt_write[1] = 1'b0;#tWRa; // Wait for tWRPc_b1 = 1'b1;Act_b1 = 1'b0;RP_chk1 = $time;if (Debug) $display ("at time %t NOTE : Start Internal Auto Precharge for Bank 1", $time);endendendalways @ (WR_counter[2]) beginif ((Auto_precharge[2] == 1'b1) && (Write_precharge[2] == 1'b1)) beginif ((($time - RAS_chk2 >= tRAS) &&(((Burst_length_1 == 1'b1 || Write_burst_mode == 1'b1) && Count_precharge [2] >= 1) || (Burst_length_2 == 1'b1 && Count_precharge [2] >= 2) ||(Burst_length_4 == 1'b1 && Count_precharge [2] >= 4) ||(Burst_length_8 == 1'b1 && Count_precharge [2] >= 8))) ||(RW_interrupt_write[2] == 1'b1 && WR_counter[2] >= 2)) beginAuto_precharge[2] = 1'b0;Write_precharge[2] = 1'b0;RW_interrupt_write[2] = 1'b0;#tWRa; // Wait for tWRPc_b2 = 1'b1;Act_b2 = 1'b0;RP_chk2 = $time;if (Debug) $display ("at time %t NOTE : Start Internal Auto Precharge for Bank 2", $time);endendendalways @ (WR_counter[3]) beginif ((Auto_precharge[3] == 1'b1) && (Write_precharge[3] == 1'b1)) beginif ((($time - RAS_chk3 >= tRAS) &&(((Burst_length_1 == 1'b1 || Write_burst_mode == 1'b1) && Count_precharge [3] >= 1) || (Burst_length_2 == 1'b1 && Count_precharge [3] >= 2) ||(Burst_length_4 == 1'b1 && Count_precharge [3] >= 4) ||(Burst_length_8 == 1'b1 && Count_precharge [3] >= 8))) ||(RW_interrupt_write[3] == 1'b1 && WR_counter[3] >= 2)) beginAuto_precharge[3] = 1'b0;Write_precharge[3] = 1'b0;RW_interrupt_write[3] = 1'b0;#tWRa; // Wait for tWRPc_b3 = 1'b1;Act_b3 = 1'b0;RP_chk3 = $time;if (Debug) $display ("at time %t NOTE : Start Internal Auto Precharge for Bank 3", $time);endendendtask Burst;begin// Advance Burst CounterBurst_counter = Burst_counter + 1;// Burst Typeif (Mode_reg[3] == 1'b0) begin // Sequential BurstCol_temp = Col + 1;end else if (Mode_reg[3] == 1'b1) begin // Interleaved BurstCol_temp[2] = Burst_counter[2] ^ Col_brst[2];Col_temp[1] = Burst_counter[1] ^ Col_brst[1];Col_temp[0] = Burst_counter[0] ^ Col_brst[0];end// Burst Lengthif (Burst_length_2) begin // Burst Length = 2Col [0] = Col_temp [0];end else if (Burst_length_4) begin // Burst Length = 4Col [1 : 0] = Col_temp [1 : 0];end else if (Burst_length_8) begin // Burst Length = 8Col [2 : 0] = Col_temp [2 : 0];end else begin // Burst Length = FULLCol = Col_temp;end// Burst Read Single Write if (Write_burst_mode == 1'b1) beginData_in_enable = 1'b0;end// Data Counterif (Burst_length_1 == 1'b1) beginif (Burst_counter >= 1) beginData_in_enable = 1'b0;Data_out_enable = 1'b0;endend else if (Burst_length_2 == 1'b1) beginif (Burst_counter >= 2) beginData_in_enable = 1'b0;Data_out_enable = 1'b0;endend else if (Burst_length_4 == 1'b1) beginif (Burst_counter >= 4) beginData_in_enable = 1'b0;Data_out_enable = 1'b0;endend else if (Burst_length_8 == 1'b1) beginif (Burst_counter >= 8) beginData_in_enable = 1'b0;Data_out_enable = 1'b0;endendendendtask//**********************将SDRAM内的数据直接输出到外部文件*******************************///* integer sdram_data,ind;always@(sdram_r)beginsdram_data=$fopen("sdram_data.txt");$display("Sdram dampout begin ",sdram_data);

// $fdisplay(sdram_data,"Bank0:");for(ind=0;ind<=mem_sizes;ind=ind+1)$fdisplay(sdram_data,"%h %b",ind,Bank0[ind]);

// $fdisplay(sdram_data,"Bank1:");for(ind=0;ind<=mem_sizes;ind=ind+1)$fdisplay(sdram_data,"%h %b",ind,Bank1[ind]);

// $fdisplay(sdram_data,"Bank2:");for(ind=0;ind<=mem_sizes;ind=ind+1)$fdisplay(sdram_data,"%h %b",ind,Bank2[ind]);

// $fdisplay(sdram_data,"Bank3:");for(ind=0;ind<=mem_sizes;ind=ind+1)$fdisplay(sdram_data,"%h %b",ind,Bank3[ind]);$fclose("sdram_data.txt"); //->compare;end

*/integer sdram_data,sdram_mem;reg [23:0] aa,cc;reg [18:0] bb,ee;always@(sdram_r)begin$display("Sdram dampout begin ",$realtime);sdram_data=$fopen("sdram_data.txt");for(aa=0;aa<4*(mem_sizes+1);aa=aa+1)beginbb=aa[18:0];if(aa<=mem_sizes)$fdisplay(sdram_data,"%0d %0h",aa,Bank0[bb]);else if(aa<=2*mem_sizes+1)$fdisplay(sdram_data,"%0d %0h",aa,Bank1[bb]);else if(aa<=3*mem_sizes+2)$fdisplay(sdram_data,"%0d %0h",aa,Bank2[bb]);else$fdisplay(sdram_data,"%0d %0h",aa,Bank3[bb]);end $fclose("sdram_data.txt"); sdram_mem=$fopen("sdram_mem.txt");for(cc=0;cc<4*(mem_sizes+1);cc=cc+1)beginee=cc[18:0];if(cc<=mem_sizes)$fdisplay(sdram_mem,"%0h",Bank0[ee]);else if(cc<=2*mem_sizes+1)$fdisplay(sdram_mem,"%0h",Bank1[ee]);else if(cc<=3*mem_sizes+2)$fdisplay(sdram_mem,"%0h",Bank2[ee]);else$fdisplay(sdram_mem,"%0h",Bank3[ee]);end $fclose("sdram_mem.txt"); end // // Timing Parameters for -75 (PC133) and CAS Latency = 2

// specify

// specparam

tAH = 0.8, // Addr, Ba Hold Time

tAS = 1.5, // Addr, Ba Setup Time

tCH = 2.5, // Clock High-Level Width

tCL = 2.5, // Clock Low-Level Width

// tCK = 10.0, // Clock Cycle Time 100mhz

// tCK = 7.5, // Clock Cycle Time 133mhz

tCK = 7, // Clock Cycle Time 143mhz

tDH = 0.8, // Data-in Hold Time

tDS = 1.5, // Data-in Setup Time

tCKH = 0.8, // CKE Hold Time

tCKS = 1.5, // CKE Setup Time

tCMH = 0.8, // CS#, RAS#, CAS#, WE#, DQM# Hold Time

tCMS = 1.5; // CS#, RAS#, CAS#, WE#, DQM# Setup Time

// tAH = 1, // Addr, Ba Hold Time

// tAS = 1.5, // Addr, Ba Setup Time

// tCH = 1, // Clock High-Level Width

// tCL = 3, // Clock Low-Level Width

tCK = 10.0, // Clock Cycle Time 100mhz

tCK = 7.5, // Clock Cycle Time 133mhz

// tCK = 7, // Clock Cycle Time 143mhz

// tDH = 1, // Data-in Hold Time

// tDS = 2, // Data-in Setup Time

// tCKH = 1, // CKE Hold Time

// tCKS = 2, // CKE Setup Time

// tCMH = 0.8, // CS#, RAS#, CAS#, WE#, DQM# Hold Time

// tCMS = 1.5; // CS#, RAS#, CAS#, WE#, DQM# Setup Time

// $width (posedge Clk, tCH);

// $width (negedge Clk, tCL);

// $period (negedge Clk, tCK);

// $period (posedge Clk, tCK);

// $setuphold(posedge Clk, Cke, tCKS, tCKH);

// $setuphold(posedge Clk, Cs_n, tCMS, tCMH);

// $setuphold(posedge Clk, Cas_n, tCMS, tCMH);

// $setuphold(posedge Clk, Ras_n, tCMS, tCMH);

// $setuphold(posedge Clk, We_n, tCMS, tCMH);

// $setuphold(posedge Clk, Addr, tAS, tAH);

// $setuphold(posedge Clk, Ba, tAS, tAH);

// $setuphold(posedge Clk, Dqm, tCMS, tCMH);

// $setuphold(posedge Dq_chk, Dq, tDS, tDH);

// endspecifyendmodule仿真测试结果

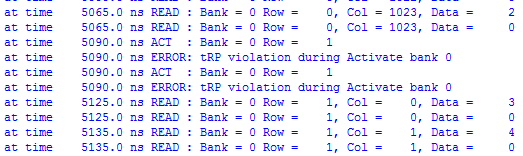

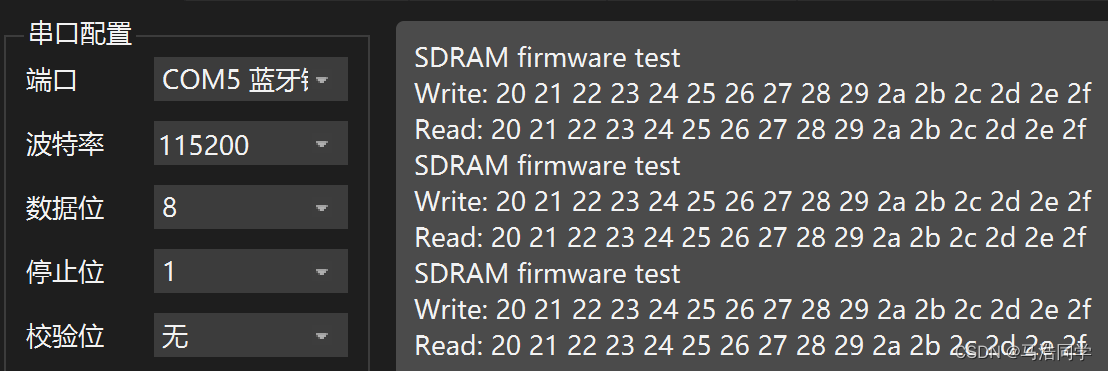

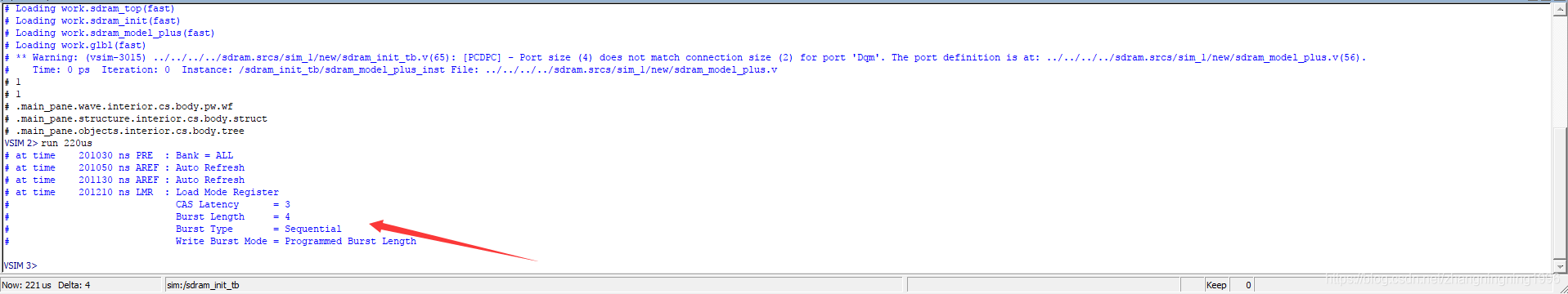

这里给出modelsim的仿真结果如下:

出现上述结果,说明SDRAM的上电初始化成功,上面也打印出来了配置具体的模式。

接下来我们会写出SDRAM的刷新模块、读写模块。

参考文献

[1] 开源骚客

总结

创作不易,认为文章有帮助的同学们可以关注点赞支持。(工程也都在群中)对文章有什么看法或者需要更近一步交流的同学,可以加入下面的群: