目录

1、名词解释

2、SDRAM 内部结构

3、SDRAM 外部信号描述

4、SDRAM 命令

4.1、COMMAND INHIBIT

4.2、NO OERATION

4.3、ACTIVE

4.4、LOAD MODE REGISTER (LMR)

4.5、READ

4.6、WRITE

4.7、PRECHARGE

4.8、BURST TERMINATE

4.9、REFRESH

4.9.1、AUTO REFRESH

4.9.2、SELF REFRESH

5、SDRAM 状态

5.1、Idle

5.2、Row active

5.3、Read

5.4、Write

5.5、Refreshing

5.6、Accessing mode register

5.6、Precharging all

6、SDRAM 初始化

7、Mode Register

7.1、Burst Length

7.2、Burst Type

7.3、CAS latency

8、Read operations

8.1、连续读

8.2、随机读

8.3、读过程中去 precharge

8.4、burst 读并终止

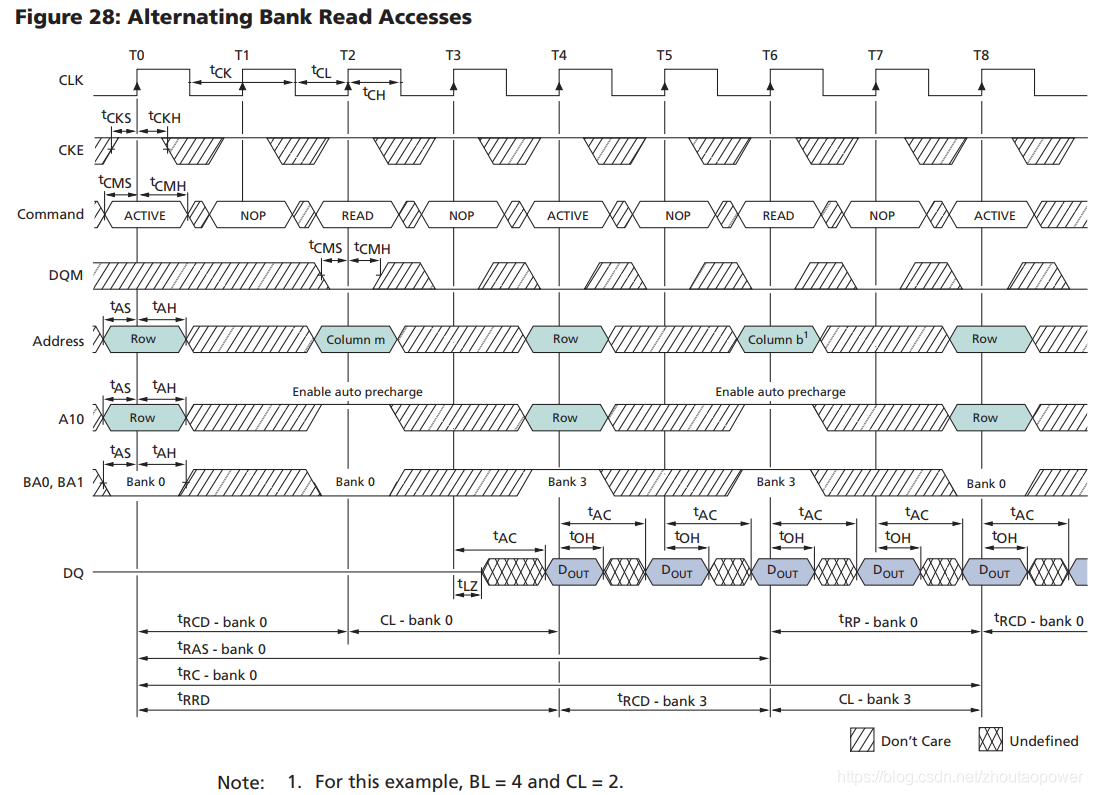

8.5、交替读

9、Write operations

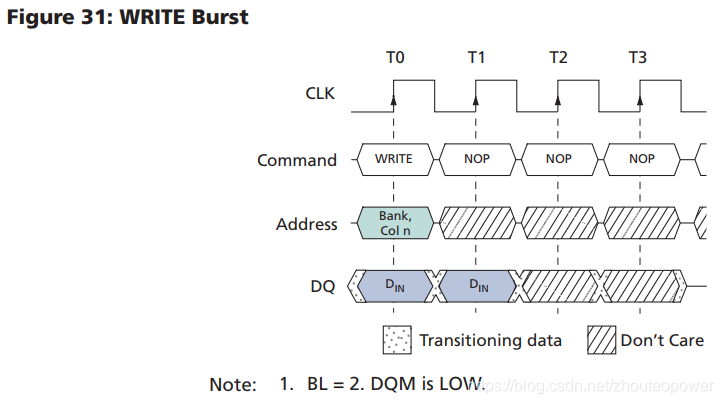

9.1、Burst 写

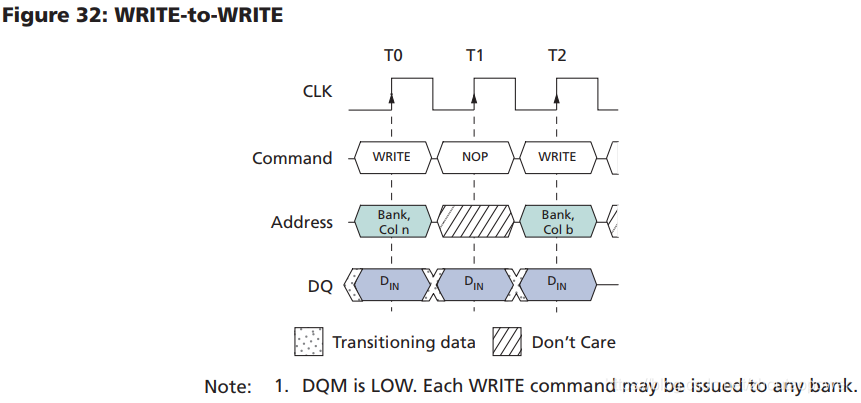

9.2、换列写

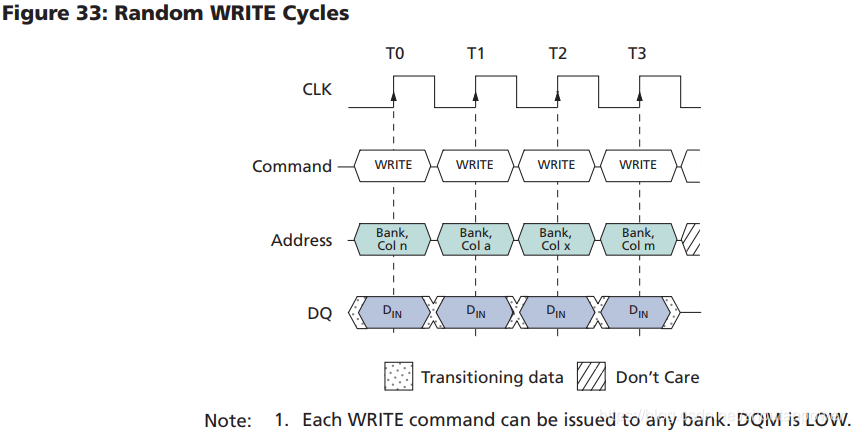

9.3、随机写

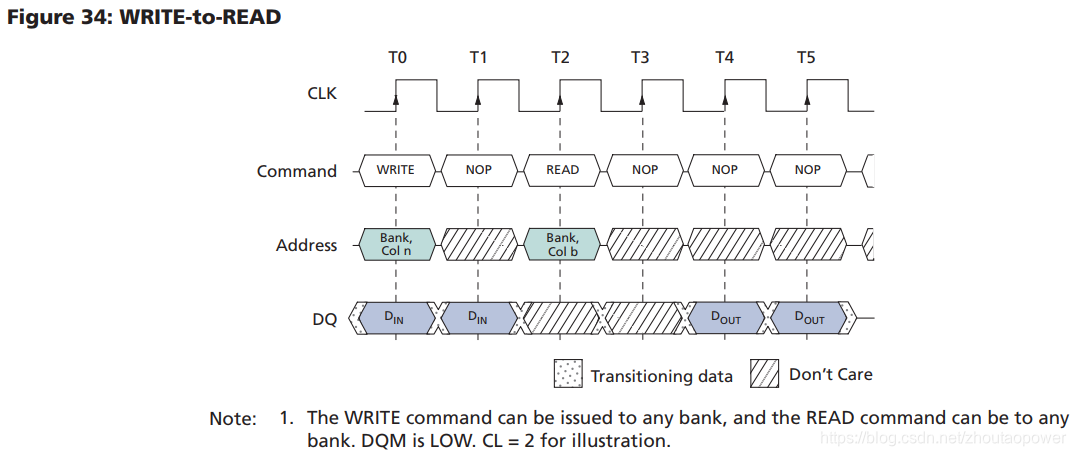

9.4、写转读

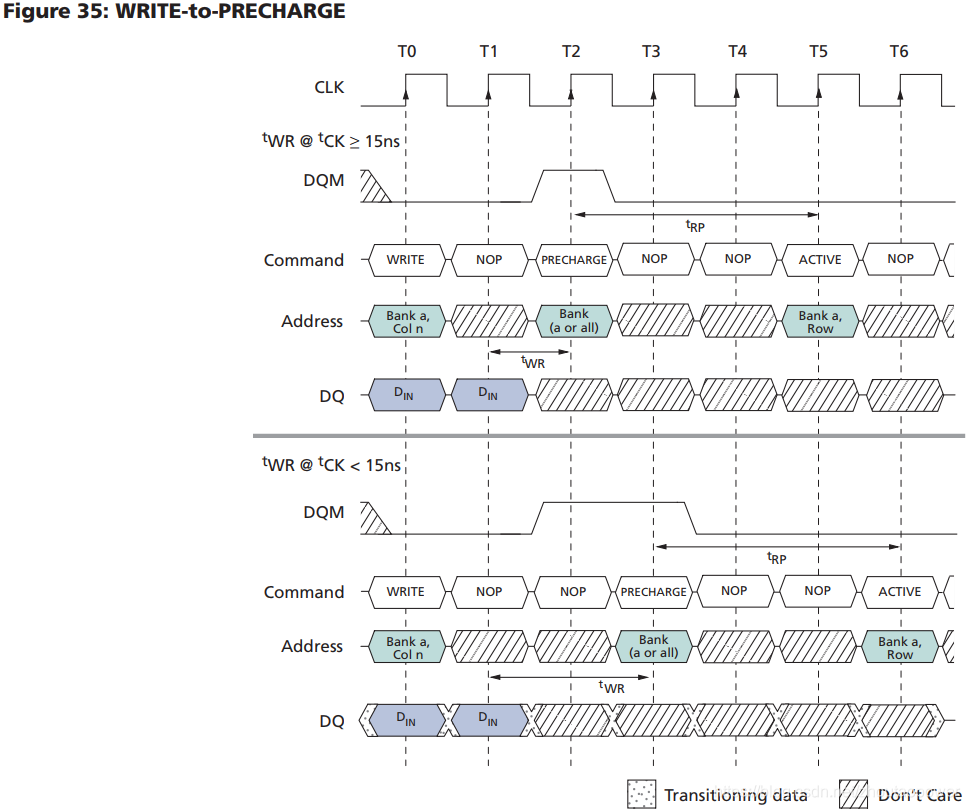

9.5、写转precharge

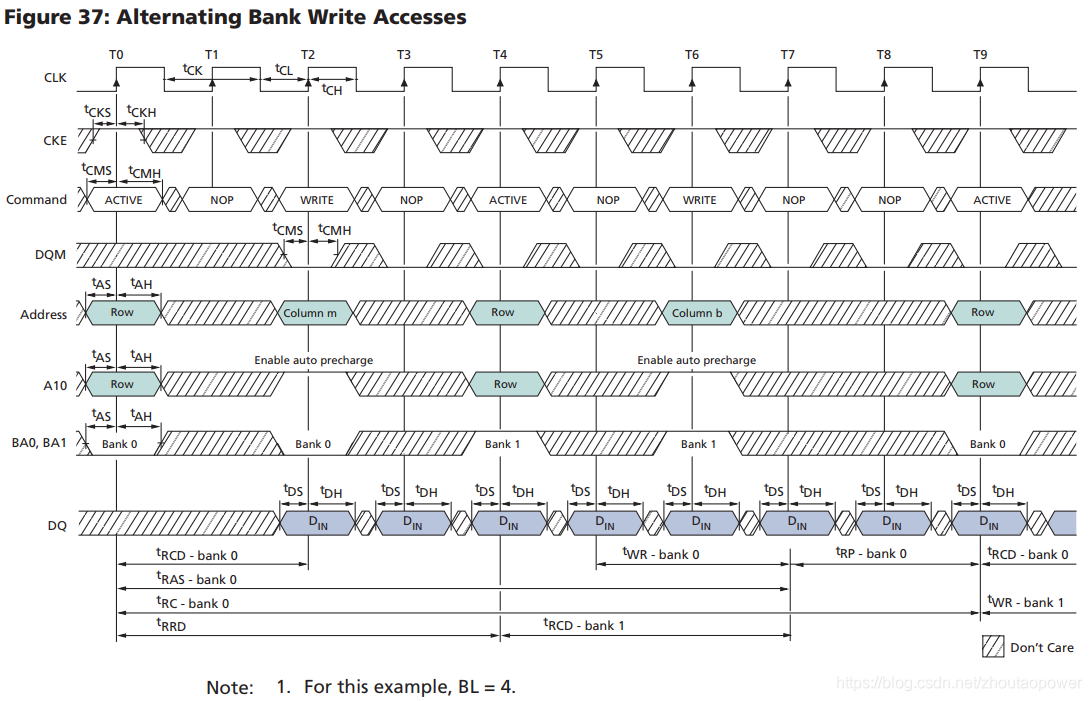

9.6、交替写

10、PRECHARGE Operation

11、AUTO REFRESH Operation

12、SELF REFRESH Operation

13、POWER DOWN

14、Clock Suspend

15、驱动

1、名词解释

SDRAM :Synchronous Dynamic Random Access Memory,同步动态随机存储器。同步是指其时钟频率和CPU前端总线的系统时钟相同,也就是双方通信,有同步时钟;内部命令的发送与数据的传输都以它为基准;动态是指存储阵列需要不断的刷新来保证数据不丢失;随机是指数据不是线性依次存储,而是自由指定地址进行数据的读写。

NOTES:这里需要强调一下:为了保证数据一直都在,SDRAM 需要不停的去刷新,刷新,刷新;

2、SDRAM 内部结构

这里以 MICRON(美光)的 SDRAM(MT48LC16M16A2P-6AIT_256Mb_SDRAM)为例,进行 SDRAM 的结构介绍;

这款 SDRAM 有几种规格:

1、16 Meg x 4 x 4 banks

2、 8 Meg x 8 x 4 banks

3、 4 Meg x 16 x 4 banks

MT48LC16M16A2P-6AIT_256Mb_SDRAM 属于 :4 Meg x 16 x 4 banks,16 位的数据总线;

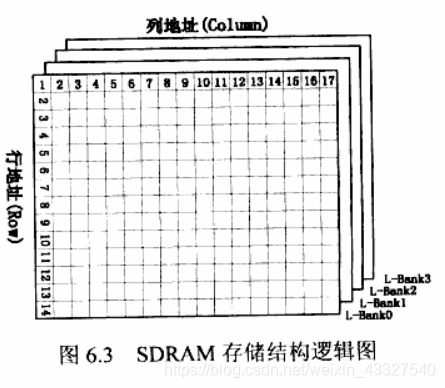

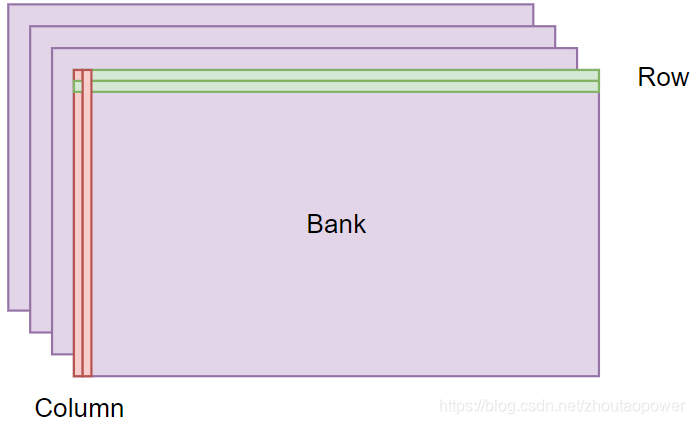

首先,先说一下存储结构,其实存储内部是由 Row、Column、Bank 组成:

其中:

紫色部分,是 Bank,这款 SDRAM 有 4 个 Bank;

红色部分,是 Column,列;

绿色部分,是 Row,行;

那么不同组成部分的解释为:

1、16 Meg x 4 x 4 banks : 8192 row、2048 columns、by 4 bits

2、 8 Meg x 8 x 4 banks:8192 row、1024 columns、by 8 bits

3、 4 Meg x 16 x 4 banks:8192 row、512 columns、by 16 bits

那么 16Meg x16 他的内部是这样的:

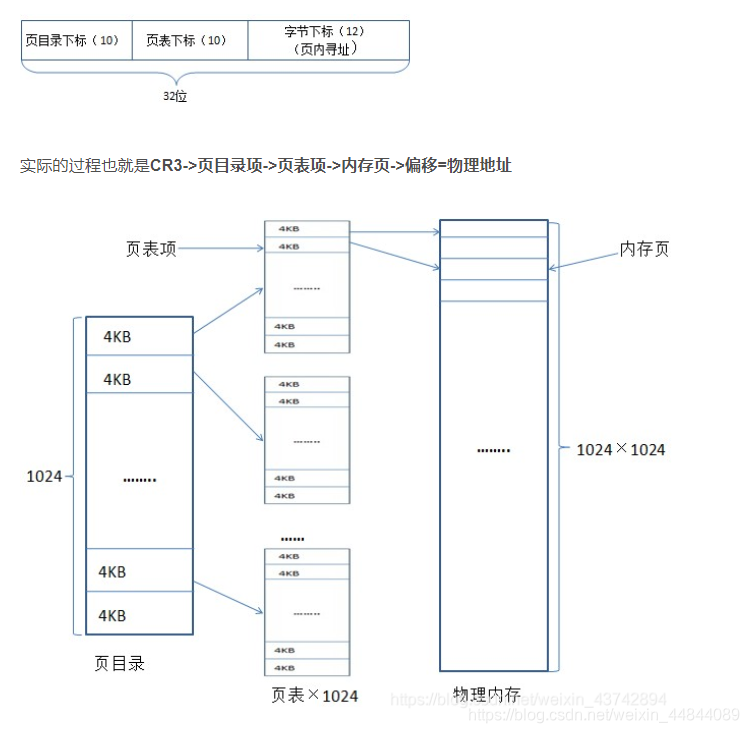

所以呢,如果我们要寻址一个 SDRAM 内部的单元,我们需要给出 3 个参数,Row、Colunm、Bank;

细心的读者可能看到,输入的地址总线只有 A[12:0],这代表可寻址的空间只有 2^13 = 8KB,那是如何访问到 256Mbit(32MB) 的空间的呢?稍安勿躁,看后面描述;

3、SDRAM 外部信号描述

我们来看看 SDRAM 的信号线描述:

| 引脚代号 | 定义 |

| Vdd/VddQ | 工作/DQ电压 |

| Vss/VssQ | 相应电压的接地 |

| DQ[15:0] | 数据I/O线 |

| A[12:0] | 行列地址线 |

| DQML/DQMH | 数据掩码 |

| CS# | 片选(低电平有效) |

| CAS# | 列地址选通脉冲(低电平有效) |

| RAS# | 行地址选通脉冲(低电平有效) |

| WE# | 读写信号(低电平有效) |

| CK | 时钟信号 |

| CKE | 时钟有效 |

| BA[1:0] | Bank 选择信号 |

可以看出来了吧,选择 Bank 的话,一共 4 个 Bank,2bit 就可以了,也就是 BA[1:0];

专门有 CAS# 和 RAS# 信号给到 SDRAM,告知,当前的 A[12:0] 代表的行地址,还是列地址;

那么,一切就说得通了;

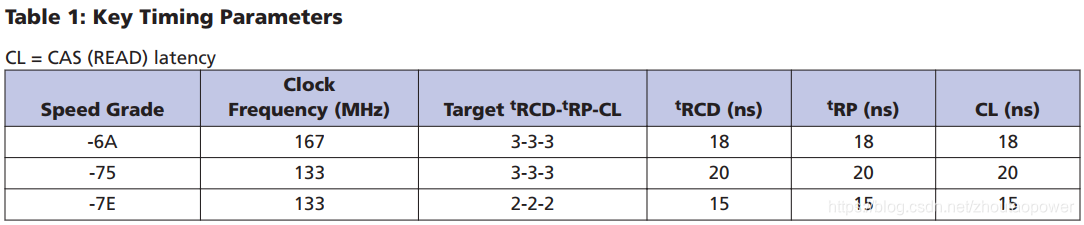

Datasheet 中描述到一个概念:Speed Grade:-6A、-75、-7E,也代表了不同规格的 SDRAM,速率不一样,时序参数也有所区别;时序部分,下面在仔细看;

另外,Datasheet 还描述了三种另外的规格:分别叫:

commercial:商业级

industrial:工业级

automotive:车规级

他们的时序和温度要求,可靠性要求有所不一样,但是大致都差不多,这里,我们暂时忽略他们的区别;

4、SDRAM 命令

介绍完 SDRAM 的结构组成、以及信号后,接下来介绍一下他的命令;啥?他还有命令?当然,SDRAM 也有他自己的控制器和状态机,我们要用它,就需要深入了解他;

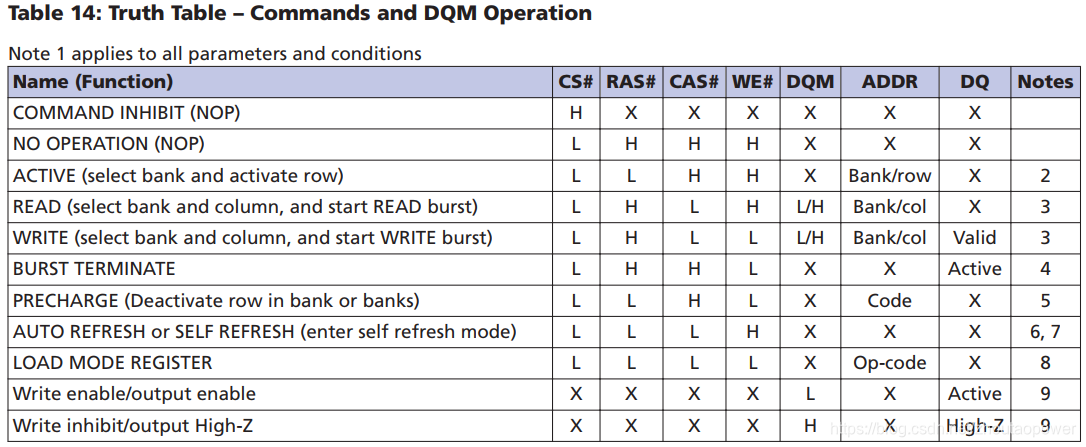

首先需要说明一下,SDRAM 的命令,是外部发给 SDRAM 的,也就是 CPU 或者 MCU;SDRAM 引脚就这么多,那么如何发送命令呢?肯定就是不同引脚上不同的电平状态的组合了:

可以看到,SDRAM 支持如下命令:

COMMAND INHIBIT(NOP):空指令;

NO OERATION(NOP):空指令;

ACTIVE:选择 bank 和 row 的指令;

READ:选择 bank 和 column ,并且开始读数据的指令;

WRITE:选择 bank 和 column ,并且开始写数据的指令;

BURST TERMINATE:终止 Burst 指令;

PRECHARGE:预充电指令(会使得 bank 中的 row 变成 deactivate 状态);

AUTO REFRESH or SELF REFRESH:刷新指令;

LOAD MODE REGISTER:配置寄存器指令;

可以看到,发送这些指令,都是靠不同电平状态下的各个信号组合而成;

4.1、COMMAND INHIBIT

COMMAND INHIBIT 指令,不管 CLK 是否被使能,发送 COMMAND INHIBIT 指令的功能是阻止新的指令执行;

4.2、NO OERATION

NO OERATION 指令是为了发送 NOP 不想让其他的命令占用设备;

4.3、ACTIVE

当设备处于 IDLE 状态的时候,ACTIVE 指令用于激活指定 bank 的指定 row;其中 BA[1:0] 用于指定 Bank;

注意:在发送 PRECHARGE 命令之前,当前的 row 都可以持续被访问,直到该 bank 被发送了 PRECHARGE 命令;在打开同一个 bank 的不同 row 之前,PRECHARGE 命令都必须先被发送;

看到这里,小伙伴肯定很懵逼,什么又是选中 bank + row,什么又是 PRECHARGE 命令;不着急,后面我会再次汇总,现在有一个概念就可以了:访问一个 row 之前,必须先执行 PRECHARGE 命令(可以理解为,对他充电),要访问其他 row,需要再次充电;

4.4、LOAD MODE REGISTER (LMR)

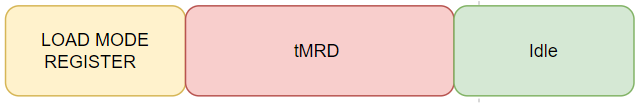

刚刚不是说了么,SDRAM 也有自身的控制逻辑,这个控制逻辑有一部分是在 SDRAM 的寄存器里面,有且只有一个寄存器,就是这个 LOAD MODE REGISTER;我们在使用之前,需要去配置他,就是通过发送这个 LMR 命令配置;

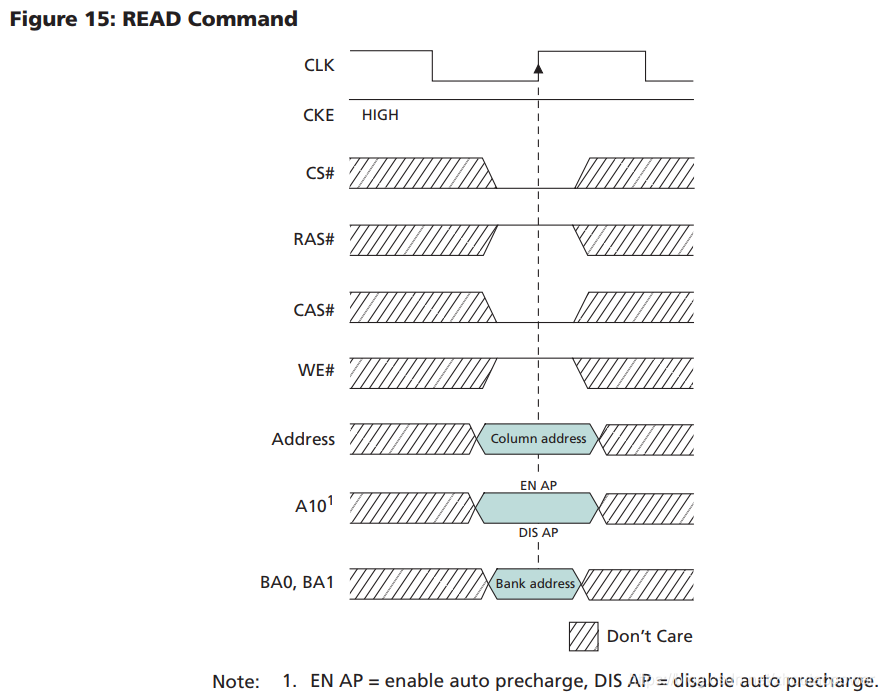

4.5、READ

读命令是用来在 ACTIVE 命令之后,去选择 column ,并且发起 burst 读的;在读命令的时候,需要注意两点:

1、READ 的时候呢,A10 这个位,标记了,是否需要使用 auto precharge 功能;这里会衍生出几个问题:

1.1、A10 不是地址线么,为啥拿来做标志位了?:

因为在 READ 阶段,属于选 column 阶段,ACTIVE 阶段使用到 A[12:0],在 READ 阶段,只用到了:x4: A[9:0], A11; x8: A[9:0]; x16: A[8:0],,对于我们这块来说,就是 A[8:0];所以不管怎么说,这个阶段选择列,最大用到 10bit,那么 A10 (也就是第 11 bit 就可以挪作他用了)

1.2、auto precharge 是啥?

如果 auto precharge 被选择,那么就意味着,在这次 READ 结束的时候,会自动跟上一个 precharge 的操作;这个操作上了以后呢,就使得这个 row 变为了一个 inactive 状态,无法立即访问该 row;

如果 auto precharge 没有被选择,那么就意味着,在这次 READ 结束的时候,不会自动跟上一个 precharge 的操作;该 row 可以再次立即被访问;

现在你只需要知道,每次访问一个 row,都要先 precharge,然后等上一个时间;

2、READ 的时候呢,DQM 这个信号起作用了,这个 DQM 是什么意思呢?

数据掩码的意思,就是代表了那些位的数据是需要的,DQM分为 2 bit,DQMH 和 DQML,分别代表了高 D[15:8] 和 D[7:0]

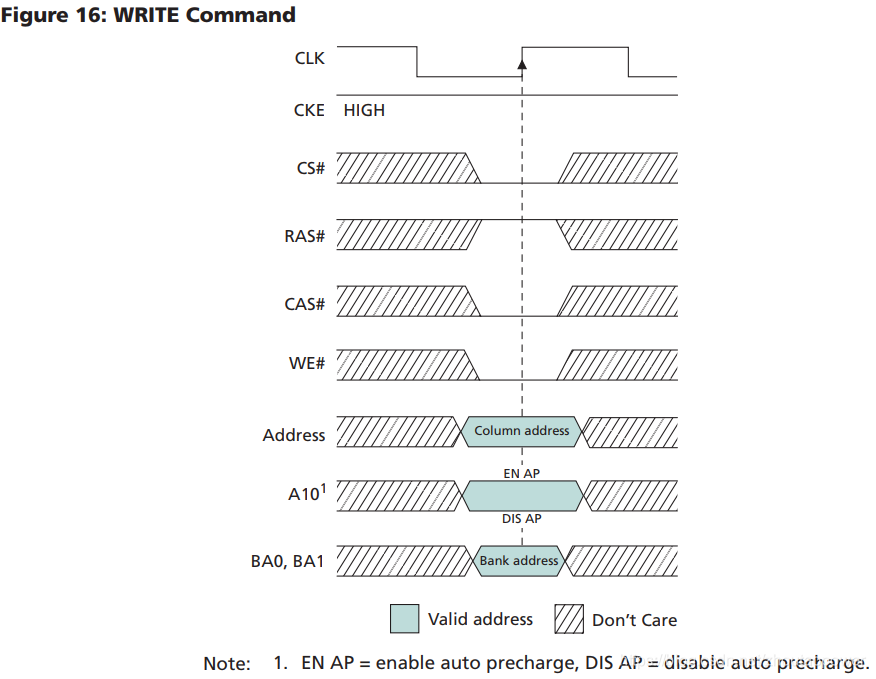

4.6、WRITE

写命令基本上和 READ 是一样的,只不过变成了数据写入 SDRAM,在这个阶段,也是选择 column;其他都和 READ 一样,不再多说:

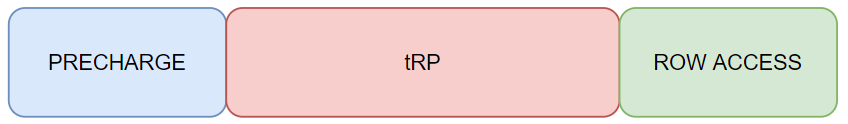

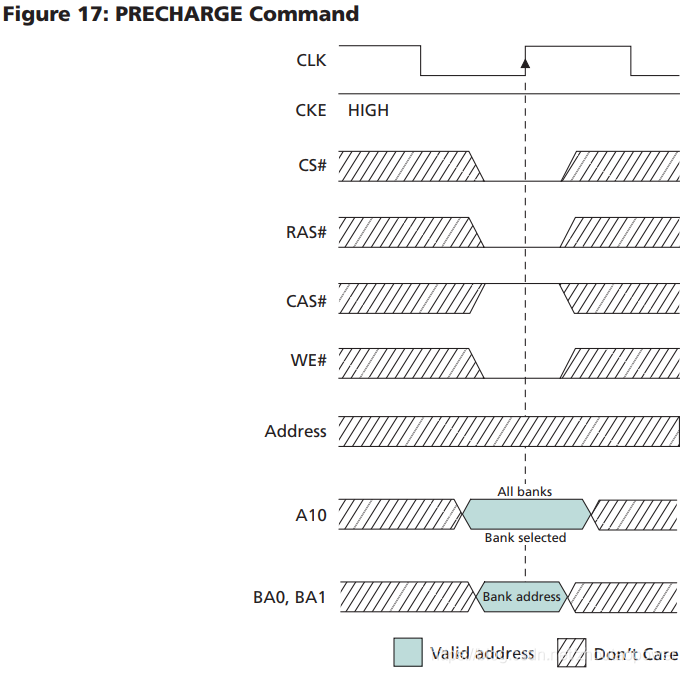

4.7、PRECHARGE

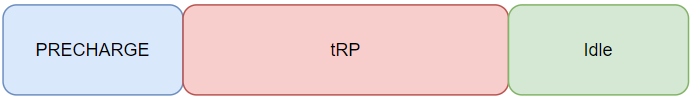

PRECHARGE 命令用于指定的 bank 的 处于 open 状态下的 row 进入 deactivate 状态,或者也可以让所有的 bank 的 row 都进入 deactivate 状态;当发送 PRECHARGE 命令后,经过一个指定的时间:tRP,指定 bank 的指定 row 就将可以被访问;

A10 在这个过程中,依然充当了另外角色,指示了是要指定 bank 的 row 进入deactivate 状态,还是 all bank 的 row 进入 deactivate 状态;

4.8、BURST TERMINATE

用于终止一个 Burst 传输;

4.9、REFRESH

为了保持 SDRAM 的数据一直都在,需要不停的刷新,刷新分为两种类型如下:

4.9.1、AUTO REFRESH

第一种叫 AUTO 类型,这里说是 AUTO,其实一点都不 AUTO,就是需要手动去刷新(或者称之为 MCU 或者 CPU 端的 SDRAM Controller 去主动刷新),所以,就必须在一个指定的时间间隔之内,去刷新一次,也就是发送一次这个指令;

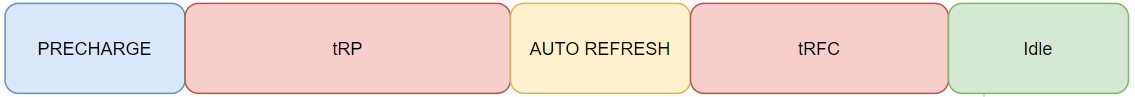

在每次发送 AUTO REFRESH 之前,所有的 active bank 都必须被 precharged 一次;

在发送 PRECHARGE 之后,需要等待 tRP 时间,然后在去发送 AUTO REFRESH 指令;

在发送 AUTO REFRESH 命令期间,地址会在内部自动去递增的生成,所以,在这期间,外部输入的地址信息,是无效的;

根据 Spec 的要求,256Mb SDRAM 需要 8192 次 AUTO REFRESH Cycles 每 64ms (针对商业级和工业级的 SDRAM) 或者 16ms (车规级 SDRAM).

当然,这种刷新,你既可以按照时间来进行等时的刷新(比如你吧 64ms 分为 8192 份,就可以得到 7.813μs 就要刷新一次),当然,也可以在 64ms 到之前,一次性发送 8192 个 AUTO REFRESH,来一次性完成刷新;

4.9.2、SELF REFRESH

SELF REFRESH 这种才是真的自动刷新,它不需要外部参与,完全依靠 SDRAM 的内部时钟来刷新,从而保持内部数据;

这种刷新,需要将 CKE 信号拉低,也就是时钟的使能信号;

SDRAM 在进入这种模式后,最少持续时间是 tRAS,最长时间是无限期;

如果要推出 SELF REFRESH,需要几步:

1、CLK 必须要稳定

2、CKE 拉高

3、至少 2 个周期的 NOP 指令(tXSR),因为内部需要完成他的 refresh;

4、退出 SELF REFRESH 后,以后的刷新都要交给上面的 AUTO REFRESH 了;

5、SDRAM 状态

SDRAM 定义了几种状态如下:

5.1、Idle

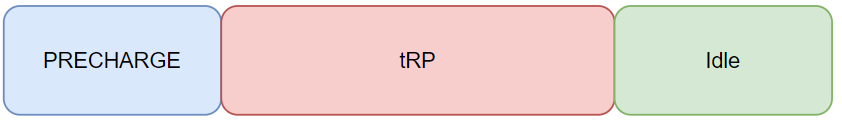

当 bank 被 precharged 后,等了 tRP 时间后,SDRAM 处于 Idle 状态:

5.2、Row active

处于 Idle 状态的 SDRAM,收到 ACTIVE 后,bank 和 row 被选中,并等待了 tRCD 时间后的状态:

5.3、Read

处于 Row active 状态的 SDRAM,收到 READ 后,bank 和 column 被选中后的状态:

5.4、Write

处于 Row active 状态的 SDRAM,收到 WRITE 后,bank 和 column 被选中后的状态:

5.5、Refreshing

当发送 Refresh 后,等待 tRFC 时间,bank 进入 idel;

5.6、Accessing mode register

当发送 LOAD MODE REGISTER 指令后,等 tMRD 时间:

5.6、Precharging all

发送 Precharging 后等待 tRP 时间:

小结:命令+时序,组成了状态,各个状态直接,又有顺序的联系;

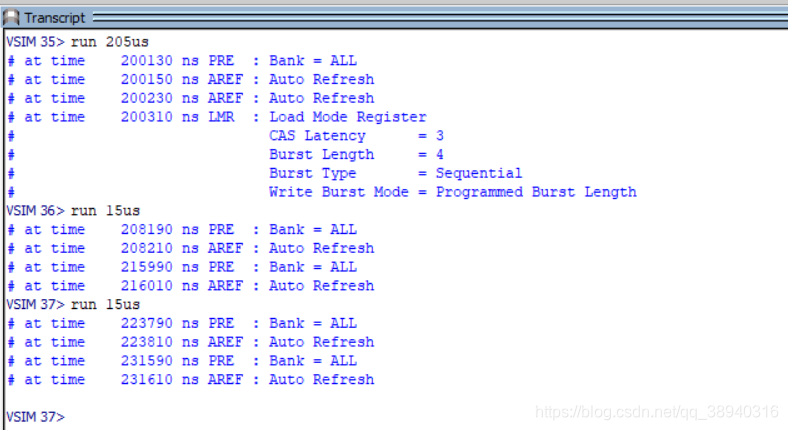

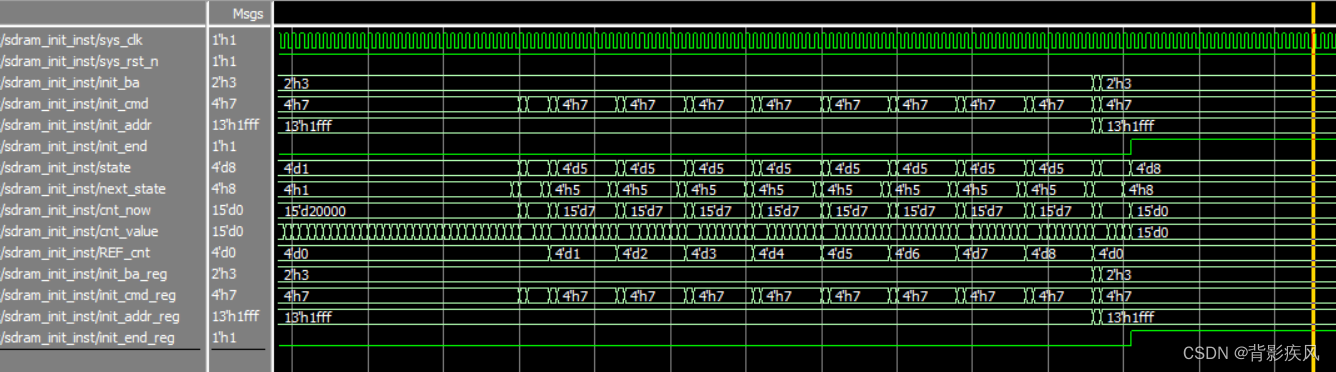

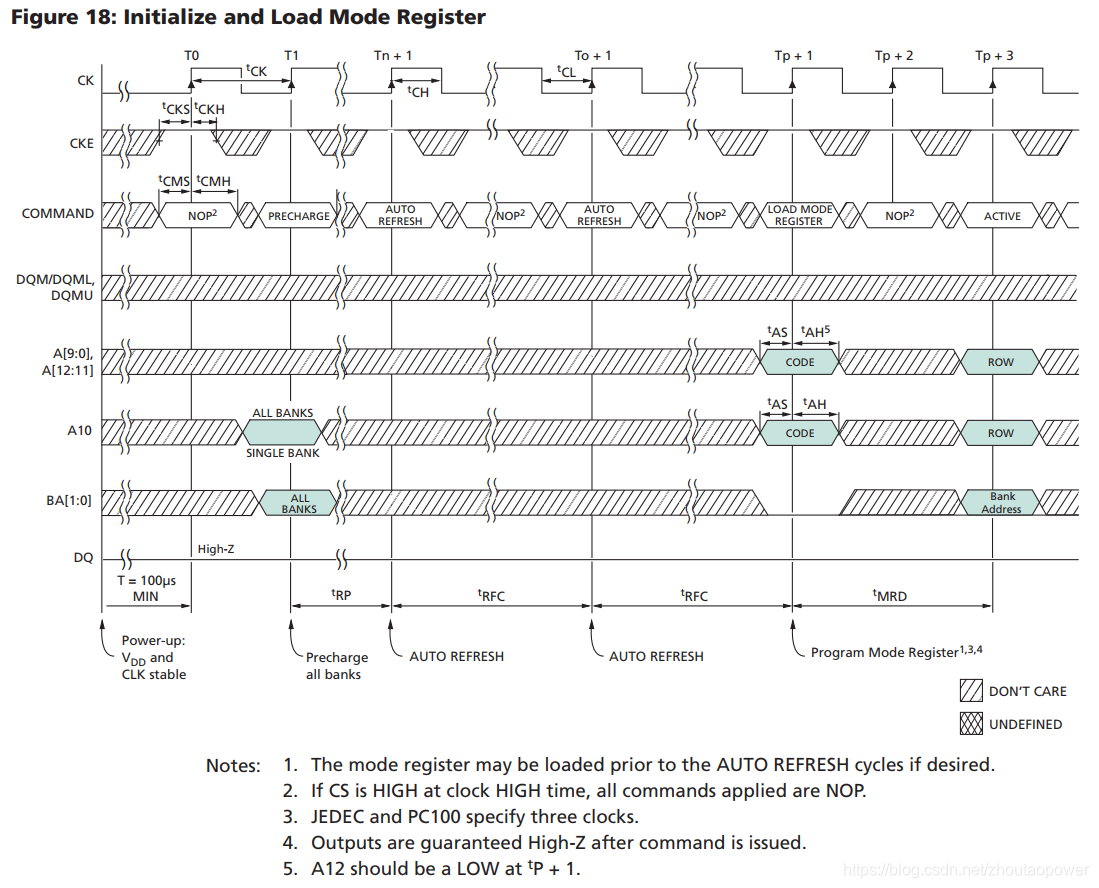

6、SDRAM 初始化

上面讲完了命令,状态,时序,下面是初始化的流程:

1、VDD 和 VDDQ 上电;

2、拉低 CKE;

3、CLK 稳定;

4、等 100us;

5、拉 CKE 高;

6、发送 PRECHARGE ALL 指令;

7、等待至少 tRP 时间;

8、发送 AUTO REFRESH 指令并等待 tRFC;

9、发送 AUTO REFRESH 指令并等待 tRFC(第二次);

10、现在 SDRAM 已经可以接受配置 REGISTER 了,上电时刻,mode register 是随机值,所以我们必须配置它;通过 LMR 指令配置 mode register;

11、等待至少 tMRD 时间;

12、此刻 SDRAM 初始化完成,可以被访问;

整个初始化流程和时序如下:

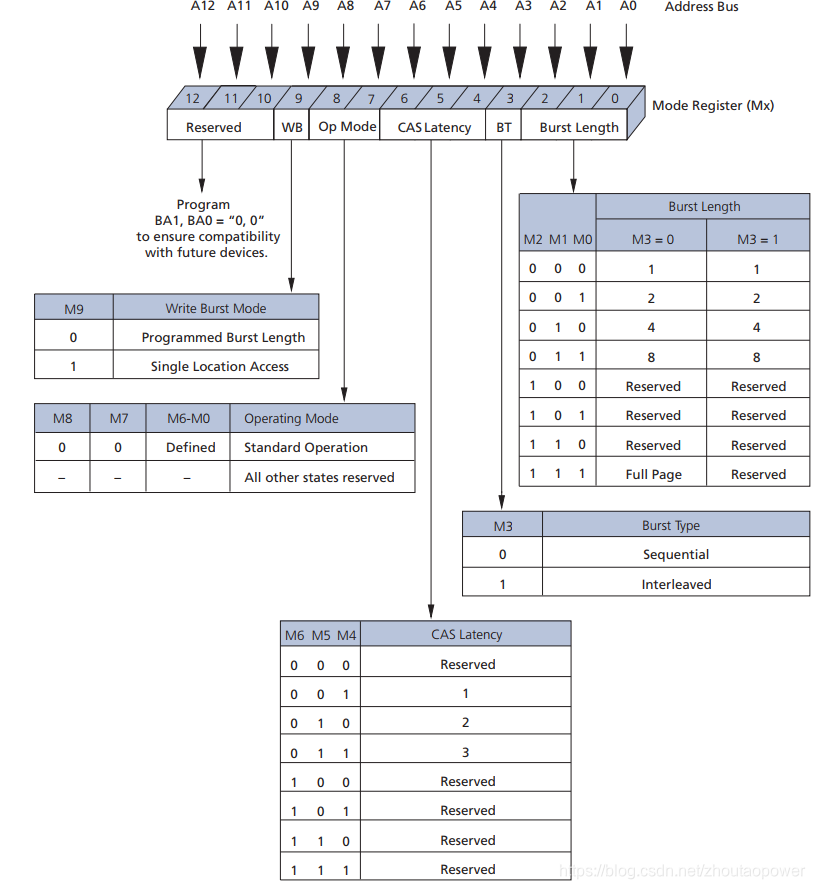

7、Mode Register

讲完了初始化,那么这个 mode register 到底是何方神圣呢?

Mode register 是 SDRAM 部分的控制逻辑,它定义了一个 16bits 的寄存器,里面包含了 burst len(BL),burst type, CAS latency (CL),操作模式等:

7.1、Burst Length

突发长度决定了给定 READ 或 WRITE 命令可以访问的最大列位置数。突发长度为 1、2、4、8 或连续位置可用于顺序和交错突发类型,连续页突发可用于顺序类型。连续页突发与 BURST TERMINATE 命令结合使用以生成任意突发长度。

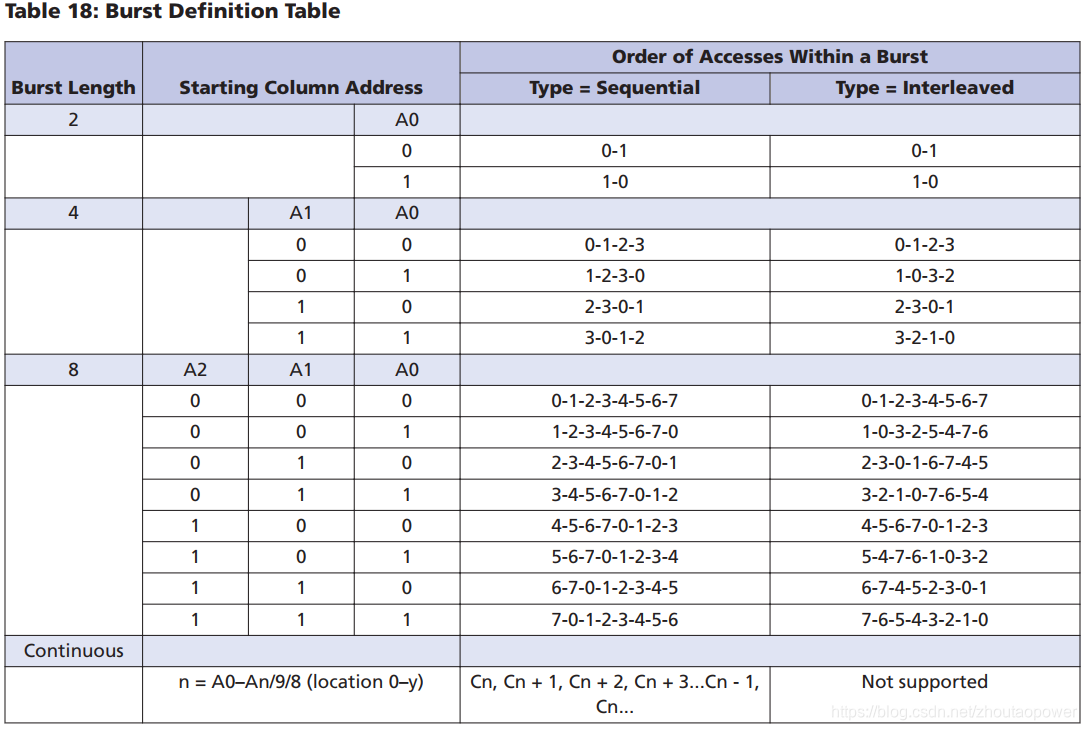

7.2、Burst Type

突发类型定义了2种,一个是顺序,另一个是交错,他和 Burst len 组合如下:

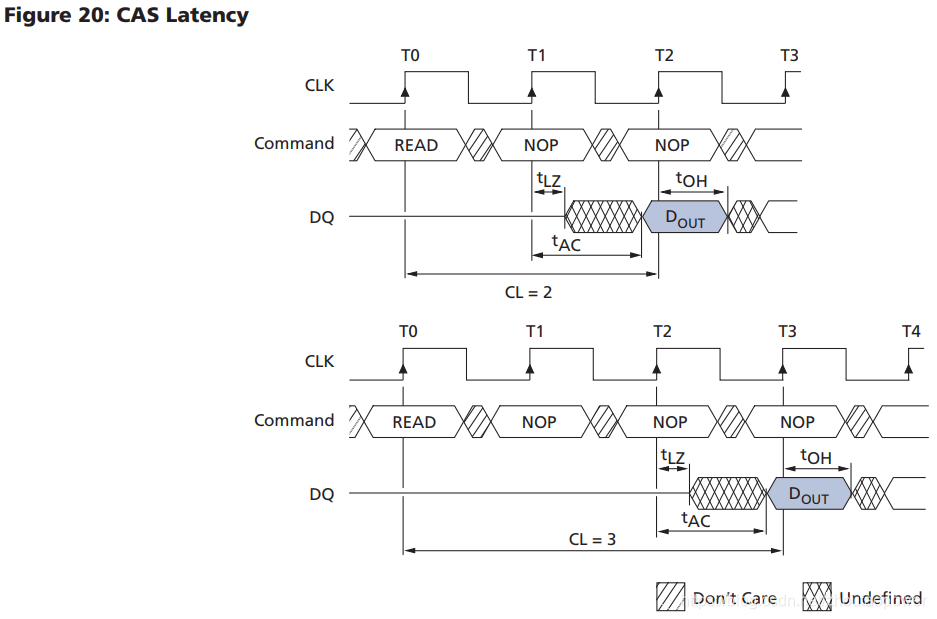

7.3、CAS latency

CAS latency 指的是,在 READ 操作的时候,数据延时几个 CLK 出来;这个值可以配置位 2 或者 3;

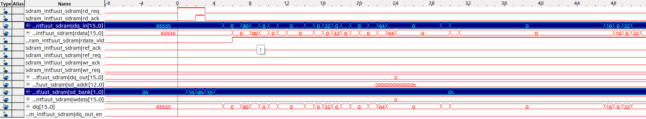

8、Read operations

读操作有很多次 case,spec 里面列出来很多,这里就简单截图:

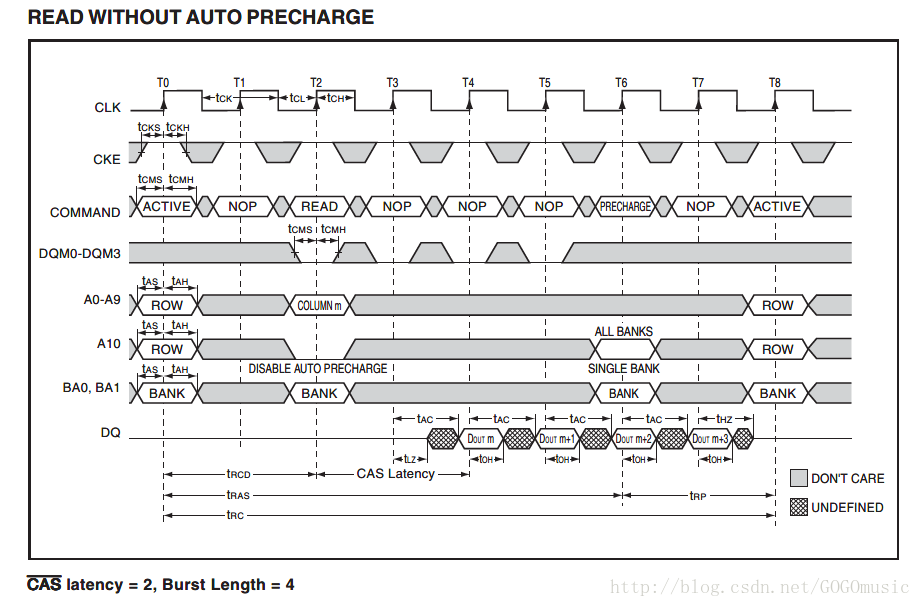

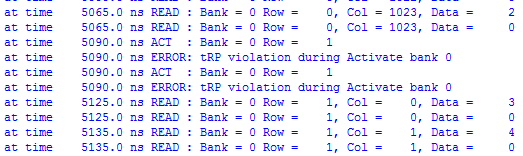

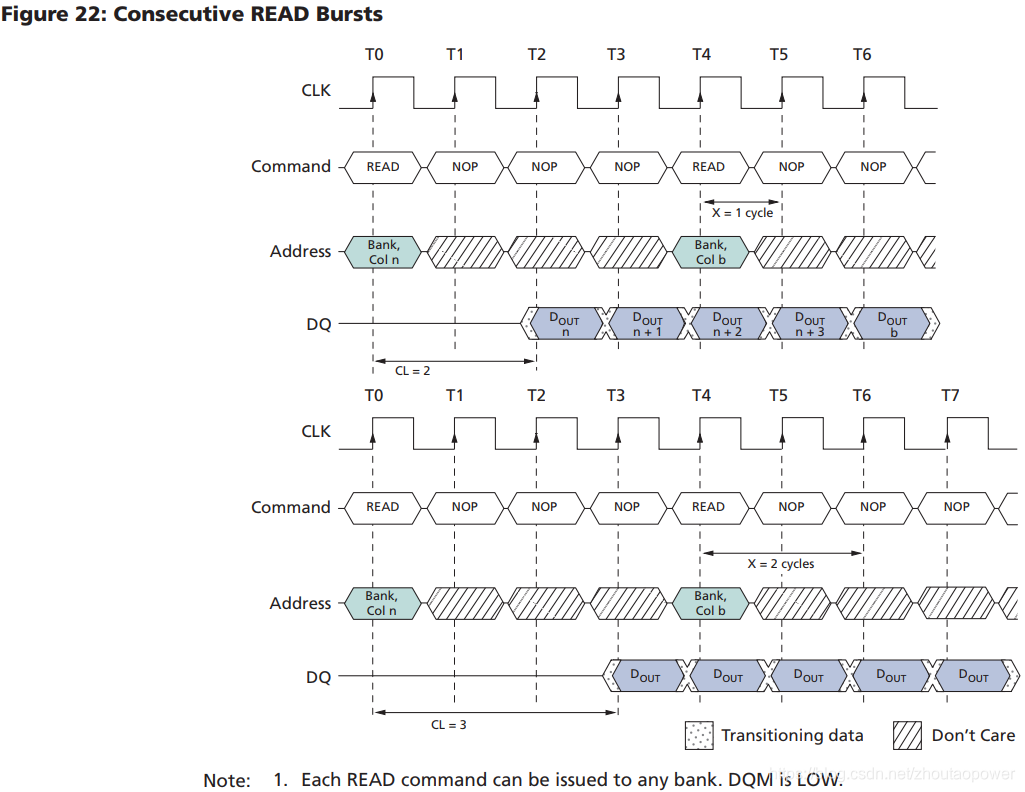

8.1、连续读

分别列出来 CL=2 和 CL=3 的情况,先读 Bank 的 n 列,如果没有换的话,burst 会继续读 n+1、n+2....

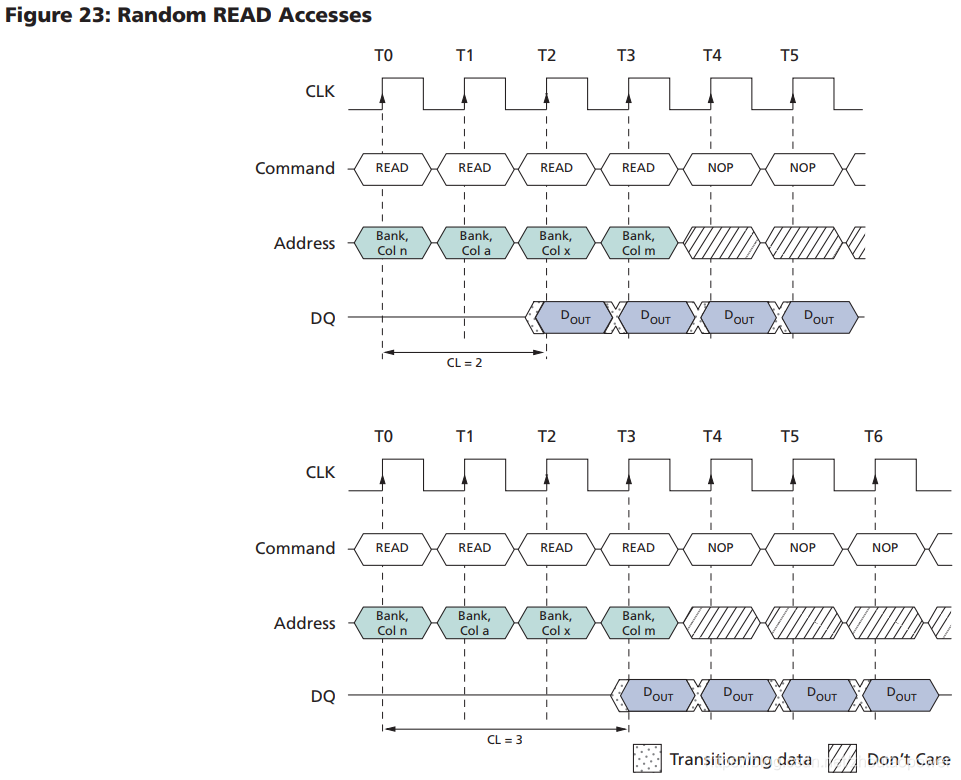

8.2、随机读

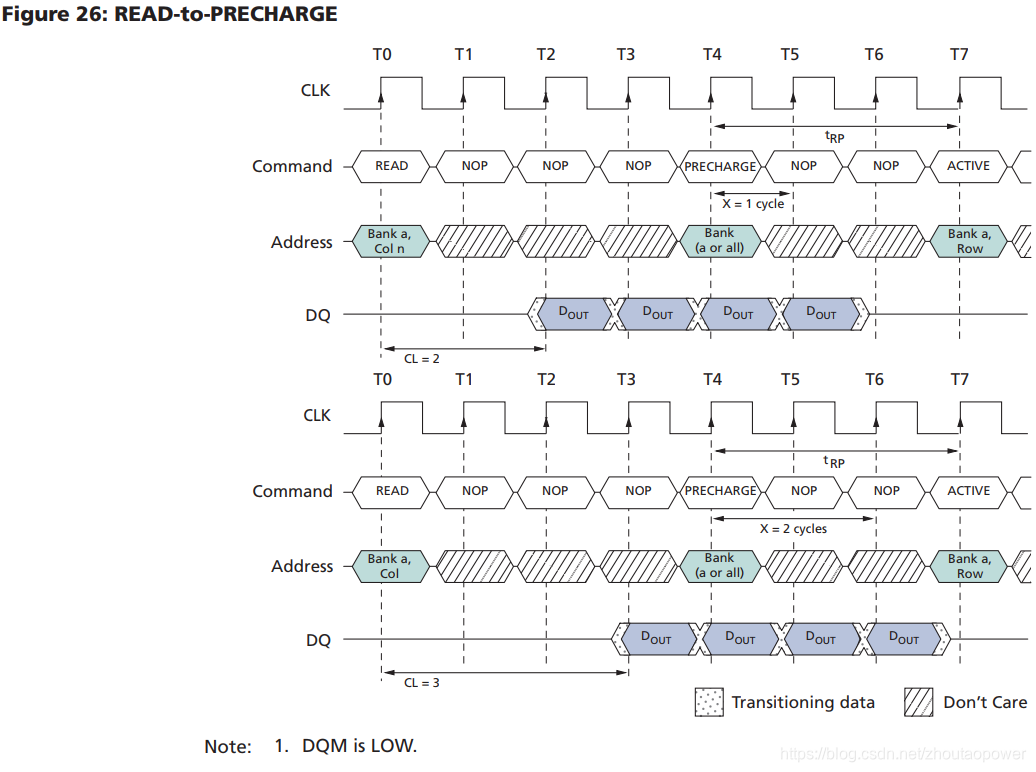

8.3、读过程中去 precharge

读过程中去 precharge 后,需要再次发送 ACTIVE ;

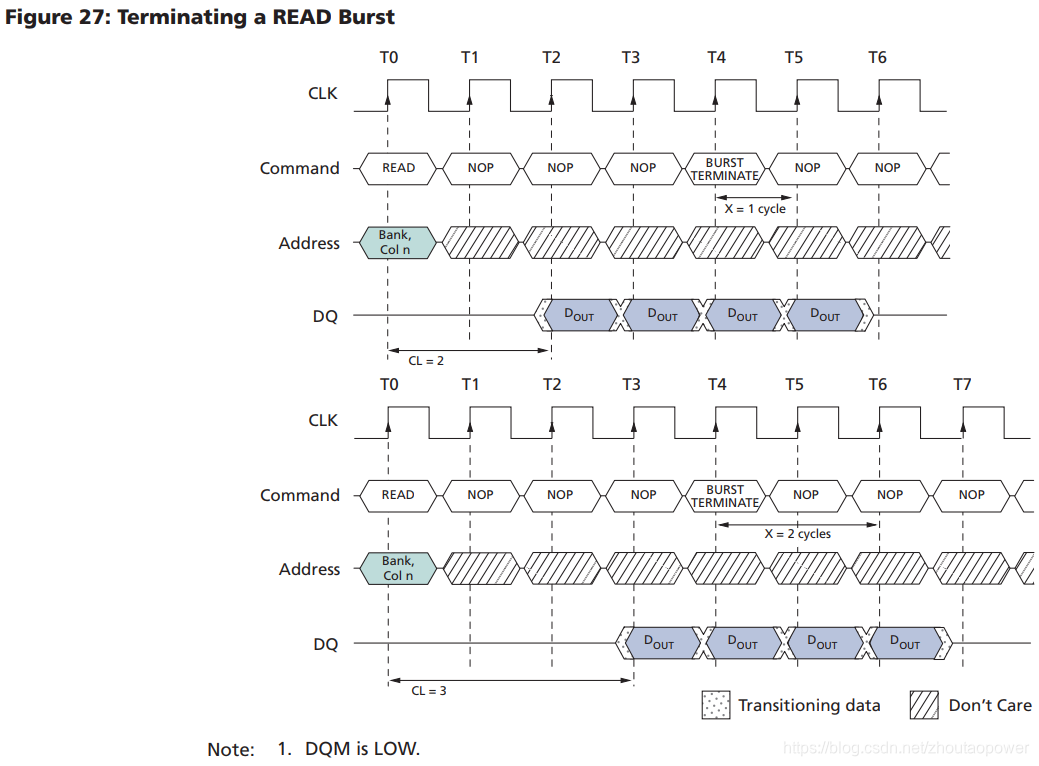

8.4、burst 读并终止

读的过程中,发送 BURST TERMINATE;

8.5、交替读

9、Write operations

写的时序类似

9.1、Burst 写

9.2、换列写

9.3、随机写

9.4、写转读

9.5、写转precharge

9.6、交替写

10、PRECHARGE Operation

11、AUTO REFRESH Operation

12、SELF REFRESH Operation

13、POWER DOWN

14、Clock Suspend

这些部分参考 Spec,不再赘述;

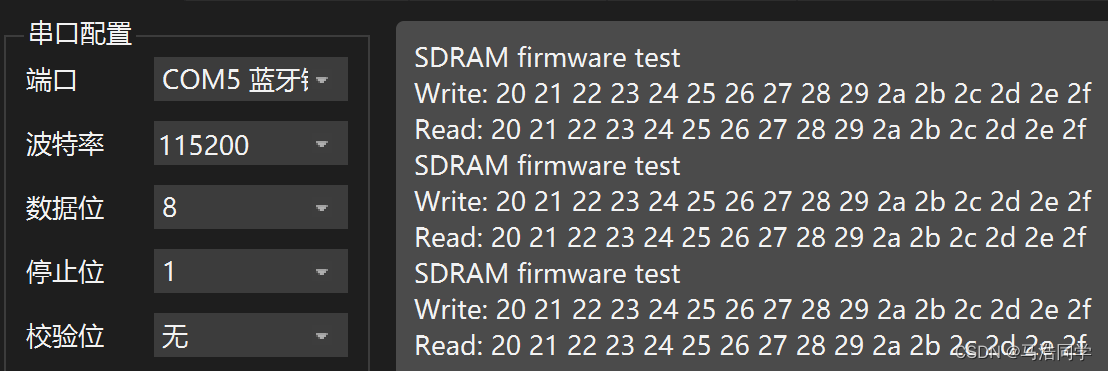

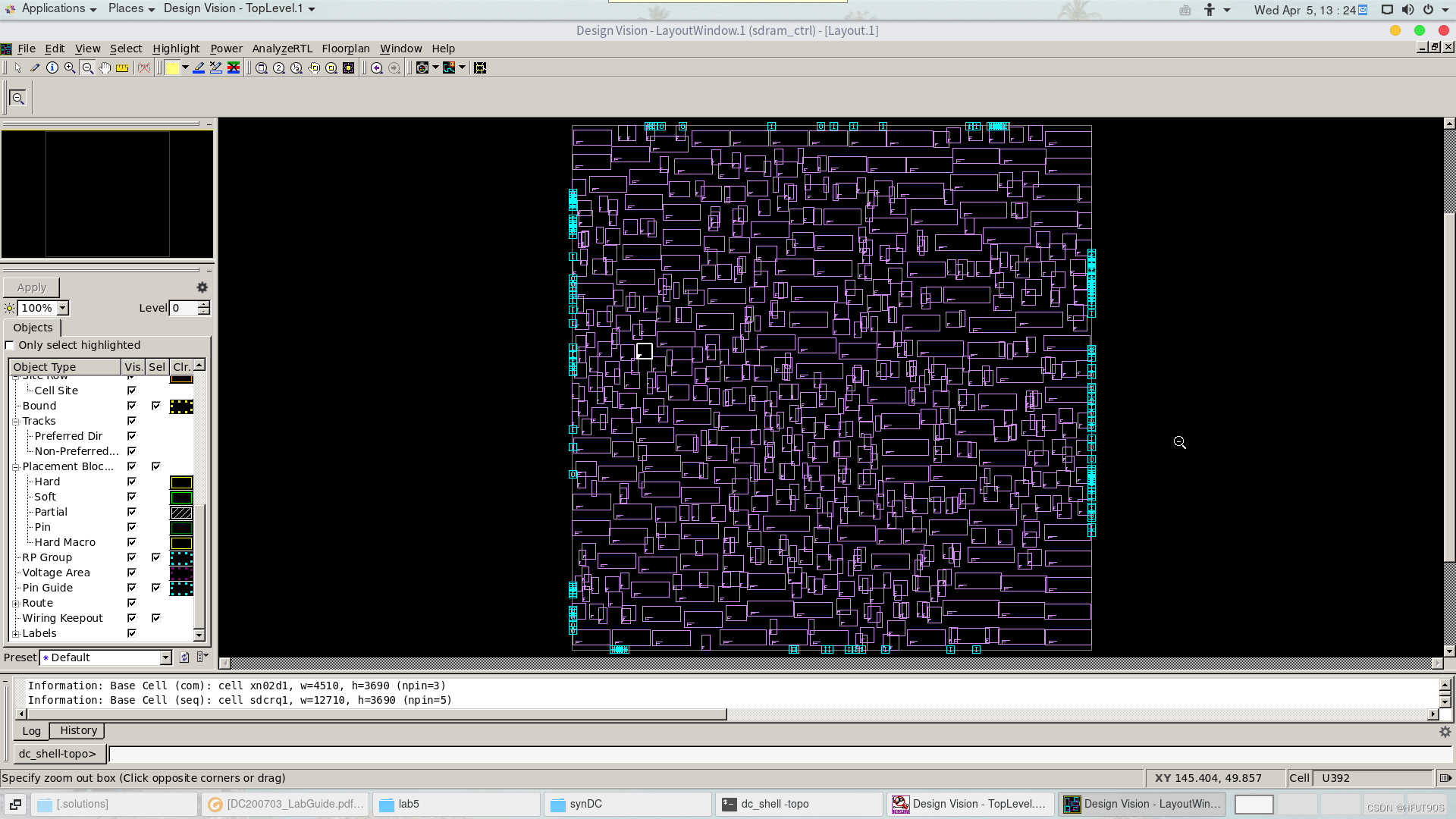

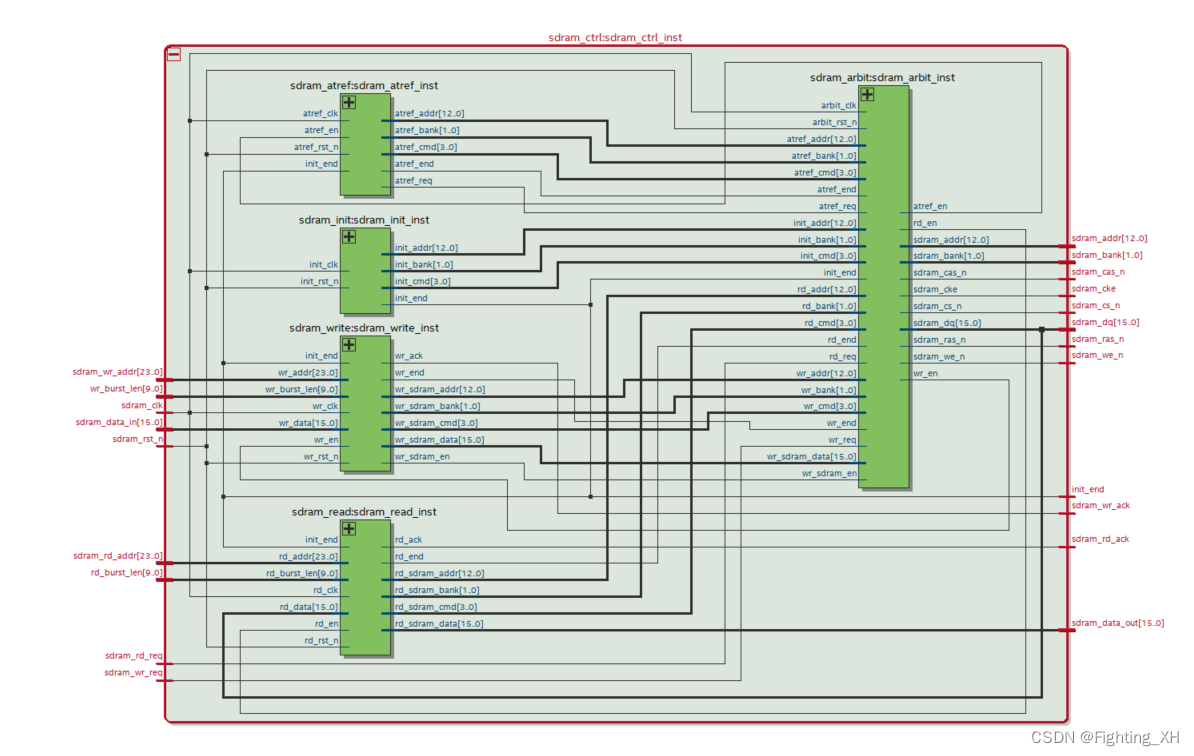

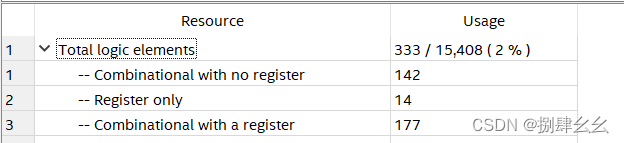

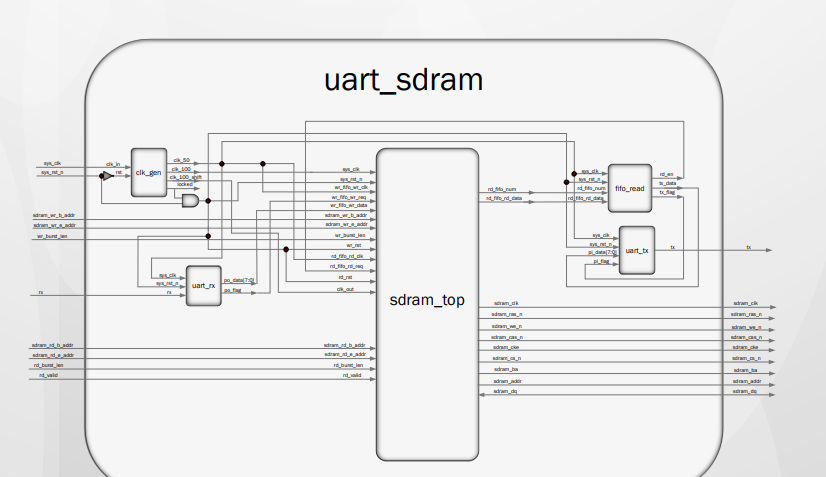

15、驱动

对于软件驱动主要应该做哪些事情呢?

1、按照 SDRAM 的时序,合理的配置驱动的时序信息;

2、发送对应的命令,初始化 SDRAM;

3、访问 SDRAM 的时候,由对应的 decoder 进行地址译码,并且生成相应的时序;

4、根据需要,配置 refresh 的时间间隔;

5、低功耗的时候,进行对应的配置;