软件工程——程序流程图详解

文章目录

- 软件工程——程序流程图详解

- 程序流程图

- 程序流程图的基本控制结构

- 程序流程图实例

- 程序流程图的标准符号(国家标准)

- 循环的标准符号

- 注解符的使用

- 多选择判断

- N-S图

- N-S图的基本控制结构

- N-S图的实例

- N-S图的特点

- N-S图的扩展表示

- PAD图

- PAD的扩充控制结构

- PAD的优点

程序流程图

程序流程图也称为程序框图,是软件开发者最熟悉的算法表达工具。

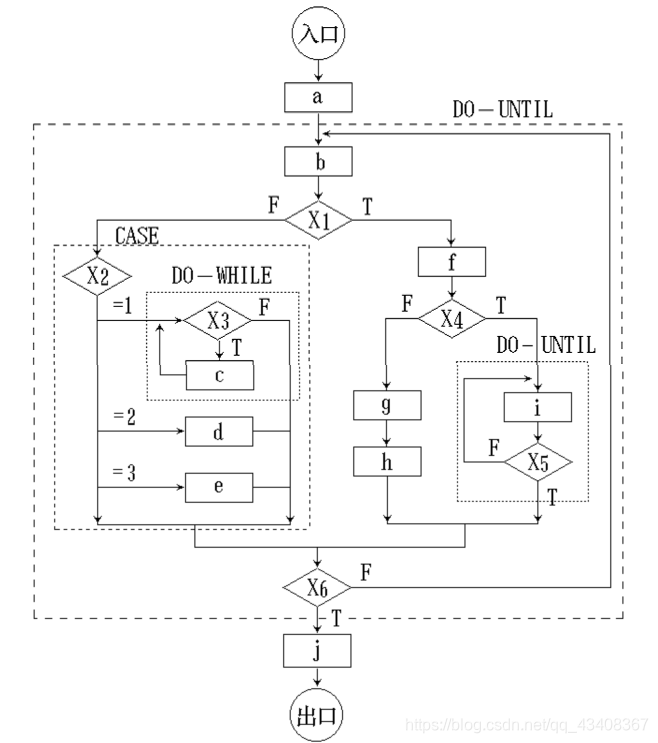

程序流程图的基本控制结构

- 顺序型:几个连续的加工步骤依次排列构成。

- 选择型:由某个逻辑判断式的取值决定选择两个加工中的一个。

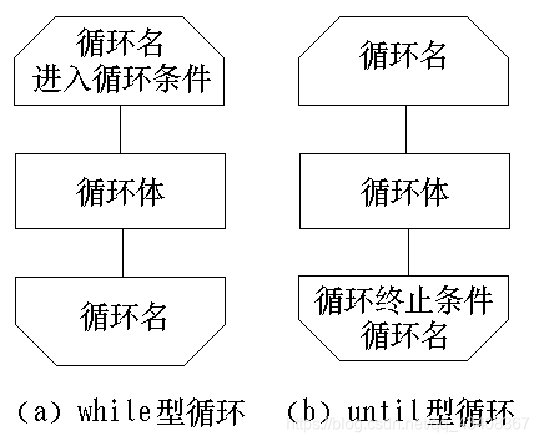

- 先判定(while)型循环:在循环控制条件成立时,重复执行特定的加工。

- 后判定(until)型循环:重复执行某些特定的加工,直至控制条件成立。

- 多情况(case)型选择:列举多种加工情况,根据控制变量的取值,选择执行其一。

程序流程图实例

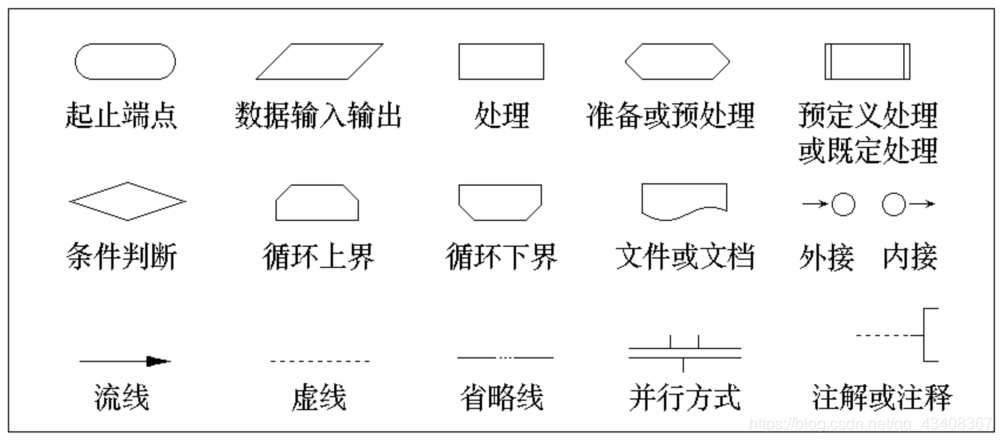

程序流程图的标准符号(国家标准)

循环的标准符号

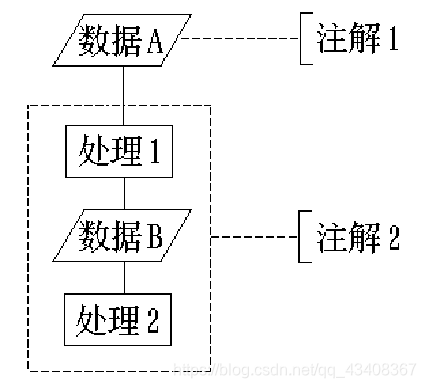

注解符的使用

多选择判断

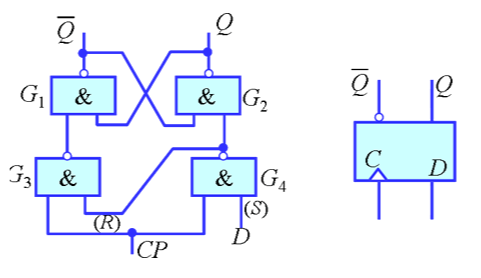

N-S图

Nassi和Shneiderman 提出了一种符合结构化程序设计原则的图形描述工具,叫做盒图 (box-diagram),也叫做N-S图。

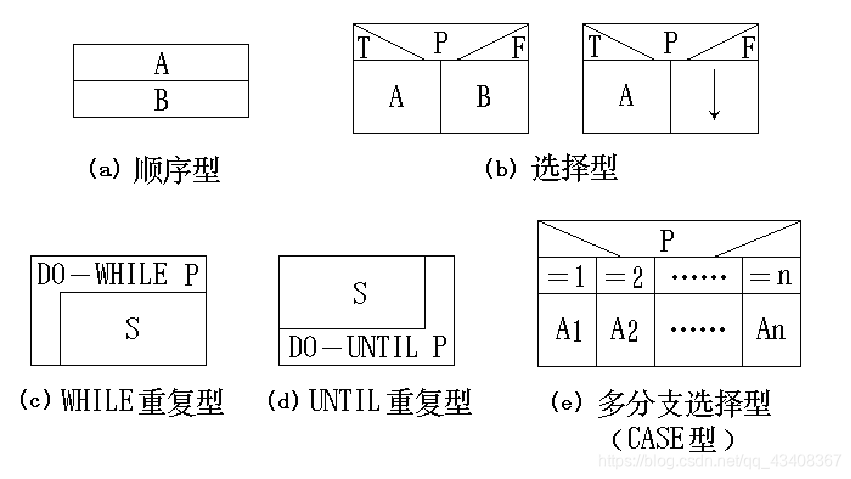

在N-S图中,为了表示5种基本控制结构,规定了5种图形构件。

N-S图的基本控制结构

N-S图的实例

N-S图的特点

- 图中每个矩形框(除CASE构造中表示条件取值的矩形框外)都是明确定义了的功能域(即一个特定控制结构的作用域),以图形表示,清晰可见。

- 它的控制转移不能任意规定,必须遵守结构化程序设计的要求。

- 很容易确定局部数据和(或)全局数据的作用域。

- 很容易表现嵌套关系,也可以表示模块的层次结构。

N-S图的扩展表示

PAD图

PAD(problem analysis diagram)是日本日立公司提出,由程序流程图演化来的,用结构化程序设计思想表现程序逻辑结构的图形工具。

PAD也设置了5种基本控制结构的图式,并允许递归使用。

PAD的扩充控制结构

PAD的优点

- 使用PAD符号所设计出来的程序必然是结构化程序。

- PAD图描绘程序结构清晰,图中竖线的总条数就是程序的层次数。

- 用PAD图表现程序逻辑易读、易懂、易记。

- 容易将PAD图自动转换为高级语言源程序。

- PAD图既可以表示程序逻辑,也可用于描绘数据结构。

- PAD图的符号支持自顶向下、逐步求精方法的使用。