Win装linux双系统教程

1. 准备步骤

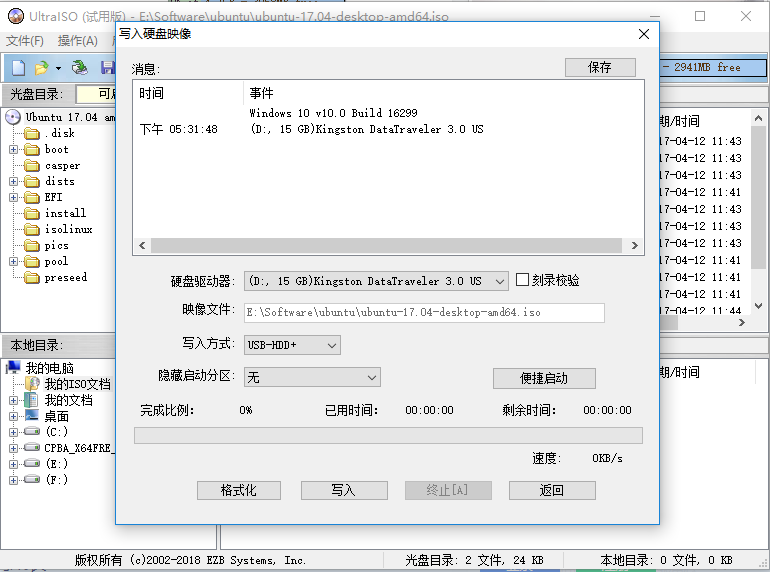

Linux系统镜像、空u盘(16g)、写入软件(一般是UltraISO,其他也行)、引导编辑工具(EasyBCD、easyuefi之类的)

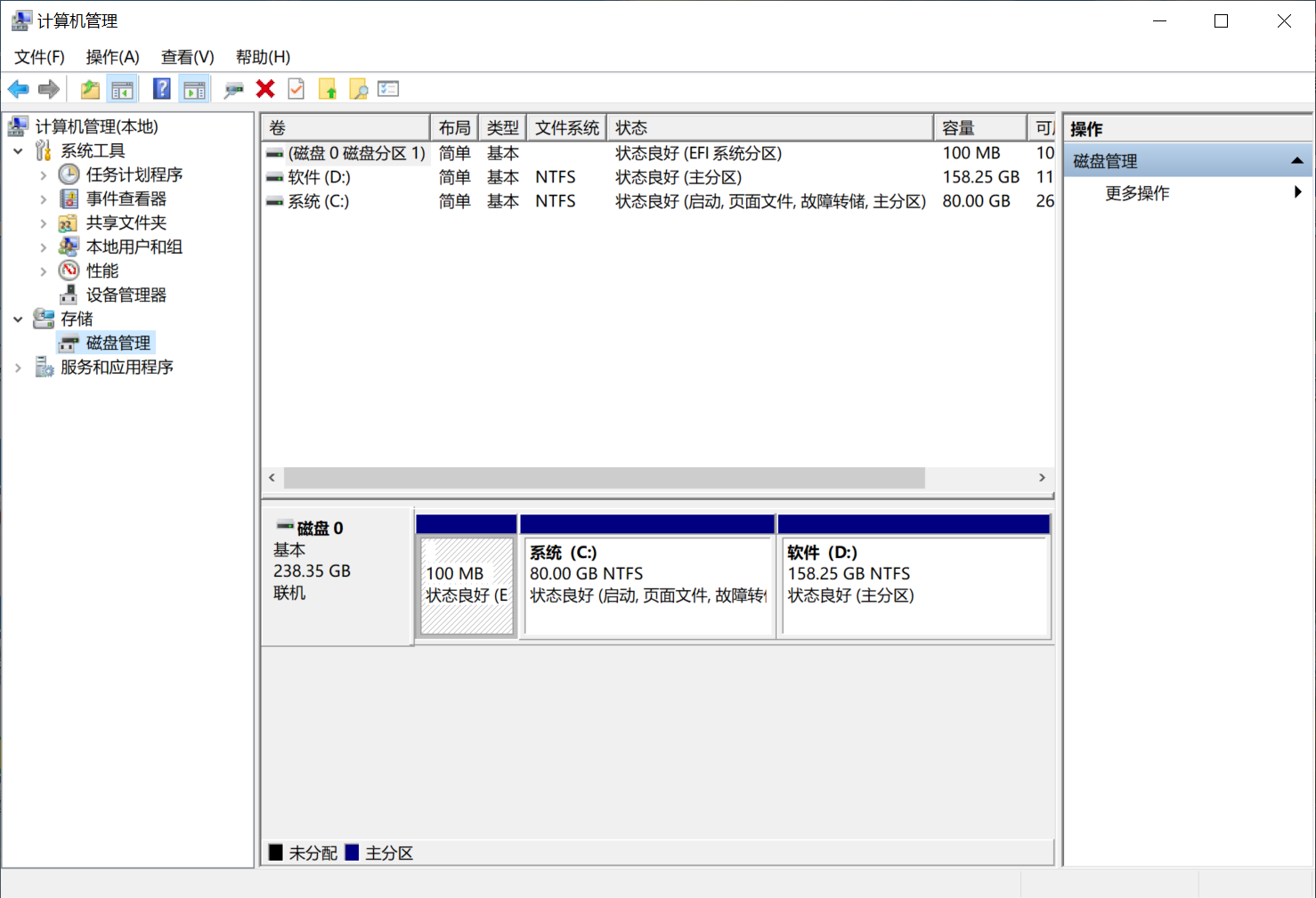

2.释放空间

右键我的电脑-管理-磁盘工具-在想要压缩的磁盘上右键选择“压缩卷”,修改你想要的“输入压缩空间量”,50G以上就够用了。

2. 将linux写入u盘,记得先格式化一次,避免你的u盘不是空u盘,镜像选你的linux镜像,写入的位置选你的u盘。

3. 将电脑设置为u盘启动,可进入bios设置,可高级启动项直接u盘启动。

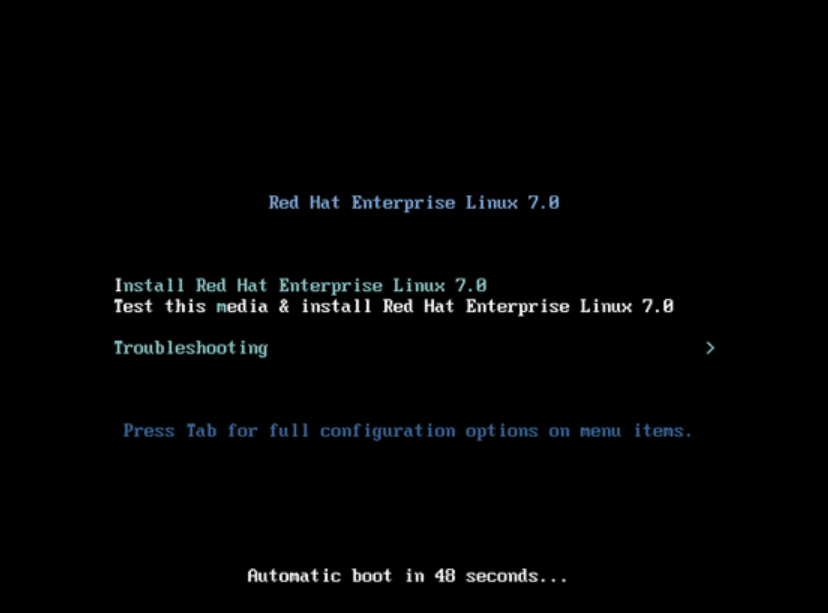

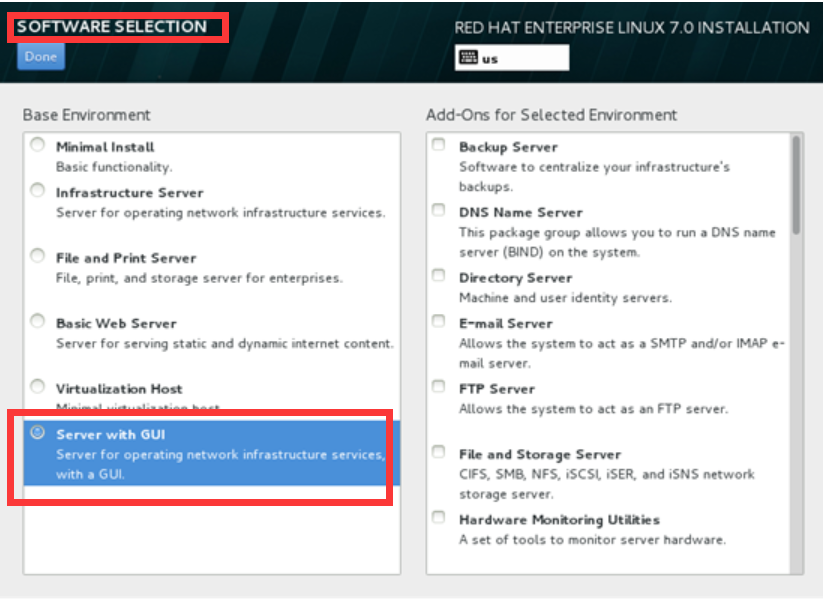

4. 进入linux安装界面(此处以redhat为例),选则Install Red Hat Enterpr ise L inux 7.0

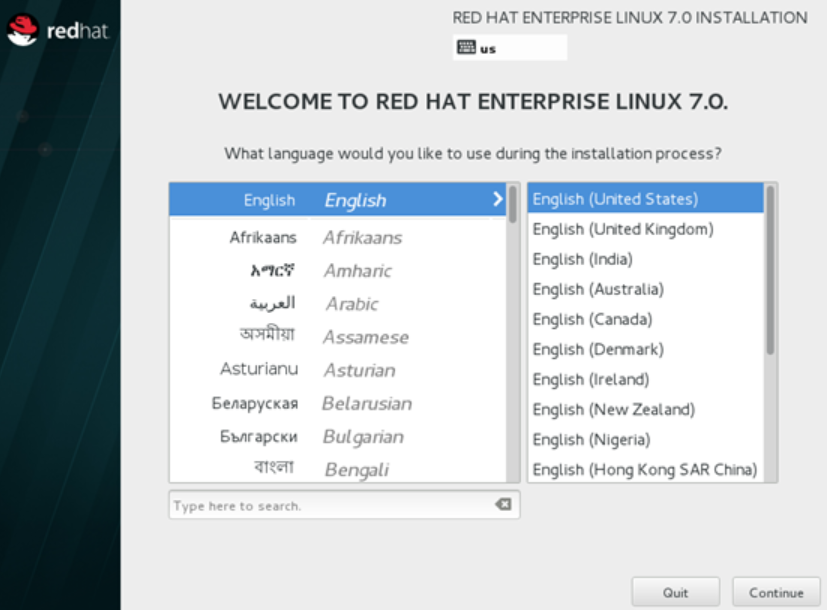

这一步选择语言,选中文,如果你愿意也可以选英文。

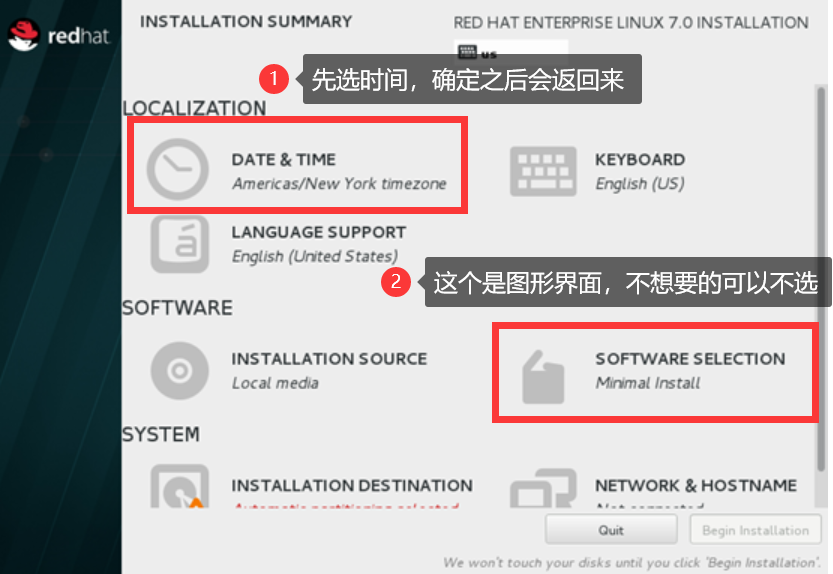

这儿选日期和时间,中文是上海时间,英文是纽约时间

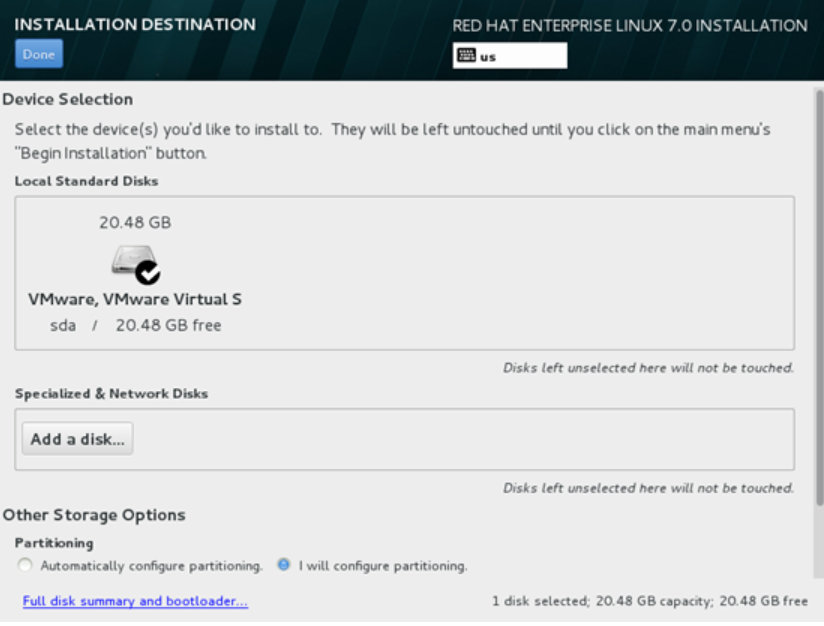

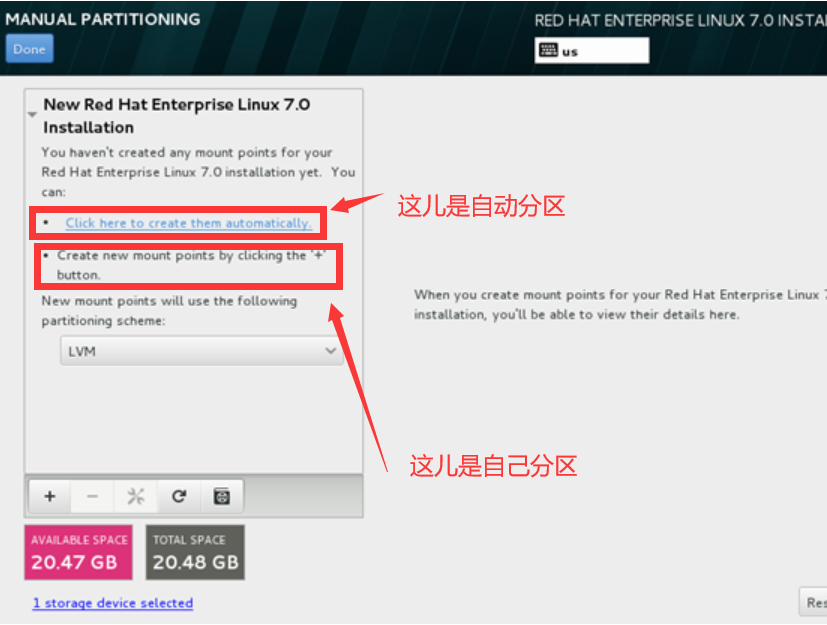

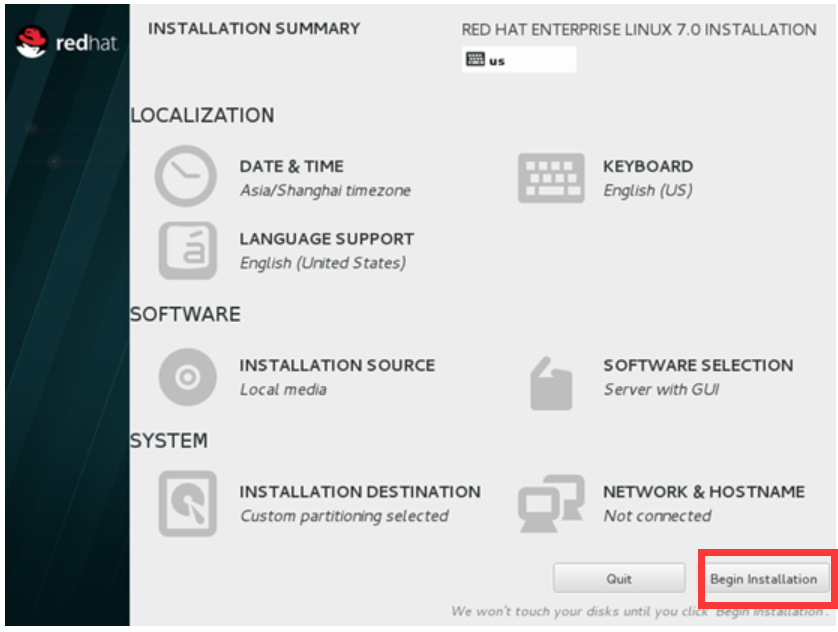

之后点击done回去刚才的界面,选择INSTALLATION DESTINATION,选择你的硬盘,要选那个I will configure partitioning,才是双系统,第一个auto是单系统

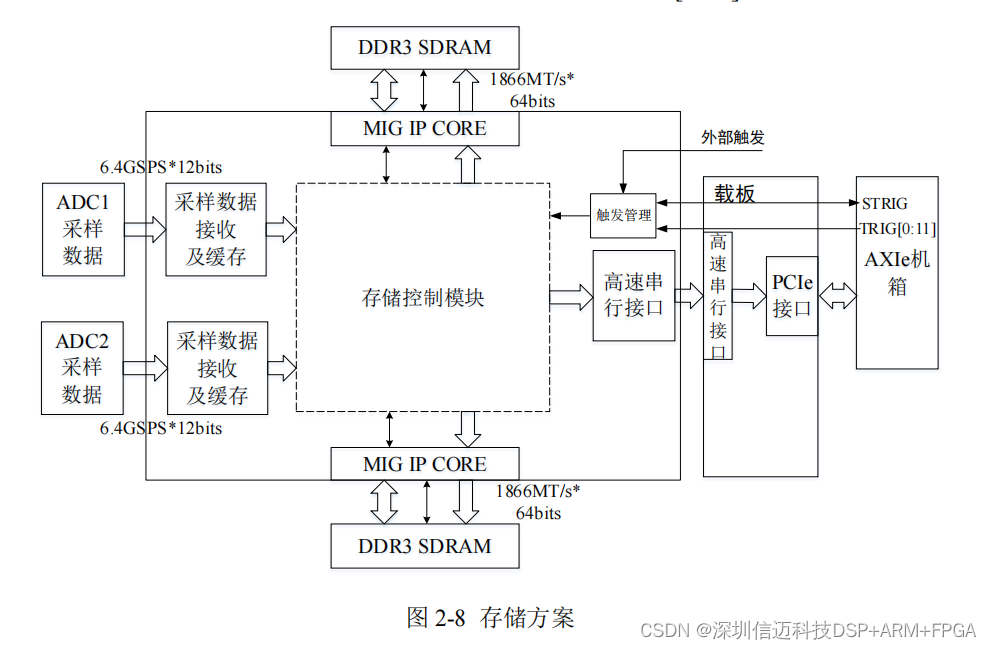

点击done,这里看看这里的盘的大小是不是你释放的空间大小,如果不是,估计是你前面的步骤有问题。

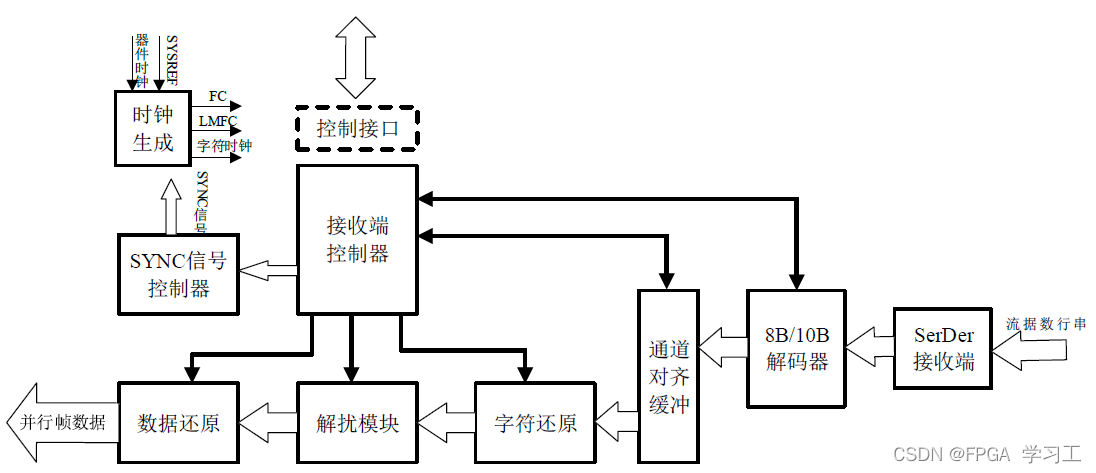

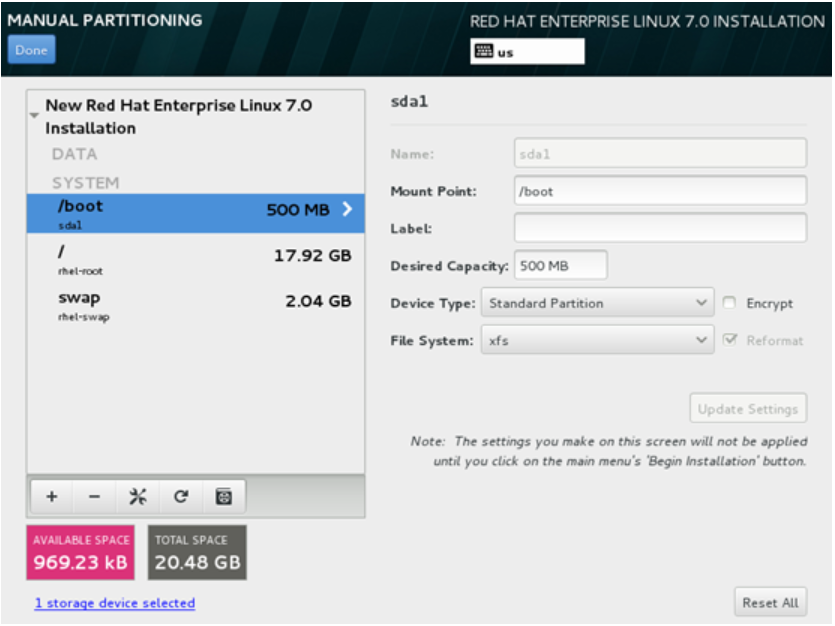

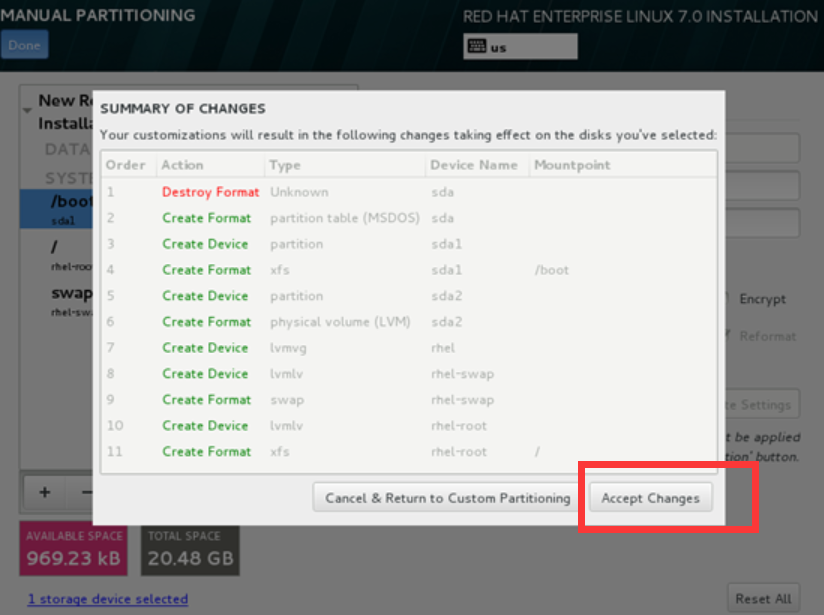

一般分区如下图,容量并不固定,看你开心,根据镜像的不同,有些没有自动分区的可以自己分,ubuntu装的时候可以直接多设一个引导分区,把引导装在里面,这样就不用最后用工具装引导了。点击done继续。

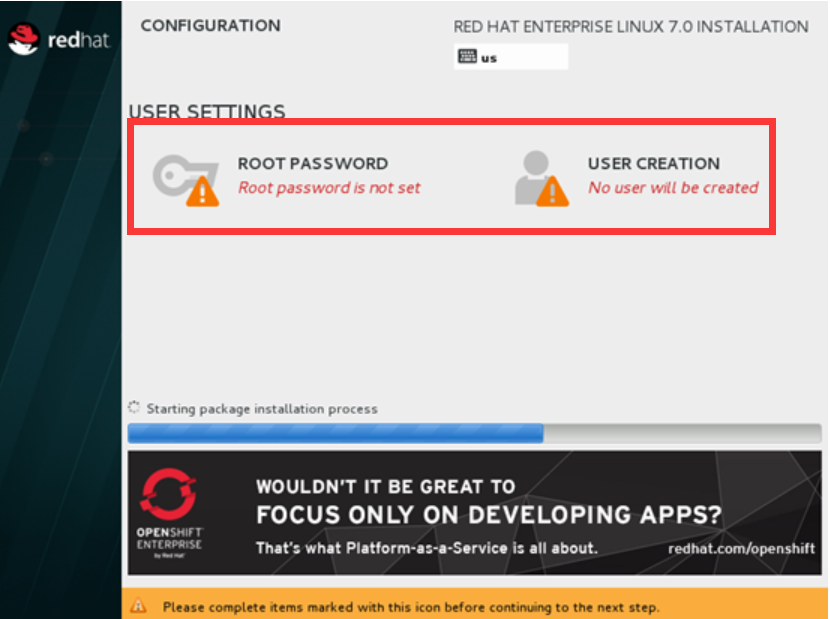

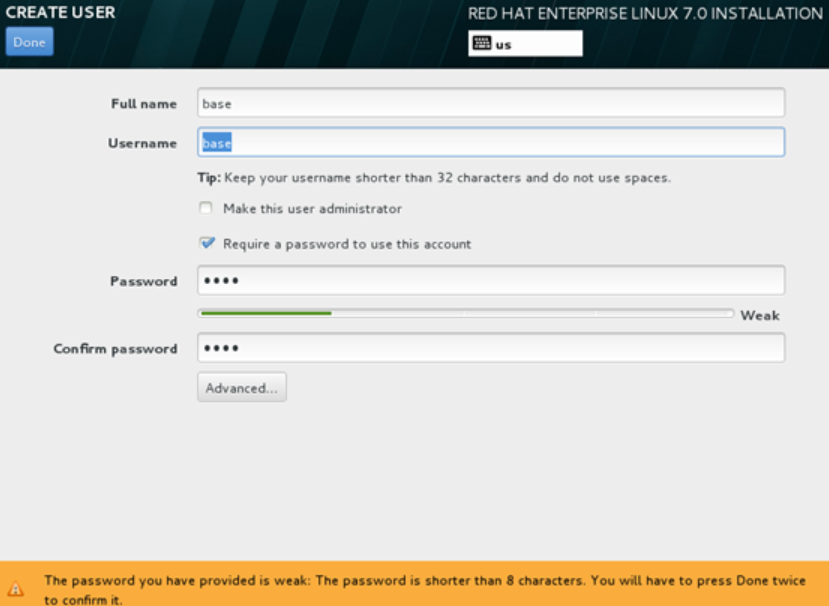

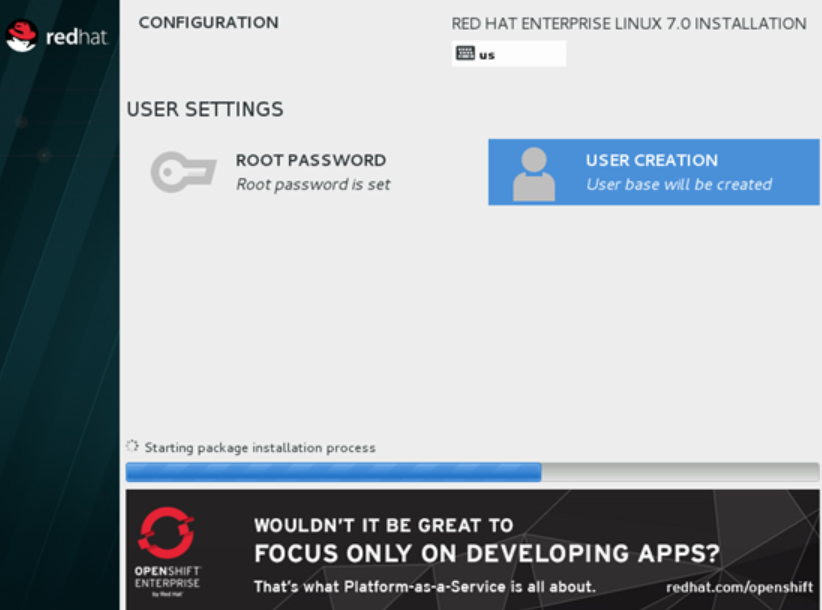

然后是创建账户和密码

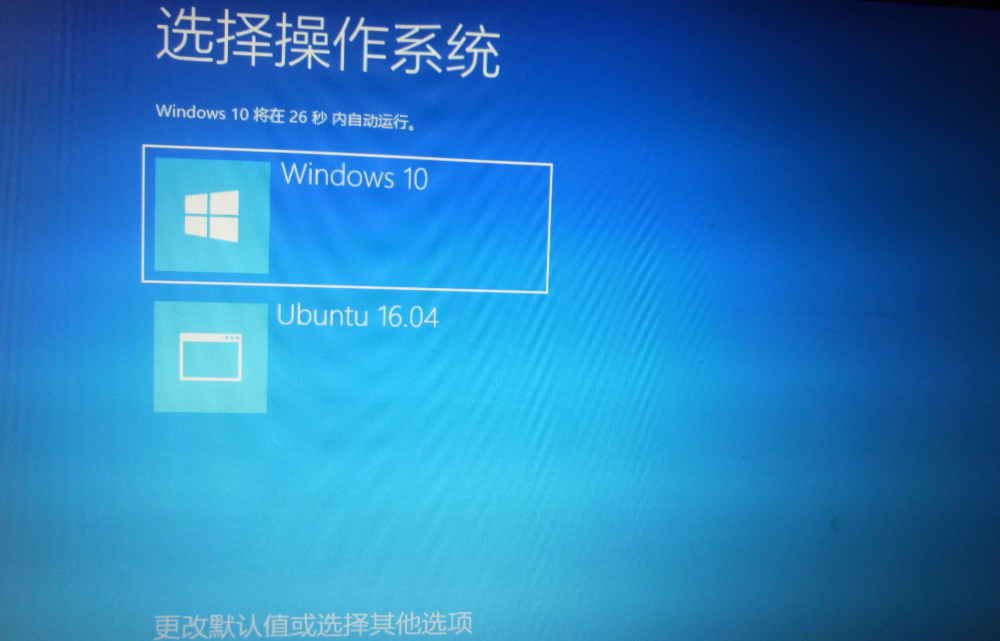

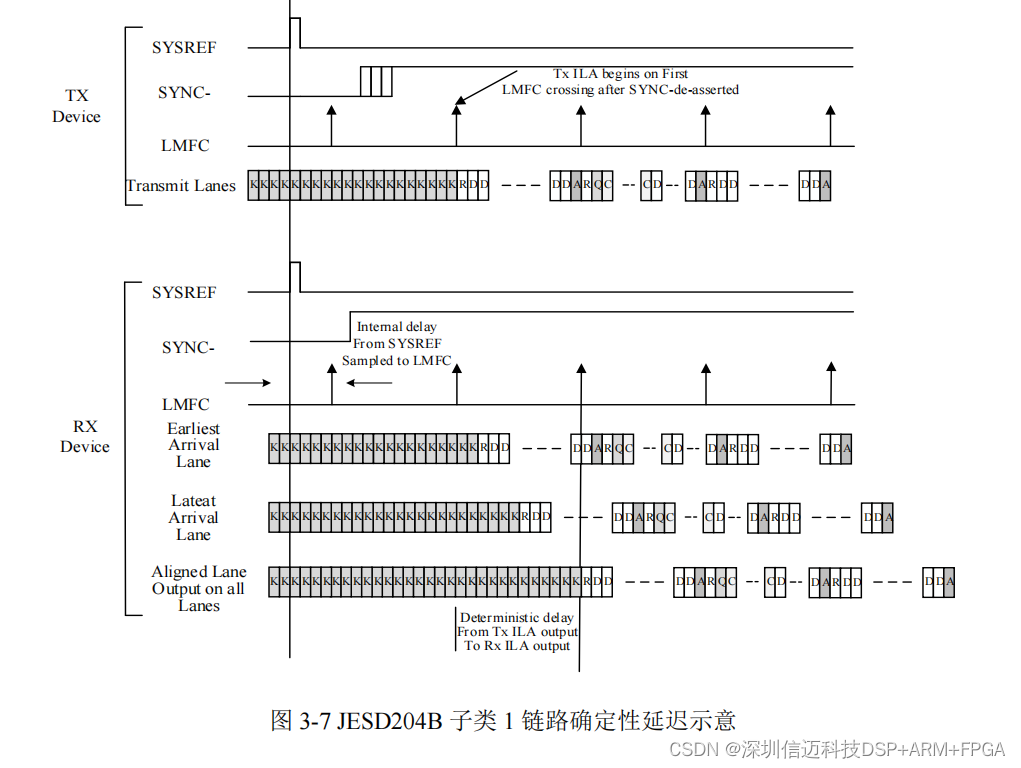

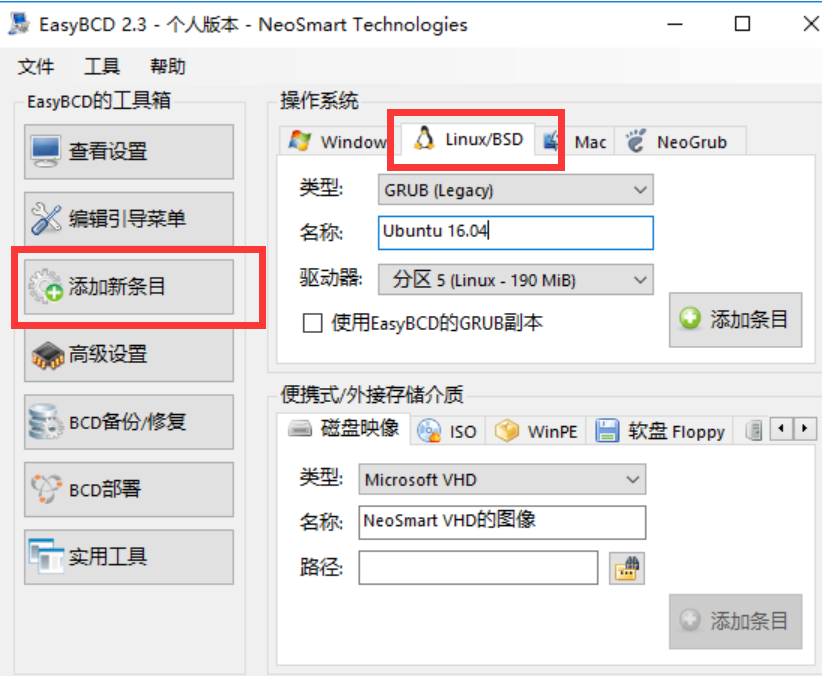

接着就是重启了,之后你开机可能直接是win10,如果你之前建了引导分区,那么你开机就会有两个系统可以选择,这时候进入到win10之后,你可以打开你下载的easybcd或者easyuefi,下图是easybcd,软件不会使用的话百度一下就好,很简单的

至此,大功告成。