基于 JESD204B 的采集与数据接收电路设计

本章将围绕基于 JESD204B 高速数据传输接口的双通道高速数据采集实现展

开。首先,简介 JESD204B 协议、接口结构。然后,研究 JESD204B 链路建立与同

步的过程。其次,研究基于 JESD204B 子类 1 的多器件同步方案。最后,将完成

双通道同步采集与数据接收设计,包括时钟、采集及数据接收设计。

3.1 JESD204B 协议概述

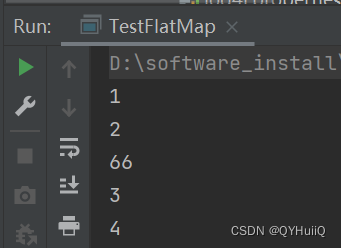

为应对高采样率、高分辨率数据转换器数据吞吐率提高的状况, JEDEC 协会

制定了一种可用于数据转换器与逻辑器件之间的高速串行通信协议—— JESD204 ,

并不断更新、修订该协议。其中 JESD204 系列协议的第二次修订版—— JESD204B

被各大知名器件厂商(如 ADI 、 TI )广泛应用于高速数据转换器。

相较于之前的两个版本, JESD204B 首先提高了数据传输速率,单通道最高传

输速率为 12.5Gbps ;其次链路收发两端不再采用同一时钟(帧时钟),而是采用

设备时钟,即转换器的采样时钟,逻辑器件的参考时钟,通常这两个时钟的频率

不同;最后引入确定性延时,通过在各链路上实现可重复、可编程延时解决多链

路、多通道之间数据不同步的问题。根据是否支持确定性延时及用于实现确定性

延时的时钟种类, JESD204B 可分为子类 0 、子类 1 及子类 2 。其中只有子类 1 及

子类 2 支持确定性延迟。 JESD204B 协议的传输示意如图 3-1 所示。

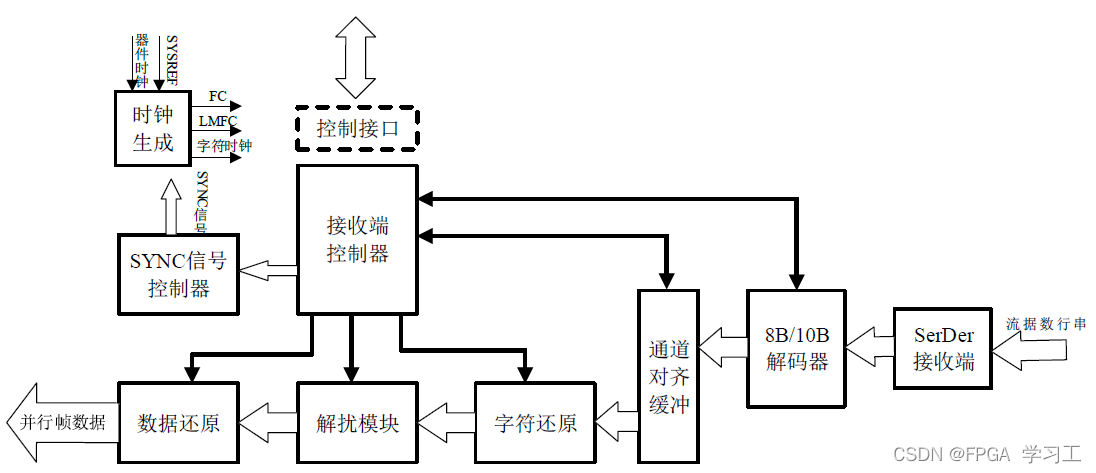

3.2 JESD204B 接口结构

JESD204B 接口由发送端(模数转换器或逻辑设备)接口及接收端(逻辑设备

或数模转换器)接口两部分组成,无论是发送端还是接收端其结构组成一致,都

包括应用层、传输层、数据链路层及物理层 4 个部分。在 JESD204B 协议中并未

定义应用层。但是,常把用于用户设置 JESD204B 链路参数的应用接口称为应用

层。只有发送端与接收端的链路参数一致才能确保 JESD204B 链路正确工作。图

3-2 是 JESD204B 接口结构框图,发送端与接收端之间对应层级在功能上互为逆过

程。

发送端一侧的传输层根据链路参数将数据生成模块的数据映射为字节、帧、

多帧及通道形式 [23] ,链路参数有 L 、 M 、 F 、 S 、 CS 、 N 、 N’ ,其中 L 、 N’ 、 M 、 F

同 2.3.1 小节及 2.3.2 小节表示的意义相同, S 则表示每个帧时钟每个转换器有多少

个采样点, CS 则表示每个转换样本包含多少个控制位, N 表示样点分辨率。接收

端侧的传输层则需要将接收的打包数据按照链路参数及映射方式恢复样点。

链路层负责建立 JESD204B 链路,实现链路同步,主要功能有 8b/10b 编 / 解码,

链路同步、建立及监测。这里主要介绍 8b/10b 编 / 解码,链路同步、建立及监测将

在后面小节介绍。 8b/10b 编码方式能够为交流耦合的串行解串链路提供直流平衡,

避免传输数据出现连续 6 位为 0 或为 1 的情况。故 8b/10b 编码方式能够在数据传

输过程中产生足够数量的边沿跳变,使接收端能可靠地恢复数据时钟。 8b/10b 还

能提供一定的错误检测,当接收端所接收的 10 位字符并不位于 8b/10b 解码器查找

表中时,说明字符中出现数据位错误。

发送端物理层将 8b/10b 编码后的数据串行化并按照通道数据传输速率发送,

接收端物理层则将接收的串行数据并行化并由 8b/10b 解码字节数据。 JESD204B

物理层主要由电流模式逻辑( CML )电平驱动器、预加重器(均衡器)及串行器

(接收端为解串器)构成。发送端采用预加重器补偿信道上由 PCB 材料及信号传

输距离带来的损耗,接收端则采用均衡器校准传输通道的低通响应。接收端的组

成部分还包括时钟检测恢复模块,该模块通过数据传输通道的串行数据流解析出

数据时钟,用于串行数据并行化。

发送端的加扰是一种可选功能,位于传输层及链路层之间。加扰功能对传输

层的 8bits 数据进行加扰,用以消除传输数据中可能存在的频谱尖峰。当发送端选

择使用加扰功能时,接收端则需要对 8b/10b 解码数据进行解扰 [23] 。

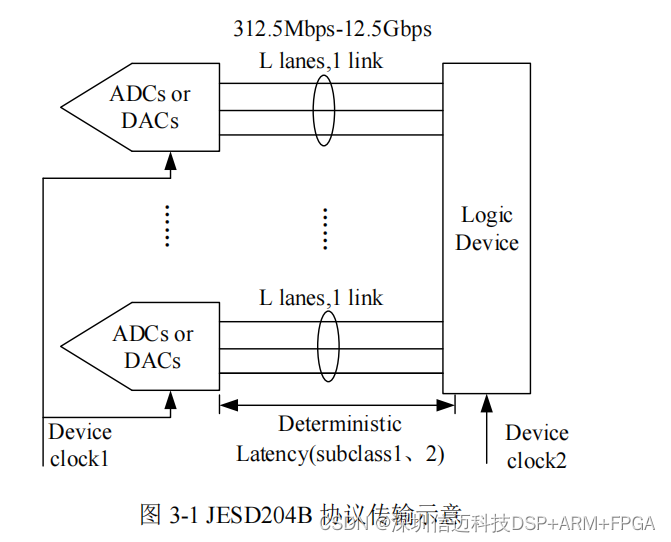

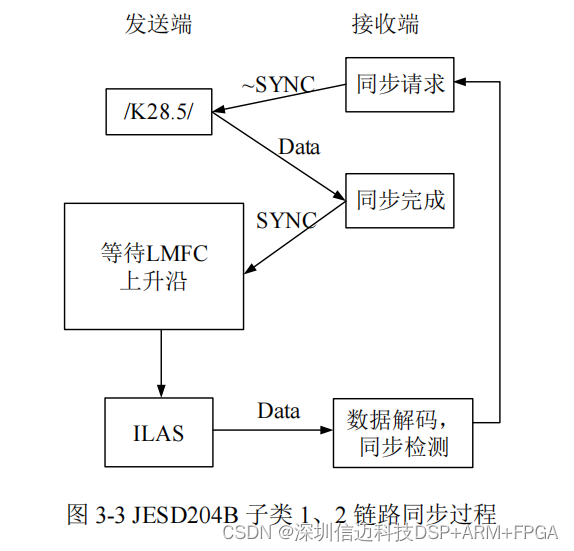

3.3 JESD204B 链路的建立与同步

由前一小节 JESD204B 接口结构可知, JESD204B 链路的建立主要由数据链路

层完成。在正式传输采样数据之前,首先需要经历代码组同步( CGS )阶段,然

后是初始化通道同步(

ILS )阶段 [24] 。初始化帧同步(

IFS )的完成包含在 CGS 及

ILS 阶段中。 JESD204B 各子类链路建立与同步的区别在于代码组同步完成之后以

何种时钟边沿为基准开启初始化通道同步,子类 0 采用帧时钟,子类 1 、 2 采用多

帧时钟。图 3-3 是 JESD204B 子类 1 、 2 链路同步过程示意。

链路同步第一阶段——代码组同步,主要用于检测串行数据流中的关键字符

边界,同步数据流中的字符边界与接收端字节时钟。接收端通过拉低 SYNC 信号

表示同步请求,发送端则通过发送 /K28.5/ (即 /K/ 字符,其十六进制数为 bc )字符

流表示检测到同步信号,接收端将接收并同步数据流。当接收端接收到至少 4 个

连续正确的 /K28.5/ 字符时,接收端将通过拉高 SYNC 信号表示取消同步请求。虽

然 SYNC 拉高,但是发送端仍会发送 /K28.5/ 字符直到发送端的下一个 LMFC 边界

到来时刻,此时代码组同步完成。对于 JESD204B 子类 1 ,在开始代码组同步之前

需要使用 SYSREF 信号指定各设备的帧时钟及多帧时钟边界。

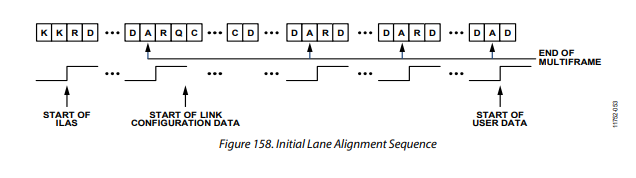

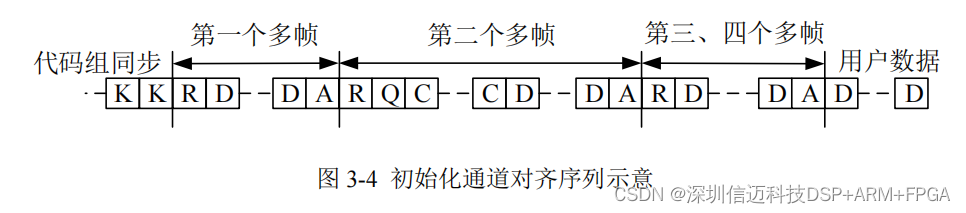

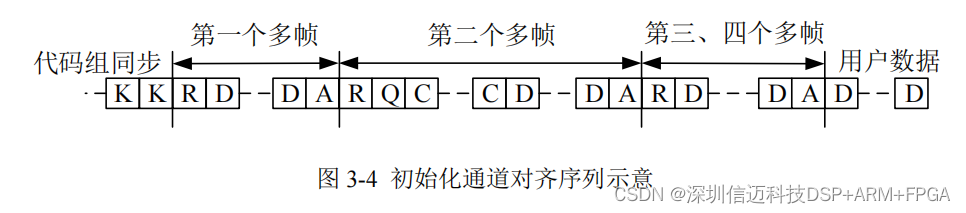

链路同步第二阶段——初始化通道同步,主要用于检测串行数据流的帧边界

及多帧边界,并验证链路参数是否与用户设置一致。初始化通道同步由初始化通

道对齐序列(ILAS)完成,初始化通道对齐序列由多帧构成,根据 JESD204B 不

同子类的工作模式,多帧个数不同, JESD204B 子类 0 可自定义多帧个数,

JESD204B

子类 1 、 2 多帧个数则为 4 个。以子类 1 、 2 为例,初始化通道对齐序列的每个多

帧都以帧开始字符 /K28.0/ (即 /R/ 字符,其十六进制数为 1c )开始,链路同步字符

/K28.3/ (即 /A/ 字符,其十六进制为 7c )结束,特别的,第二个多帧会在开始字符

后跟上一个链路控制数据开始字符 /K28.4/ (即 /Q/ 字符,其十六进制为 9c ),随后

是链路参数具体值(字符 C ),初始化通道对齐序列中未填充位置便使用斜坡数据

(字符 D )进行填充,图 3-4 是初始化通道对齐序列示意。

初始化帧同步存在于 JESD204B 链路建立的各个阶段。代码组同步阶段,发

送端通过发送 /K28.5/ 字符完成帧标识;初始化通道同步阶段,接收端将接收到的

第一个非 /K28.5/ 字符作为一个新帧开始,即图 3-4 中的帧开始字符 /R/ ;接收端还

将根据链路参数 F 估计新帧开始位置。用户数据传输过程中可能会出现帧对齐错

误,为此通过对齐字符 /K28.7/ (即 /F/ 字符,其十六进制为 fc )和 /K28.3/ 字符插入

或替换特定帧,并在接收端验证对齐字符位置方式实现帧对齐监测和纠正。

3.4 基于 JESD204B 的多器件同步

对于多通道采集系统来说,同步指的是多个 ADC 器件同步采样并且采样数据

同步传输,通道之间采样数据的相位差保持稳定。无论是采用 LVDS 并行传输接

口的多 ADC 采集系统,还是基于 JESD204 高速串行接口协议的多 ADC 采集系统

首先都需要保证器件之间的采样时钟相位确定,然后保证采样数据同步传输。基

于 JESD204B 的多器件采集系统为实现数据同步传输,不仅同 LVDS 并行传输接

口一样采取数据走线匹配方式,而且还引入了两种同步方法:一种是时间戳,一

种是确定性延迟。在实际应用中,最常采用的是第二种方式,即通过实现确定性

延迟完成多器件同步 [25-26] 。

3.4.1 确定性延迟原理

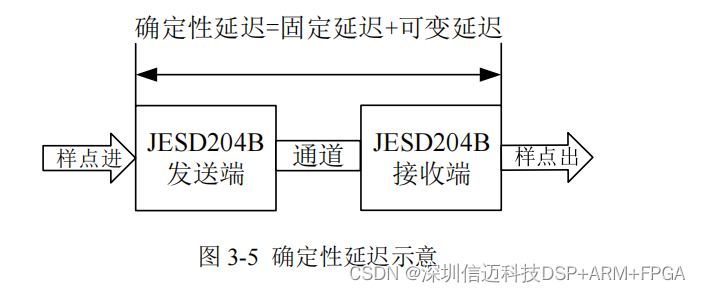

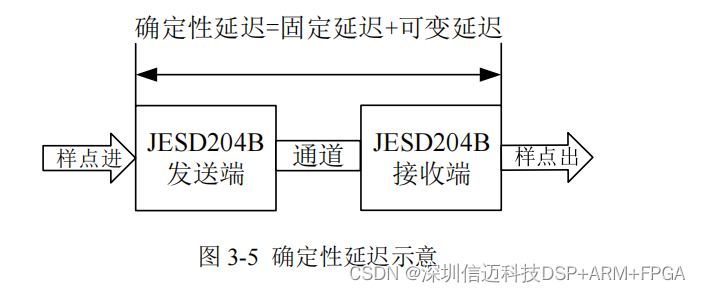

通常要求基于 JESD204B 的多通道采集系统具有数据延迟在不同上电周期或

重新建立链路时可重复的特性。 JESD204B 标准将确定性延迟定义为样本以帧结构

进入串行发送器与样本以帧结构从串行接收器输出的时间差 [27] ,如图 3-5 所示。

确定性延迟包括固定延迟和可变延迟两部分。可变延迟由 JESD204B 协议定

义的多个用于数据传输及处理的时钟在每次上电或重新建立链路时相位关系不确

定引起。 JESD204B 子类 0 虽然不需要借助外部电路就可以实现单链路多通道对齐,

但是其在不同上电周期或重新建立链路时链路延迟无法固定,不适用于多链路需

要同步的情况。 JESD204B 子类 1 、子类 2 则通过确定性延迟实现多链路同步,发

送端需使所有通道在某一“确定时刻”同时发送初始化通道对齐序列,接收端各

通道对应的接收缓冲器需在某一“确定时刻”同时释放所有通道数据。无论是发

送端的“确定时刻”还是接收端的“确定时刻”计数单位都是帧时钟。发送端的

“确定时刻”可以是 SYNC 拉高后的第一个多帧边沿,也可以编程为 SYNC 信号

上升之后的几个多帧边沿。接收端的“确定时刻”指多帧边界后的几个可编程帧

周期( RBD , RX Buffer Delay ),可编程帧周期取值范围为 1 至 K 。为确保接收缓

冲器在释放所有通道的数据之前,各通道的数据已全部到达,所有通道中最大延

迟必须小于本地多帧周期, RBD 值与帧周期乘积必须大于数据通道中可能的最大

延迟。

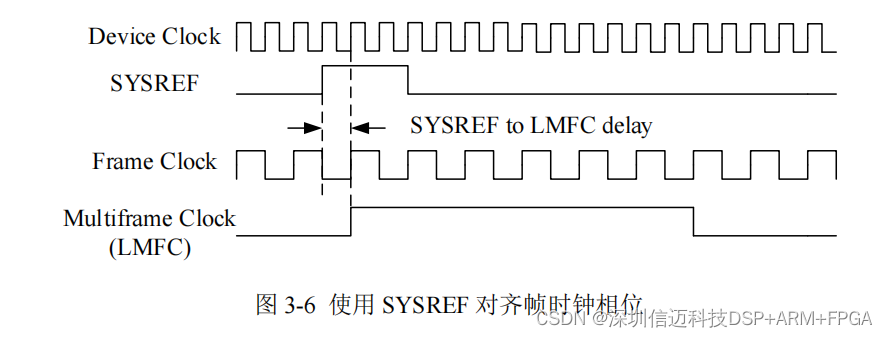

3.4.2 SYSREF 设计

上述确定性延迟要求提及的初始化通道对齐序列发送和接收缓冲器释放时刻

与发送端和接收端中的帧时钟、多帧时钟有关。发送端、接收端的帧时钟、多帧

时钟相位对齐是实现确定性延迟的关键。

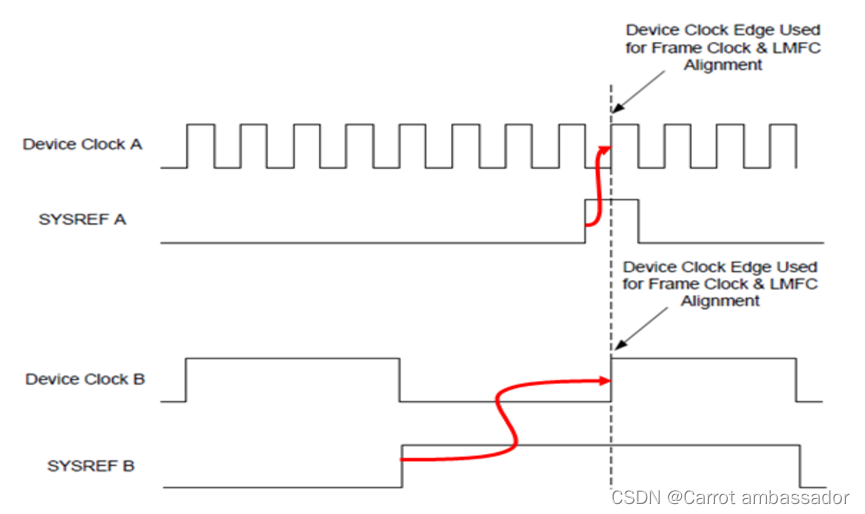

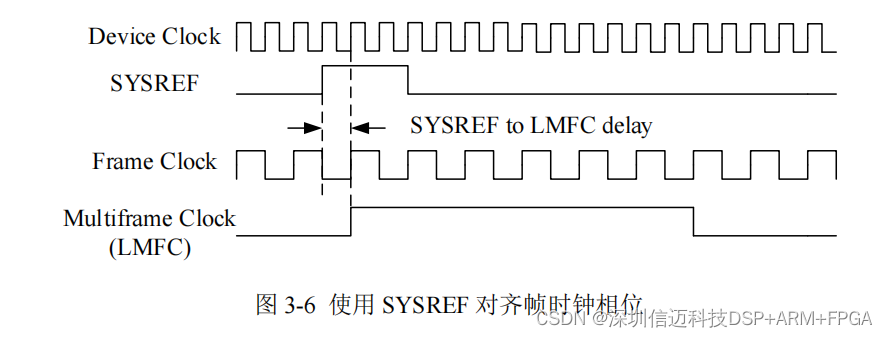

JESD204B 子类 1 采用 SYSREF 对齐系统

中各器件之间的帧时钟、多帧时钟相位,如图 3-6 所示 [28] 。

随着转换器件采样率的提升, SYSREF 相对于器件时钟的建立及保持定时变得

极具挑战,尤其采样率达千兆的器件。本文采用的 ADC12DJ3200 采样率高达

6.4GSPS ,为应对 SYSREF 的建立保持窗口减小的情况,该款 ADC 通过在单通道

模式下使用双边沿采样将输入时钟(器件时钟)频率减小一半的方式达到将

SYSREF 建立保持窗口增加一倍的效果。除了降低输入时钟频率的方式以外,该

ADC 还提供了 SYSREF 窗口以及 SYSREF 自动校准两种功能。通过 SYSREF 窗口

检测 SYSREF 位置(相对于器件时钟)和 SYSREF 采样位置选择辅助用户设计以

满足各种情况下的建立保持时间需求。 SYSREF 自动校准相较于 SYSREF 窗口功

能更易操作,使用孔径时间调整模块基于 SYSREF 相位移动 ADC 采样序列,而不

是基于 ADC 采样序列调整 SYSREF 相位。

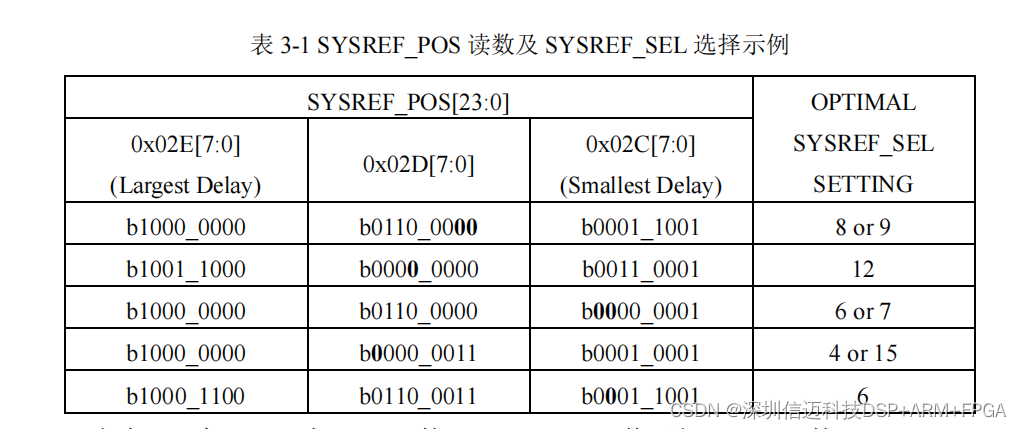

SYSREF 窗口功能需按照一定过程实现 [29] 。首先,需给 ADC 芯片提供采样时

钟及 SYSREF 。 SYSREF 捕捉模块使用 SYSREF 窗口确定 SYSREF 相对于设备时

钟的位置,并将该位置值存储在 SYSREF 位置寄存器( SYSREF_POS )中。

SYSREF_POS 寄存器的每一位都代表一个潜在的 SYSREF 采样位置。当

SYSREF_POS 中的某一位被置位,那么相应的 SYSREF 采样位置有潜在的建立或

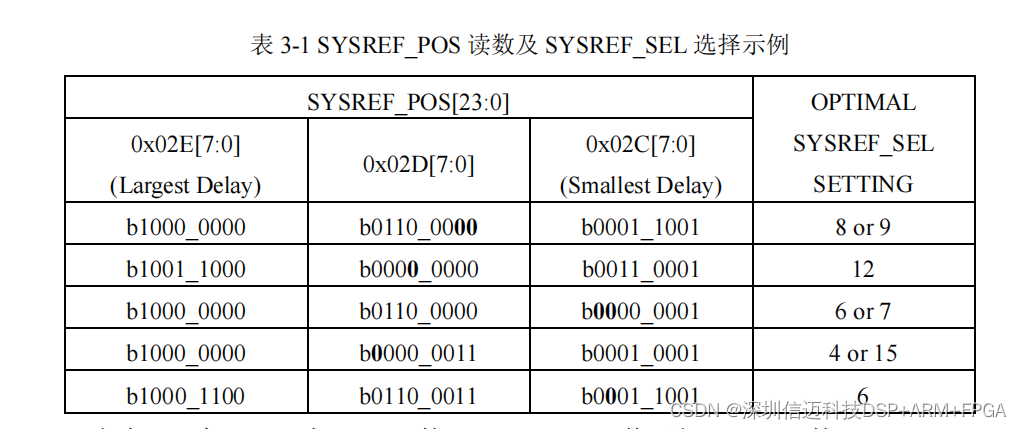

保持违例。然后,根据 SYSREF_POS 寄存器 值 在 SYSREF 选择寄存器

(SYSREF_SEL)中设置与 SYSREF_POS 相对应的有效采样位置。该采样位置通

常位于两个建立和保持时间都满足的采样位置的中间。 SYREF_SEL 的取值范围为

为 0 至 15 ,即 SYSREF 窗口功能仅支持将 SYSREF 设置在前 16 个采样位置。根

据 SYSREF_POS 数值选择 SYSREF_SEL 位置的示例如表 3-1 ,加粗部分表示可以

选择的位置。 SYSREF_POS 采样位置步进可以通过 SYSREF 放大寄存器

( SYSREF_ZOOM )调节。当 SYSREF_POS 的 0 至 23 位都为 1 时需要将

SYSREF_ZOOM 设置为 0 ,其他时候都将该值设置为 1 。

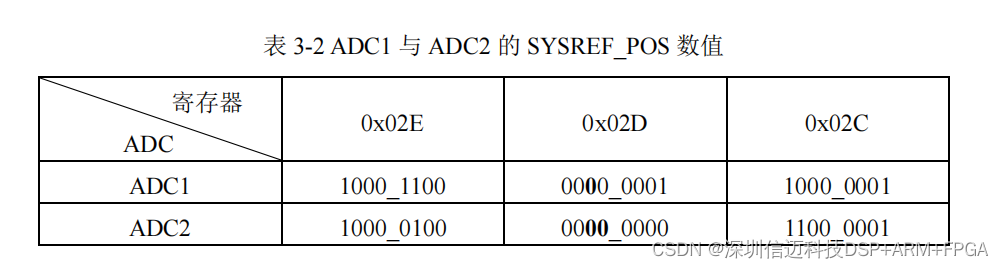

根据上文,为本文采集模块选择满足建立和保持时间的最佳 SYSREF 位置。

将 SYSREF_ZOOM 设置为 1 ,关闭 SYSREF 自动校正功能,然后读取 SYSREF_POS

值。

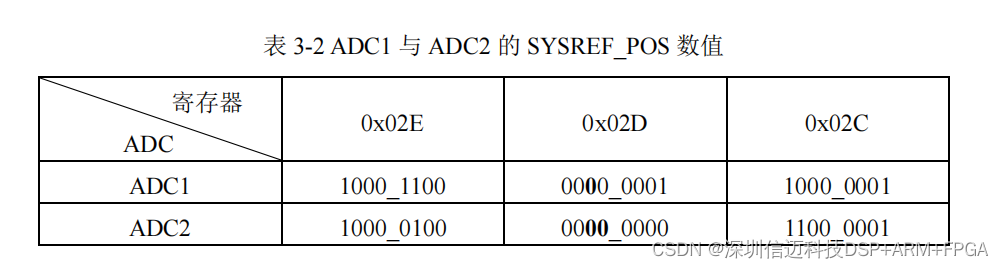

由表 3-2 中 ADC1 与 ADC2 的 SYSREF_POS 值可知,

ADC1 的 SYSREF_SEL

设置为 13 可以满足建立保持时间,而 ADC2 的 SYSREF_SEL 设置为 12 或 13 都

能够满足建立保持时间,故可将两个 ADC 的 SYSREF_SEL 的值都设置为 13 。

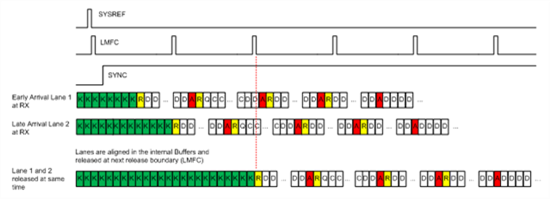

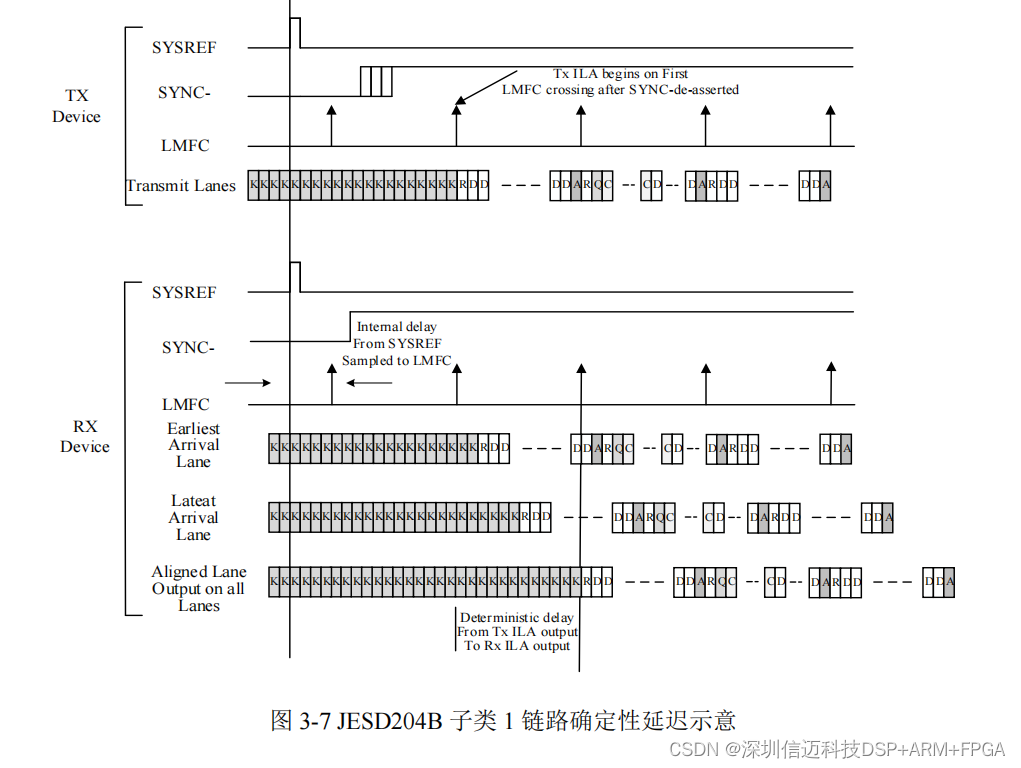

3.4.3 基于确定性延迟的多器件同步

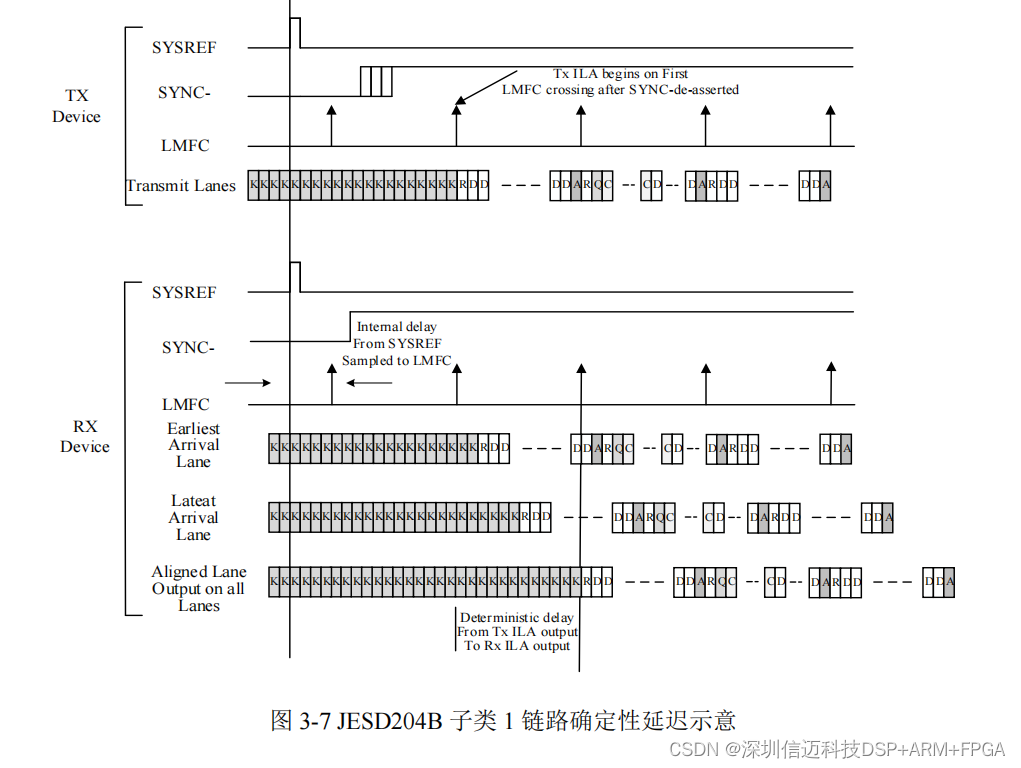

JESD204B 子类 1 实现链路确定性延迟的过程如图 3-7 所示 [30] 。首先 SYSREF

指定发送端及接收端的本地多帧时钟边界,发送端在 SYNC 信号拉低后开启链路

建立、同步过程,接收端各通道的接收缓冲器缓存有效数据,在接收端所有通道

都接收到有效数据之后,才在其下一个本地多帧边界同时释放所有缓存数据。此

时所有数据通道的数据延迟恰好为一个本地多帧周期,即 RBD 取 K 值,且延迟是

确定、可重复的。当然缓存在接收缓冲器的各通道有效数据也可以在下一个本地

多帧边界之前释放,即 RBD 的值小于 K ,其中最小 RBD 取值对应的延迟称为最

小确定性延迟。

JESD204B IP 核将 0x030 寄存器( RBD )定义为接收端缓冲器延迟,

并为每一个数据通道定义了缓冲调整寄存器( Buffer Adjust )用于指示接收缓冲器

的填充水平。在所有数据通道中找出缓冲调整寄存器最小值,并将该值赋值给 RBD

便可实现最小确定性延迟。

上述 RBD 值调整基于数据通道最大延迟满足小于一个多帧的要求,实际数据

通道的最大延迟可能并不满足此要求。不仅如此,链路还可能出现两个通道的有

效数据分别落在两个相邻本地多帧内的情况。

信迈提供高速数据采集方案。