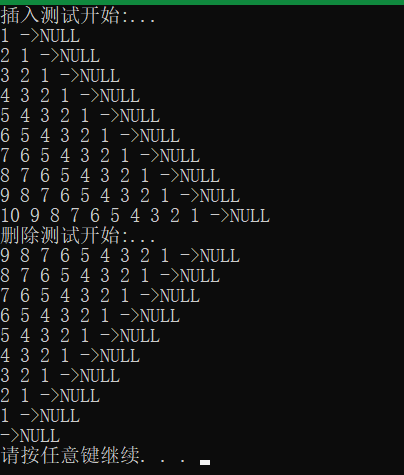

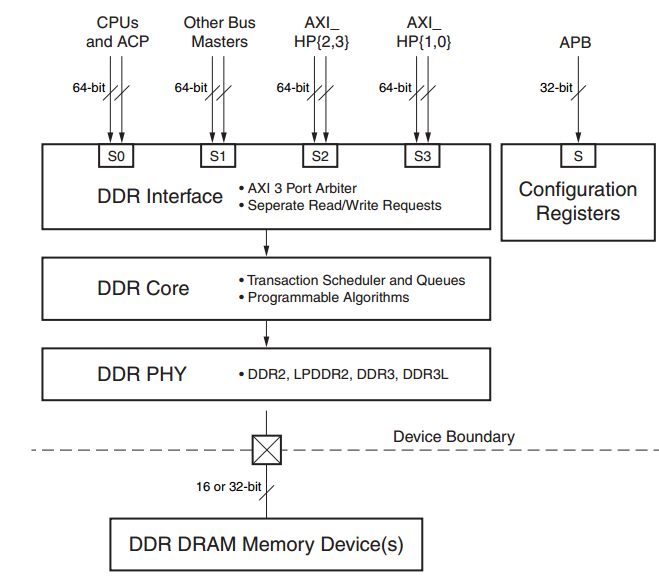

CPU执行指令得到4个地址的数据,对于CPU,1个地址对应的数据是1字节。

(例1)

CPU要读4字节数据,但是nor flash是以16位数据来访问的,一次只能提供2字节,那怎么办?谁来处理这个问题? —-由内存控制器,内存控制器要发起2次传输,

第1次发送0地址,nor flash得到0地址,返回2字节;

第2次发出地址2,nor flash得到1地址,返回2字节;

内存控制器把得到的4字节返回给CPU。

所以说,我们需要设置内存控制器,让它知道:当CPU想得到4个字节数据时,内存控制器要发出2次操作。

需要设置[位宽和等待控制寄存器BWSCON。

为什么要设置位宽?原因就在这里。

为什么CPU发出的地址要错开1位? 原因也在这里。

(例2)

对于S3C2440,写代码时Nor flash的位宽不用设置,由硬件来设置。