Memory Population Guidelines for Intel 3rd Gen Xeon Scalable Processors

英特尔的第三代至强可扩展处理器采用全新的内存控制器架构。本文将深入探讨这些更改,以及如何通过确保正确排序和填充内存模块来最大限度地提高性能。

英特尔的第三代至强可扩展处理器于 2021 年 4 月 6 日推出,其全新的架构带来了许多优势。由于这里需要新的配置和方法,我们将借此机会深入研究这些变化,本文将重点介绍新的内存控制器和 DIMM,以确保平衡配置和性能。在我们介绍新的第三代至强可扩展处理器之前,让我们回顾一下第二代至强可扩展处理器如何处理内存。

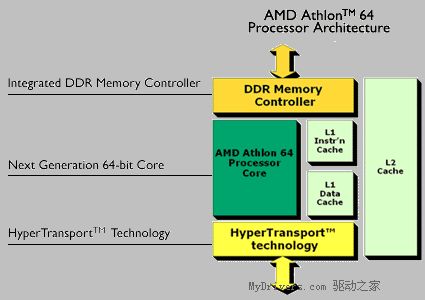

The 2nd Generation Skylake architecture

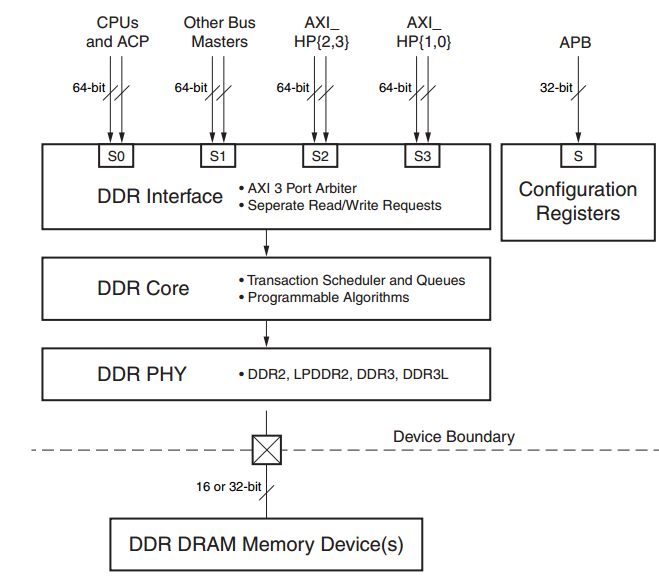

英特尔推出的第二代至强可扩展处理器,配备2个内存控制器,每个控制器管理3个内存通道。每个通道可以接受通道中的 2 个 DIMM。

处理器可以支持的 DIMM 总数 = 将控制器数乘以通道数 * 每个通道的 DIMM 数。

对于第二代至强,这相当于单个处理器可以寻址的总共 12 个 DIMM。

此内存控制器以 DDR4-2933 速度运行,每个通道填充 1 个 DIMM。当每通道填充2个DIMM或傲腾持久内存模块时,速度降低到DDR4-2666。

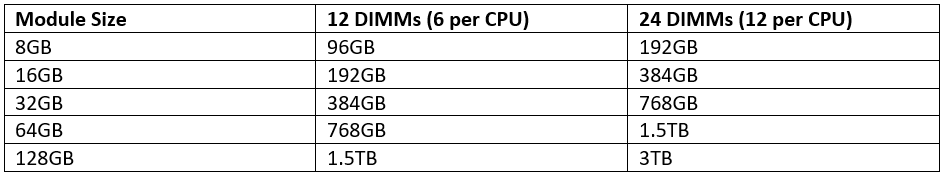

最大化内存带宽的最佳配置在每个通道中填充相同数量的相同模块。双插槽服务器具有多达 24 个 DIMM,允许两种最高性能配置:

如本表所示,有效地利用6个通道可以获得总内存数。由于交错,每个通道具有 2 个 DIMM 的配置将看到有效带宽略有增加。(交错是 CPU 在通道上的内存模块之间平衡请求以减少读写延迟的影响。)应该注意的是,对于需要总共1TB内存的用例,存在具有16个DIMM的服务器,但由于配置不平衡,有效内存带宽减少了34%。

The 3rd Generation Ice Lake architecture

第三代至强可扩展处理器采用全新的内存控制器设计。每个处理器现在有4个内存控制器,每个控制器有两个通道。每个通道可以填充两个 DIMM。第三代至强可以全性能地处理每个处理器总共 16 个 DIMM。

8个通道中的每一个都以 DDR4-3200 运行。 这与每个通道的 DIMM 数量或是否安装了 200 系列傲腾持久内存无关。 还对内存调度程序进行了改进,降低了有效内存延迟,同时增加了整体带宽。

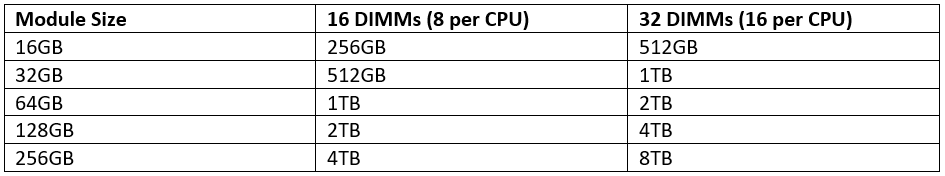

与第二代 Xeon Scalable 相比,这种新设计使整体内存容量增加了 2.6 倍,内存增加了 1.5 倍,而不会增加本地或远程套接字层的读取延迟。 双插槽服务器最多可配备 32 个 DIMM,我们仍有两种平衡的内存配置可供选择,以实现最佳性能:

表 2:Icelake 最大性能配置

Intel 第三代 Xeon Scalable 允许在不牺牲内存带宽的情况下进行更大容量的内存配置。 与前几代一样,在规划服务器内存时应遵循一些基本注意事项:

- 内存模块必须具有相同的规格。 每个 DIMM 必须具有相同的大小、速度和等级。

- 通道相同地填充有一个或两个 DIMM。

- 服务器中的每个 CPU 插槽必须具有相同的内存布局。

以安全为中心的体系结构

也就是说,提高性能只是的一部分。无论使用案例如何,安全性都是当今每个IT组织的首要关注点。英特尔抓住了这一新设计提供的机会,将高级安全功能直接嵌入到 CPU 中。全内存加密 (TME) 可加密整个系统内存,以增强对物理攻击的保护,而软件防护扩展 (SGX) 则通过内存中的应用程序隔离提供细粒度的数据保护,包含在所有第三代至强 SKU 中。这些新功能将在以后的文章中深入介绍,但重要的是要注意,SGX 需要平衡的内存配置。

在ATC体验Ice lake

服务器越来越需要以更短的时间范围处理更多数据,并在创建数据的地方创建数据。这种需求推动了对直接连接到处理器的大量高性能 DRAM 和持久内存的需求。英特尔第三代至强可扩展处理器专为适应要求苛刻的用例而构建,而不会牺牲性能或安全性。

这些处理器现已在DellEMC PowerEdge 15G、HPE ProLiant Gen10 Plus和Cisco UCS M6系列服务器中推出,其他产品线即将更新。WWT很高兴在我们的ATC中展示这项技术,我们几乎可以适应任何用例或工作负载。我们邀请您在ATC中看到它们的实际应用,或参加专门的研讨会以了解更多信息。